<頭條>微電子所面向5納米及以下節點新型負電容FinFET器件取得重要進展_風聞

huohuo-揭露事物本质,观点犀利,远超某些大V及智库-2019-05-23 19:32

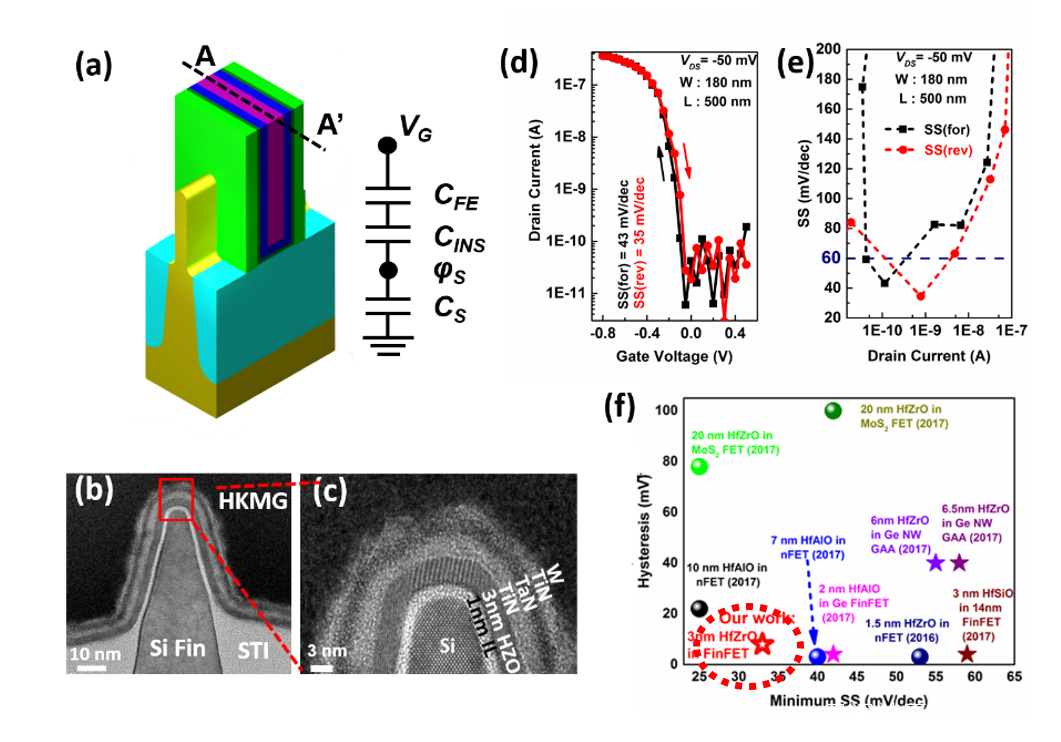

2019-05-13 近日,微電子所集成電路先導工藝研發中心,面向5納米及以下節點高性能和低功耗晶體管性能需求,基於主流後高K金屬柵(HKMG-last)三維FinFET器件集成技術,成功研製出高性能的負電容FinFET器件。

現有硅基晶體管受玻爾茲曼熱力學限制,室温下亞閾值擺幅SS≥60mV/dec,阻礙了工作電壓的繼續降低。當集成電路技術進入5納米及以下節點,隨着集成度的持續增加,在維持器件性能的同時面臨功耗急劇增加的嚴重挑戰。先導中心殷華湘研究員的團隊在主流後HKMG FinFET集成工藝的基礎上,通過材料工藝優化和多柵器件電容匹配設計,結合高質量低界面態的3納米鉿鋯金屬氧化物薄膜,研製成功性能優異的NC-FinFET器件,實現了SS和閾值電壓回滯分別為34.5mV/dec和9mV的500納米柵長NC-FinFET器件,以及SS和閾值電壓回滯分別為53mV/dec和40mV的20納米柵長NC-FinFET器件。其中,500納米柵長NC-FinFET器件的驅動電流比常規HfO2基FinFET器件(非NC-FinFET)提升了260%且電流開關比(Ion/Ioff)大於1x106,標誌着微電子所在新型NC-FinFET器件的研製方面取得了重要進展。

上述最新研究結果發表在國際微電子器件領域的頂級期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2019.2891364),並迅速受到國際多家研發機構的高度關注。

該項集成電路先導工藝的創新研究得到國家科技重大專項02專項和國家重點研發計劃等項目的資助。

“負電容”晶體管:

電容,即電荷的存儲量,一般為正值。然而,如果在晶體管柵極中加入鐵電材料,就會產生負的電容值。這是因為,在某一臨界電壓下,鐵電體的極化方向會發生反轉,這會導致材料表面束縛電荷的巨大積累瞬間超過電源的電極供給。此時,如在電極和外電源間放一電阻,就可看出電壓在下降,但電荷仍然在增加,結果導致出現電容為負值的現象。利用負電容操控晶體管所產生的功耗非常低。應用這種新型晶體管的電子設備的續航能力將會大大提升。