華為昇騰910芯片架構細節流出…

轉自快科技

在昨天開幕的行業頂級活動、第31屆Hot Chips大會上,華為也作為主角之一參加,與AMD、Intel、ARM等巨頭一道介紹自家在芯片方面的最新成果。

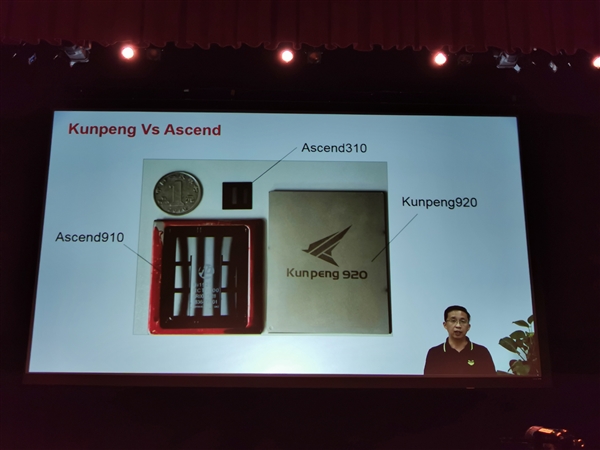

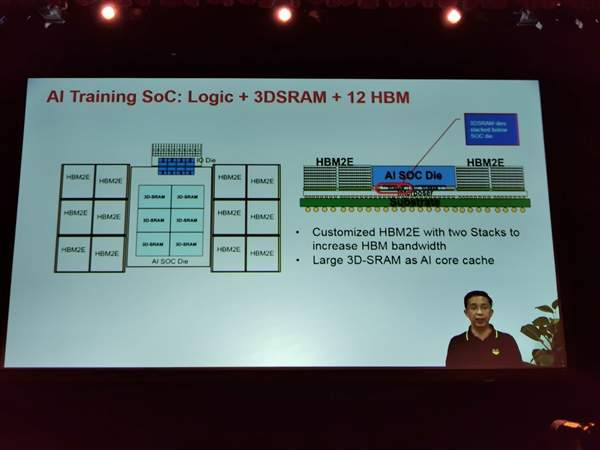

華為此次活動的主題是AI芯片所用的“Da Vinci(達芬奇)”架構,成品是去年發佈的昇騰310(Ascend 310)、昇騰910芯片和麒麟810芯片,另外,AI訓練芯片已經應用上了HBM2E內存,即HBM2增強版,SK海力士產品的陣腳傳輸速率高達3.6Gbps。

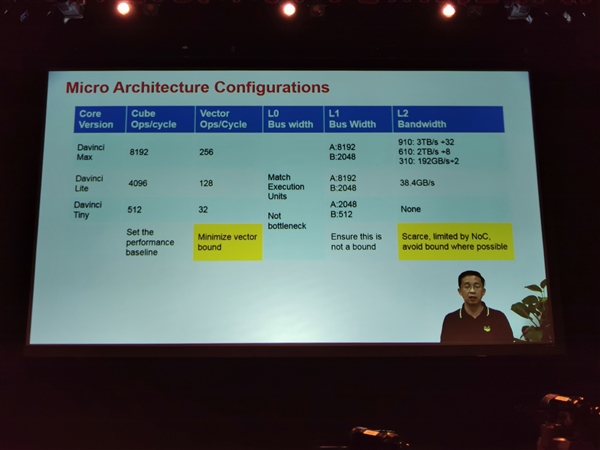

華為達芬奇核心分為三種,最完整的是“Max”,其次是Lite,再次是Tiny,Max可在一個週期內完成8192次MAC運算,Tiny僅512次。

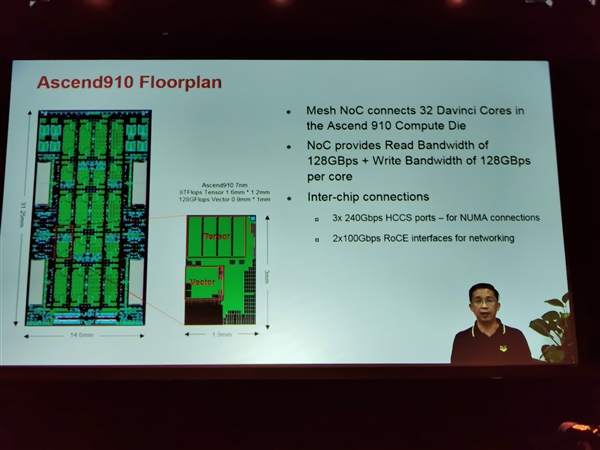

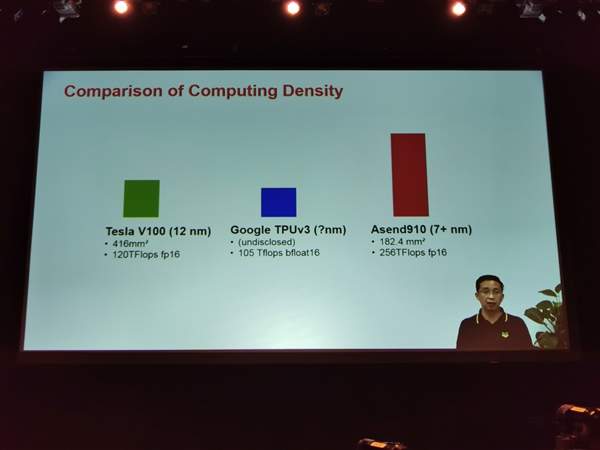

具體到昇騰AI芯片上,310基於12nm工藝,半精度8TFOPs,910基於7nm增強版EUV工藝,單Die內建32顆達芬奇核心,半精度高達256TFOPs,同樣功耗也有350W。

昇騰910 的運算密度超越了精品NVIDIA Tesla V100和谷歌TPU v3,華為還設計了擁有2048個節點的AI運算服務器,整體性能多達512 Peta Flops(2048 x 256)。