清華團隊入選芯片頂會MICRO最佳論文提名,新算法性能超英特爾8倍

本文轉自微信公號“芯潮”(ID:aichip001) 文 | 心緣

芯潮10月17日消息,今日,清華大學微電子所魏少軍、劉雷波團隊獲計算機體系結構頂級會議MICRO最佳論文提名!該團隊提出新型併發控制算法,能將事務內存系統性能提升至英特爾處理器內置TSX指令集的8倍以上。

這是亞洲高校及科研機構在MICRO 52年歷史上第二次獲得最佳論文提名,論文的第一作者是李兆石博士,通訊作者是劉雷波教授。

智東西第一時間聯繫採訪了劉雷波教授, 他告訴智東西,在主流的英特爾至強系列處理器中,TSX (Transactional Synchronization Extension, 事務同步擴展)指令集就是基於本文在研究的事務內存模型的。本文的研究成果可以解決現有英特爾處理器中TSX指令級的實現中,為了確保高併發場景下事務同步的正確性帶來的性能代價過大的問題。

他表示,本研究提出的算法對硬件平台無限制,也可以以專用邏輯設計的方法,集成到現有的處理器設計中。

除這篇論文外,另有五篇論文獲最佳論文提名。最終,《Simba:基於多芯片模塊架構的擴展深度學習推理(Simba:Scaling Deep-Learning Inference with Multi-Chip-Module-Based Architecture)》和《STT:對投機訪問數據的全面保護(Speculative Taint Tracking (STT): A Comprehensive Protection for Speculatively Accessed Data)》獲得最佳論文。

01 解決現有事務內存的性能和訪問撤銷痛點

國際微架構大會MICRO(International Symposium on Microarchitecture),是計算機體系結構領域的重要會議,與ISCA、HPCA、ASPLOS並列計算機體系結構四大頂級會議,論文錄取率通常在21%左右。

神經網絡加速器、專用加速器結構、DRAM、持久性內存、GPU加速器、近內存加速器等,都在MICRO上被首次提出。

第52屆國際微架構會議MICRO在美國俄亥俄州哥倫布市舉辦。會議期間,清華大學魏少軍教授、劉雷波教授團隊在會上做了題為《應用於事務內存的樂觀併發控制算法的FPGA加速(FPGA-Accelerated Optimistic Concurrency Control for Transactional Memory)》的報告。

▲清華大學李兆石博士在MICRO 2019上作報告

劉海波教授還通俗地介紹了該算法和應用意義,事務內存模型將多筆內存的讀寫請求打包成一個事務。事務內存系統將各個事務獨立地(Isolation)、整體地(Atomicity)進行處理。因為事務內存為並行程序開發提供了一種高層次的同步方法,所以它被廣泛用於幫助程序員表達並行性、設計併發數據結構、確保非揮發內存(non-volatile memory)的數據持久性(Durability)等應用下。

事務內存(TM)被認為是解決現有多任務並行時線程間同步問題的一種有前景的替代方法,在編程社區和體系結構社區中都吸引了廣泛的關注,而現有同步操作常常是釋放應用程序並行性的最大絆腳石。

清華團隊發現現有事務內存系統在高併發場景下,由於判斷算法的簡化和不精確,引起許多不必要的訪問撤銷,導致性能受限。

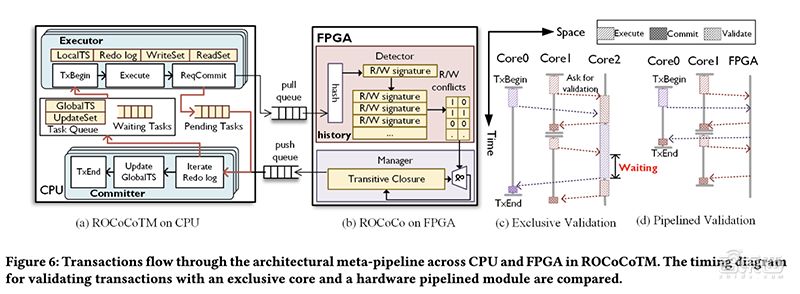

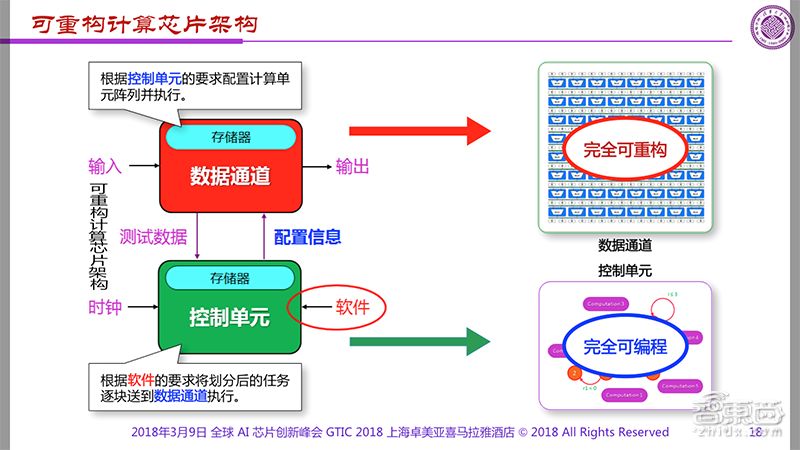

為了解決上述缺陷,該研究團隊利用數學的序關係理論分析了常見的事務內存一致性模型,然後為了解決上述固有缺陷,降低訪問撤銷率及性能開銷,研究團隊設計了立足於並行編程使用的事務內存方法(ROCoCoTM),並利用可重構架構的空間計算特性加速該算法。

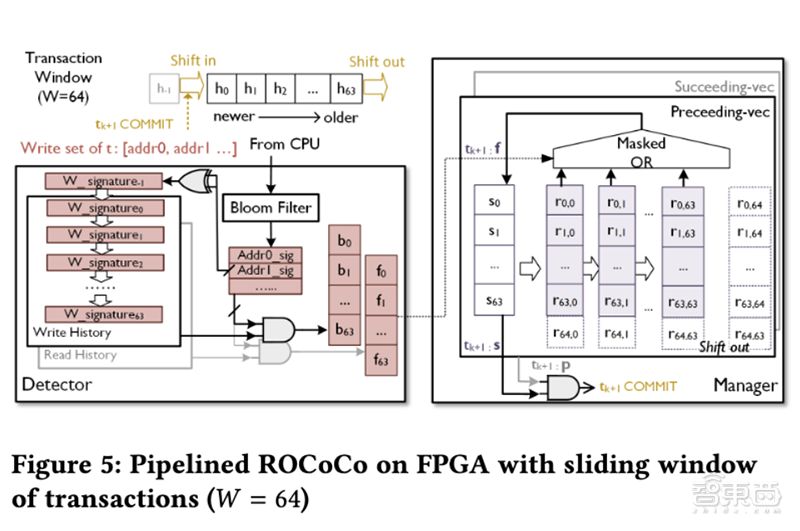

▲該研究提出的新型併發控制算法在可重構架構上的實現

如圖所示,事務之間的讀寫依賴關係在可重構架構上的Manager模塊以矩陣的形式在空間上平鋪開來,以此更高效地檢索並更新事務間讀寫依賴關係。之後在CPU-FPGA異構可重構系統上實現了基於該算法的高性能的事務內存系統的原型系統。

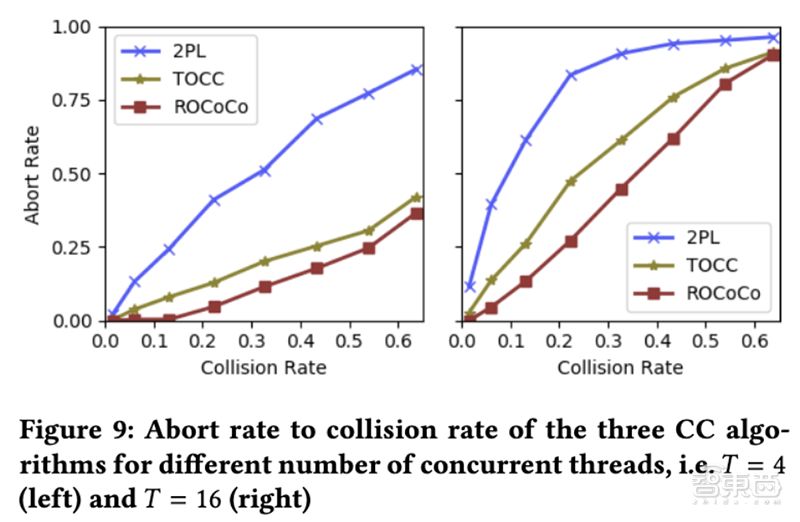

與綜合基準測試中的2PL和TOCC算法相比,ROCoCo算法最多可將訪問撤銷率降低56.2%和20.2%。

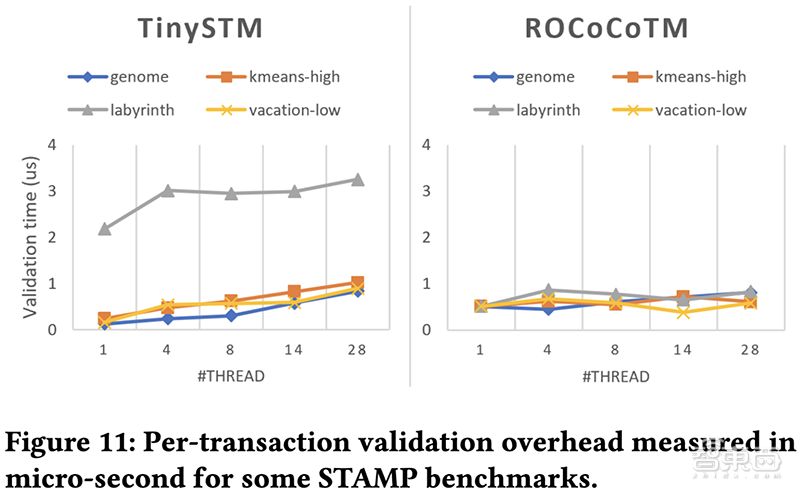

整個系統在英特爾的HARP2平台上實現,並使用STAMP測試集進行事務內存系統性能評估。

實驗顯示,該算法相比英特爾處理器內置的TSX(Transactional Synchronization Extension,事務同步擴展)指令集獲得了8.05倍的性能提升。

鑑於商用CPU-FPGA平台的部署快速普及,ROCoCoTM算法有望軟件程序員鋪平了道路,使他們可以藉助高級事務抽象來利用異構計算資源。

該研究分析一致性模型的方法不僅限於事務內存系統,還可推廣到分佈式系統、多處理器緩存一致性等問題的研究中。 02 十餘年可重構計算研發,AI芯片和CPU均已出爐

這一論文的合著作者彙集了魏少軍、劉雷波、尹首一、鄧仰東等多位清華學術大牛。

過去10餘年,清華大學魏少軍、劉雷波、尹首一團隊長期聚焦可重構芯片及其在芯片、硬件安全、密碼技術等關鍵技術研究,從“十一五”到“十三五”連續獲得國家自然科學基金項目、863計劃重點項目和其他國家重大專項項目的支持,在可重構芯片領域取得了多項重大技術突破。

清華大學微電子所所長、中國半導體行業協會、IC設計分會理事長魏少軍教授是國內集成電路產業的領軍人物,曾主導編寫了《人工智能芯片技術白皮書(2018)》,從定義、脈絡、標準以及發展趨勢等方面對AI芯片進行了深入而專業的研究報告,填補了國內空白。

魏少軍教授曾多次作為全球AI芯片創新峯會(GTIC)演講嘉賓,詳細解讀清華大學微電子所研究的可重構神經網絡計算架構。

清華大學微納電子系Thinker團隊自2016年以來基於可重構計算架構設計了數款Thinker系列低功耗終端AI芯片(Thinker I,Thinker II,Thinker S),受到學術界和工業界的廣泛關注。清華大學微電子所副所長、CAD技術研究室主任尹首一任Thinker芯片團隊帶頭人。

去年7月成立的AI芯片創企清微智能,即是從Thinker團隊脱胎而出,尹首一任清微智能首席科學家,清華大學博士、Thinker芯片主架構師歐陽鵬任清微智能CTO。

過去4個月間,清微智能先後推出其首款可重構超低功耗語音人工智能(AI)芯片TX210和首款多模態智能計算芯片TX510。( 清華創新架構芯片量產! 全球首款可重構超低功耗語音AI芯片 )( 全球首款多模態智能計算芯片來了! 基於清華可重構架構,同時支持視覺和語音處理 )。

此前在2016年1月,清華大學和英特爾宣佈聯合研發“融合清華可重構計算技術和英特爾X86架構的新型通用CPU”津逮CPU,即是結合清華可重構計算技術與x86架構。

去年年底,瀾起科技完成第一台津逮服務器平台產品的開發,於今年上半年進行市場推廣,已具備批量供貨能力。聯想、長城等數家服務器OEM廠商已採納津逮CPU及其系統解決方案,研發出了系列高性能且具有安全監控功能的服務器機型。