Moore定律與中國半導體_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2020-02-17 11:20

來源:內容由公眾號半導體行業觀察(ID:icbank)授權轉載自【桃芯科技 】,作者桃芯芯,謝謝。

桃芯科技

分享產品,分享知識,分享經驗。為物聯網發展和芯片設計提供桃芯方案。20年不長也不短了,20年最簡單的事,就是將一個人變老,一個人的黃金歲月往多了算不過40年。20年也可以將一個國家的GDP變到世界第二,也可以將IC產業普及到大眾認知。

一、導言

我們先往前説説00之前的半導體發展。90年代是真正的個人意識覺醒,以及全民商業化的序曲階段,是國內信息化的開始,中國GDP逐步加速。下面幾件事情如果你還有印象,那麼你應該也不年輕了。

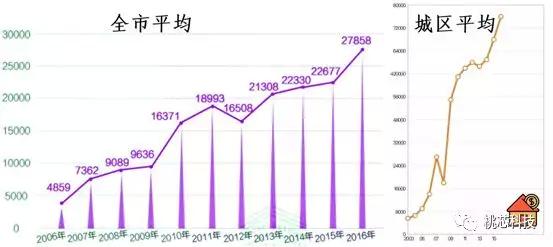

90年代末商品房開始出現了。如果我們知道中國的GDP是按照上圖那根曲線發展,那搞幾套房子就好了,不用做IC也不用做股票,當然也不用做投資。做了的就當娛樂。鄭淵潔據説買了10多套房子裝信,從1400元每平到14萬每平,你算算。那時候宇宙中心五道口的華清嘉園開盤的時候也就4000元。

當然還有其他的廠商EDA廠商包括Mentor做DFX,Ansys的IRdrop等等,還有消失的Avanti,Magma等等。但主流的全流程的EDA廠商,全球看來還是Synopsys和Cadence,其他廠商作為單點工具廠商有些活的還不錯。

**作為一個早期的IC工程師,用EDA廠商作為開篇,是因為這裏其實是應該向他們致敬。****那時候聽一位台灣人説,大陸合格的IC工程師還不足300人。**工程師們對synopsis和cadence的依賴還比較多,在實戰層面,無論從工具的使用上,還是從IC設計流程,甚至IC設計原理,都處於比較貧乏的狀態。直到今天,沒有他們,國內的IC設計幾乎完成不了。更別説,對小公司,他們還放水養着魚。

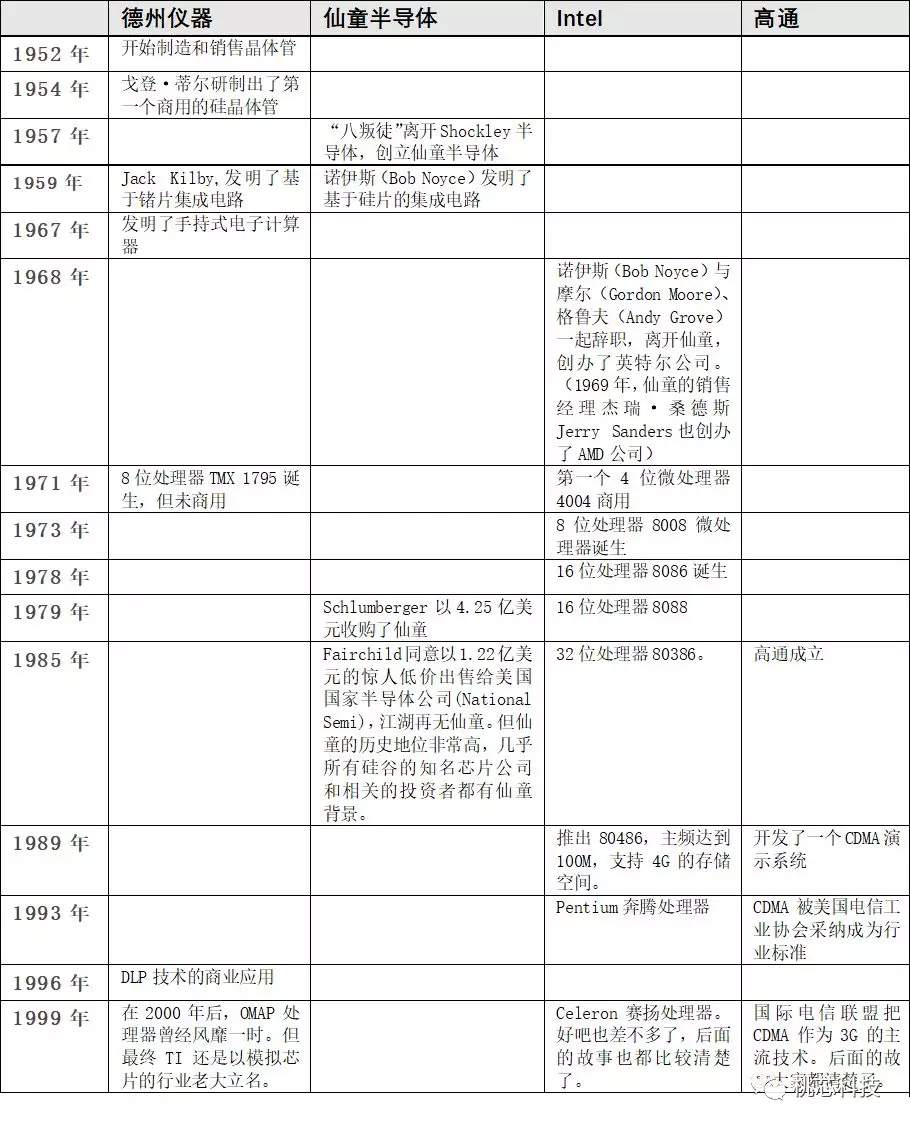

對於新世紀之前國外半導體發展,我們用幾個代表公司大概梳理了一下美國半導體發展的時間節點,回頭跟國內對應的時間可以做個對比。

二、國際半導體20年

2000年左右開始,國內半導體行業在互聯網浪潮的帶動下,出現了一波浪潮,大家發現從美國copy到國內paste好像是個能賺錢的生意,以百度,新浪,搜狐為代表掀起了第一波互聯網泡沫。另外一方面也確實是計算機及信息技術爆發帶來的底層技術上的強烈需求。

**2000到2008這幾年中,出現了一大批創業企業,特別多的情況是硅谷回國的工程師,然後帶着硅谷的投資,在國內創立了一大批的企業,算是第一次半導體發展浪潮。**説起來一些名字的話,有些應該大家很瞭解,有些則命運多舛。沒有系統的總結,我隨便説幾個通信行業相關的,包括中星微,展訊,鋭迪科,暢訊,硅谷數模,六合萬通,希圖,創毅視訊,新岸線等等吧,太多了。那時候方舟處理器也進行的如火如荼。

我也在其中一家創業公司。180nm工藝已經是挺先進的工藝了,FPGA用的是Xilinx的VertexII,流程都用DC/PT,仿真用VCS比NC-Verilog好像快不少,封裝用BGA已經是顯得非常NB了。雖然Synopsys和Cadence都是全流程,到目前為止,前端用Synopsys,後端用Cadence,測試用Mentor,大的地盤劃分一直沒有變。

IC行業裏面,可以從工藝的演進角度看,也可以從行業技術的演進去看,我下面舉幾個例子來看看國內的IC行業與國外同行的對比。

(一) EDA工具

EDA(ElectronicsDesign Automation)工具實際上是個泛泛的概念,用來做輔助電子相關設計的軟件都可以叫EDA。這裏我們專門介紹一下做數字IC的EDA,暫且不包含模擬,PCB,FPGA等方面的。

數字IC的設計,測試包含幾十道工序,對應的EDA軟件也大約有這麼多。看起來挺複雜的,但相比較製造過程,工序還是少很多。雖然製造過程也許不需要這麼多專業軟件,對材料,設備和工藝的要求比較苛刻一些。

**前面提到過EDA工具提供商裏面全流程的包括Synopsys和Cadence,而Synopsys又可以看做行業老大。**2018年Synopsys的營收大概31億美元,Cadence大約21億美元。加上第三名Mentor的13億美金,第四名ANSYS的12億美金,這幾家頭部公司的營收佔據了整個市場的幾乎95%。

針對數字IC設計流程中的EDA,我們挑一些比較重要的來説一下。通常的一個軟件可能會集成幾個工序的工作,負責好幾件事情。有些EDA公司在某個環節比較強,做出一個行業普遍認可的工具,我們叫點工具,它只負責整個工序的某個點。

我們就拿Synopsys舉個例子,看看涉及到的工具有多少,每個系列少則幾種,多則十來種:

目前還存在的其他的EDA公司基本都是點工具公司,像ANSYS的RedHark作為IR Drop分析的工具,在業界也是無出其右,其2018年營收估計應該有12億美金,當然還有一批小的點工具公司。

國內除了華大還有廣立微、概倫、芯禾、九同方、博達微、藍海微、珂晶達、鴻芯微納、奧卡思微和行芯等EDA相關工具研發的企業,在不同方向上做一些工作。就像CPU,操作系統一樣,EDA不光需要技術和人員投入,它也是需要有生態基礎的一項運動,目前國內EDA還任重道遠。

(二) 工藝製程

工藝製程是個耳熟能詳的詞。我們先看一個台積電工藝演進圖感受一下數字半導體工藝節點的變化,體會一下Moore定律。

從台積電官網所公佈的信息來看,在1987年成立時,他們的芯片工藝是3微米,在1990年提升到了1微米;2001年的時候提升到了0.13微米;2004年開始採用90納米工藝;隨後是65納米、45納米、40納米、28納米、20納米,2015年提升到了16納米;2016年升至10納米;2017年是7nm;5nm也已在去年開始生產,將在今年上半年開始大規模量產。

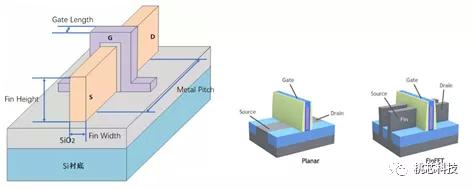

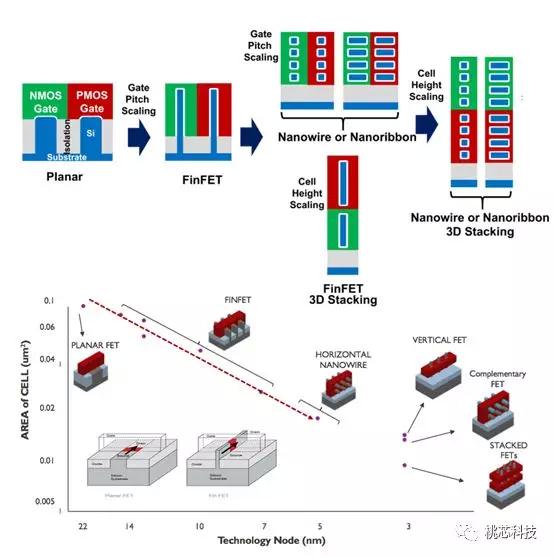

我們簡單説一下什麼是工藝尺寸。傳統ITRS定義技術節點是source和drain之間最小金屬間距的一半(Half-Pitch)。但到了20/22nm引入FinFET以後,Half-Pitch的減少開始變得很慢,但是因為結構3D化後晶體管數量仍舊激增,廠商再用Half-Pitch就顯示不出來技術進步了。因此各家的命名就比較亂,比如説台積電從10nm到7nm是用10nmX0.7的理想計算得到7nm,但Half-Pitch只是從42nm降到40nm。原理上每降一次工藝面積縮小一半,對應長寬各減小到原來的70%,這是20->14->10->7nm名稱的由來。

晶體管的結構也經歷了從2D到3D的演變。在20nm以後從PlanarFET演化到FinFET的架構。FinFET的創新性3D晶體管架構,可讓IC製造商生產出尺寸更小、速度更快、功耗更低的器件。

在PlanarFET 到FinFET之間還出現了一種FD-SOI的工藝技術。FD-SOI技術還是一種平面工藝,但通過使用不同的起始襯底來槓桿化和延伸現有批量CMOS平面製造工藝的性能。FD-SOI的襯底中,在硅基底上布有一層超薄的氧化物薄膜以充當絕緣層。與傳統的塊狀硅技術相比較,FD-SOI技術能提供更好的電晶體靜電特性,也能降低影響元件性能的泄漏電流。

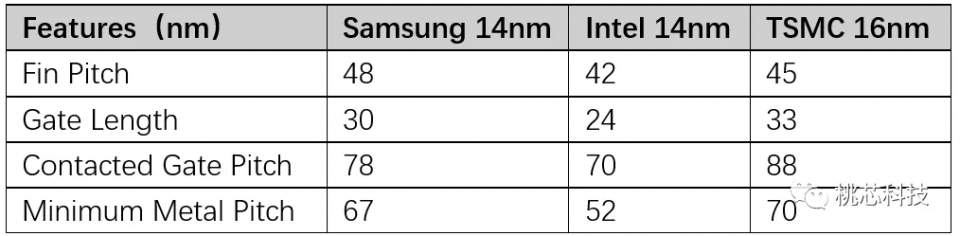

下表是14nm工藝下的對比參數,GateLength還是30左右,MetalPitch也在50-70,都不代表14nm本身這個數字。

中芯國際成立的2000年,當時台積電營收已經做到了1662億新台幣,淨利潤也做到了651億新台幣,同比增長也分別高達127.3%和165.1%。在2002年九月,中芯國際北京兩座12英寸工廠動工;2003年,中芯國際又收購了摩托羅拉在天津設立的八英寸芯片廠。創始人張汝京曲折的從美國進口0.18微米工藝的生產設備,這種情況一直延續到0.13微米、90納米和65納米的工藝上。官方説法,中芯國際在2017年2季度就開始推出28nmHKMG製程,但當時28nm HKMG良率只做到40%,這離能被大家接受的大規模量產還有很大距離。而在2018年第一季度台積電的10nm工藝已經為他帶來了19%的營業收入。

在新的CEO梁孟松到來後,14nm被提高到優先於28nm的地位。梁孟松曾在2019年Q2的財報會議上表示,“中芯國際第一代FinFET 14nm工藝已經進入客户驗證階段,產品可靠度與良率進一步提升”。期待中芯國際14nm早日量產。目前中芯國際最成熟,營收最大的應該還是55nm工藝。

國內其他的代工廠目前狀態還比較好的包括華力微電子等。他們自2010年1月建廠以來,到2019年已經投入了80億美元進行研發,目前主要產能在55nm以及40nm工藝,康橋廠二期,則承擔了華力微28nm到14nm等先進工藝的生產任務。

**從國際角度看,台積電,Intel和三星是領導整個工藝製程的領頭羊。**目前台積電、三星已經挑起3nm的戰局。據悉,三星已經完成了首個3nm製程的開發,計劃2022年規模生產3nm芯片,此前台積電也計劃2022年量產3nm。

Intel稍有尷尬,我們知道Intel創始人Moore提出的Moore定律,一直到14nm之前都是領先業界。而剛剛下野的柯再奇就有點尷尬,業界有柯再奇‘擠牙膏’的梗。在他任內,從14nm到14nm+++尷尬無比,搞了3年多。

2014年蘋果幾經周折在台積電終於實現了20nm A8的量產,而當年英特爾已經開始量產14nm,領先台積電1-1.5代。蘋果對CPU性能的苛刻要求迫使台積電的一路狂奔,在18年反超Intel。而現在,Intel的10nm才剛剛量產,7nm估計也得2年後,和另外2家的3nm同步上了。

不止於此,老陪襯AMD的RyZen居然在也迎頭趕上,在CPU領域Intel也沒有那麼閒庭信步了。看來Intel要好好反思整理一下。

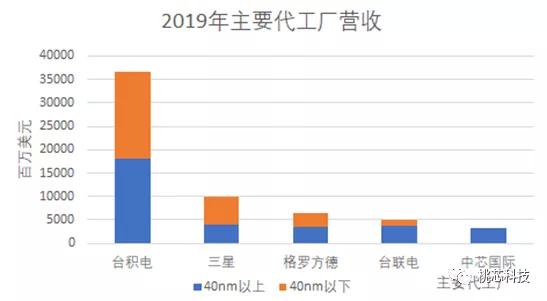

我們感受一下台積電在代工領域的行業地位。通常的,台積電每年佔有50%-60%之間的市場佔有率。當然了,三星不算是純的代工廠。

這是一個系統工程,如果要趕超世界先進水平的話,不光要採購設備和材料,還需要生產設備和材料,這才是一個比較理想的狀態。但是也不可能一蹴而就,紮紮實實的,先把一個工藝吃透,建立自己的研發能力,在此基礎上追趕。盲目在後面追趕工藝製程並不是一個好的辦法。摩爾定律一定會放緩,乃至未來消失,我們依然有機會。當然了,我們也一定要關注下面將要發生的跨越性的變革,比如説,是不是量子科技帶來的,雖然他現在還很幼稚。

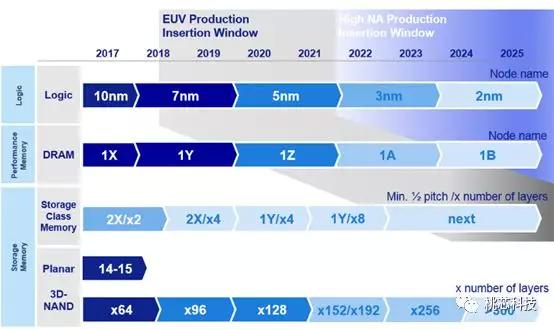

順手的,我貼一個存儲器在工藝方面的進展(來源,AMSL),存儲器應該是芯片領域裏單品銷量最大的產品,甚至達到1/3的規模。

CPU的情況相對沒那麼複雜,PC/Server的市場主要是Intel和AMD佔據,手持設備和嵌入式主要是Arm,最近RISC-V藉着指令集開源的東風有星火燎原的勢頭。國內也有一些CPU的開發者,龍芯的處理器瞄準的是Intel這類應用,而其他的主要是作為嵌入式或者某些專用場景。

ARM的區別在於,他本身只提供CPU核,由其他廠商集成為各種單核或多核處理器,無論APPLE,高通,華為等等都使用ARM的內核。

對應RISC-V,目前的內核提供商包括SiFive,Andes,芯來,中天微等。RSIC-V是一個開源指令集的嵌入式CPU,目前各家公司根據開源的指令開發自己的底層IP核,同時對於拓展部分DSP內核也採用了基於Andes的指令集。

雖然指令集是開放的,但硬件部分每家的經驗,能力不一樣,工具鏈的能力也不一樣,所提供的產品應該説也是具有很大差別。雖然説是開放的,對於國內廠商來説是個新的機會,但從目前的發展狀態來看,還是SiFive和Andes的內核比較有競爭力,大陸的東西還是很弱勢,要趕超的話,要加油啊。

作為使用者,從生態或是性能的角度看依然是ARM的東西比較可靠,但如果RISC-V的生態比較好,是未來趨勢的話,還是應該儘早參與。

直到2019年,龍芯發佈了龍芯3A4000/3B4000,使用龍芯公司最新研製的新一代處理器核GS464V,主頻1.8-2GHz,採用28nm工藝。

而反觀2000年的時候Intel的市值已經達到5000億美元,酷睿系列面世後的2006年的營收達到354億美元,而2018年Intel的營收已經高達780億美元,長期位列半導體公司排名第一位。

最近AMD的RyZen比較風光,而且龍芯官方對比的也是AMD前一個挖掘機系列,我們就把AMD RyZen9也拿來和他一起對比一下,可以看到差距還是非常大:

這些都是挑戰,而且東西越沒人用迭代越慢,從指標上看差距也許還不到10年,但從生態看就差20年了。有人開玩笑説,如果Windows被禁止了,國內的CPU,OS,軟件沒準很快就上去了。不過這只是玩笑。

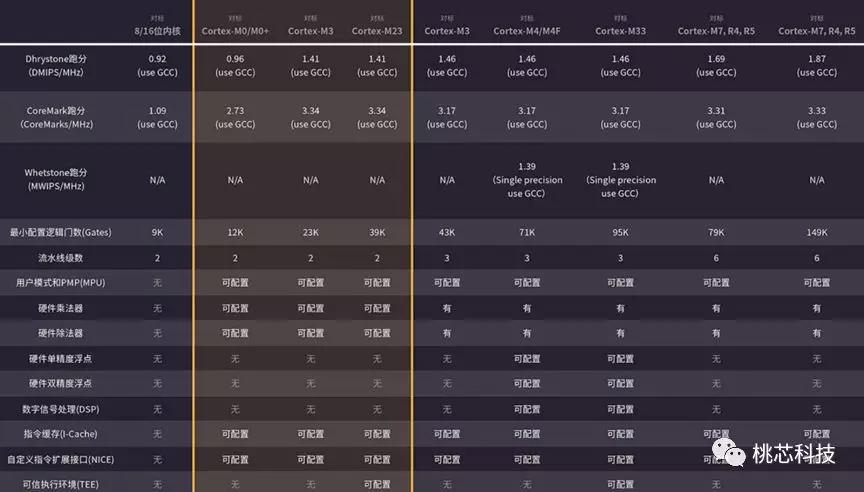

RISC-V和ARM對比的話,目前幾乎所有的廠商都能拿出比較漂亮的表格,但是這個需要用户實戰的效果作為最終評判。到目前為止,用RISC-V量產的芯片還不是很多,不過近幾年肯定會出現一個放量增長的過程。如果性能基本匹配,而且ARM的M系列IP核不做重大的戰略調整的話,那麼新局面一定會出現。

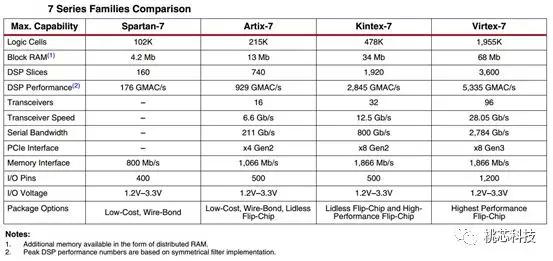

説到FPGA就必須説行業龍頭Xilinx,成立於1984年的賽靈思在1998年推出Virtex系列FPGA,演進到2006年推出45nm的Virtex6大行其道,直到用這個系列拿下行業龍頭的寶座。另外,他還有並行的低端產品線是Spartan系列。從2011年開始7系列FPGA後,Xilinx在7系列上衍生出新的產品系列,目前一共4個系列。

**2019年Xilinx以近30億美元的營收,以及超過50%的市場佔比繼續引領FPGA技術以及市場的發展。**排行第二的Altera以性價比的優勢在中低端市場佔據較大份額,與Xilinx一起佔據了FPGA 將近90%的市場份額。2015年Altera以167億美元的價格被Intel收購。

FPGA是一個比較特別的行業。首先FPGA本身是一種芯片,但這種芯片可以通過內部資源配置芯片的具體功能。其次他還需要一套配合芯片應用的EDA工具(比如Xilinx的ISE),如果內部帶CPU那還得配上一套軟件開發的IDE(比如Xilinx的EDK)。

通常FPGA除了比較靈活之外,價格太高,面積太大,功耗也高,基本上都是做原型產品來用,以及一些產品數量不大的市場,一旦芯片市場容量稍微有一定規模,就會轉移到ASIC上面。近年來,隨着FPGA廠商在功耗,成本上的努力,在某些產品場景上也顯示出來了一定優點。

FPGA的內部資源根據產品的目標場景有不同的配置,如果需要設計高端的產品,對廠商來説也是比較具有挑戰性。拿Xilinx的Virtex7來説明一下FPGA內部資源。先看一下7系列的配置。

多達200萬個邏輯單元,每個單元至少相當於15個IC邏輯門,以及30萬個Slice,每個Slice平均包含一個LUT以及一個寄存器等。68Mb RAM非常給力,滿足絕大多數IC對內部存儲的需求。5335 GMACS 的 DSP 處理性能,滿足無線 LTE 基礎設施設備、LED 背光和3D數字視頻顯示器等應用。支持 400G 橋接和交換結構有線通信系統,支持核心有線基礎設施高速串行連接功能和內置式 Gen3x8 PCI Express,以及其他DDR藉口,串行藉口等。LTE基帶能夠滿足通用平台內 LTE 基帶處理嚴苛的延遲要求,支持 多種空中接口混合使用。集成PowerPC,ADC等等。

目前國內FPGA都還比較弱,僅僅從參數這個層面來看的話,就已經遠遠不在一個層面。國內廠商需要在特定場景,特定應用裏面尋找合適的空間發展,以積累經驗和資本,再圖謀更高規格場景。

(五)無線通信(5G,WiFi,藍牙)一)5G演進

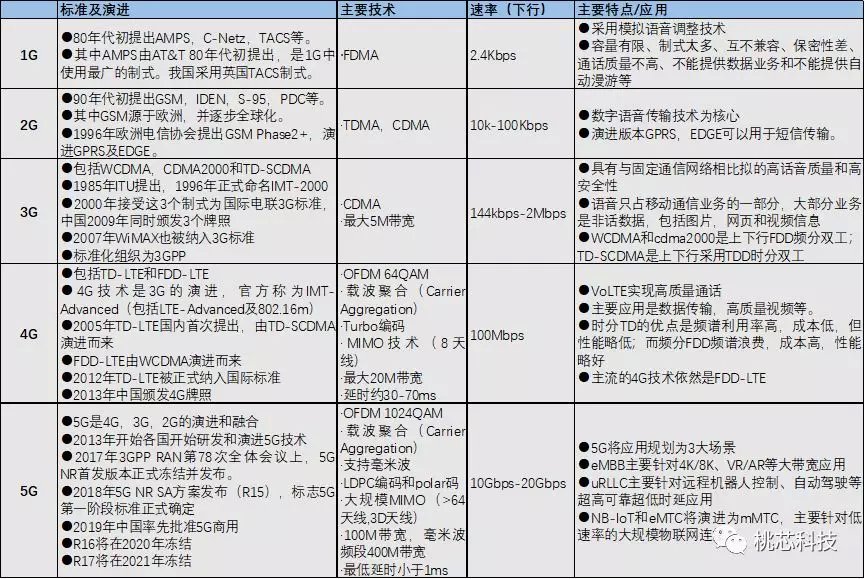

這裏也通過回顧無線通信的發展來看一下近20年無線技術方面演進的情況,應該説也是突飛猛進,各類標準演進非常積極。説無線通信必然要説5G,但5G太廣為人知了,我們也在不同文章有過相關的論述,這裏簡單總結一下。

2003年左右,我們聽説MTK的2G手機芯片turnkey方案大行其道,橫掃深圳的山寨機市場。公司也就百十來人,年會的時候抽美金,抽寶馬,很快MTK就變成了移動通信芯片的一級供應商,而現在轉眼5G就來了,你説快不快。

這個表大致比較清晰的描述了從1G到5G的大致發展歷程,以及關鍵技術和應用場景,作為背景知識應該夠了。

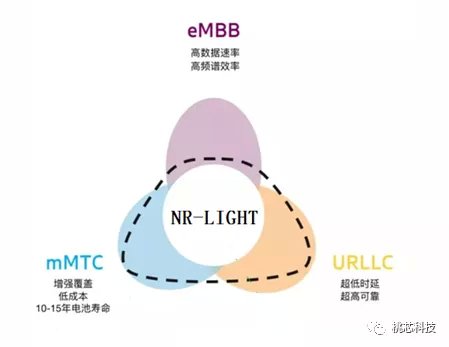

5G定義了eMBB、uRLLC和mMTC三大場景,eMBB主要針對4K/8K、VR/AR等大帶寬應用,uRLLC主要針對遠程機器人控制、自動駕駛等超高可靠超低時延應用,而NB-IoT和eMTC將演進為mMTC,主要針對低速率的大規模物聯網連接。

2018年發佈的R15是5G第一版成型的商用化標準,R15目前支持5G三大場景中的增強型移動寬帶(eMBB)和超可靠低時延(URLLC)兩大場景,海量機器通信(mMTC)場景標準將在R16中確定。

R15重點關注如下幾個方面:新空口(波形、編碼、參數集、幀結構、大規模陣列天線等)、網絡架構(NSA、SA、CU/DU切分等),並聚集在eMBB場景。

**大家之前聽到的華為Polar碼的故事,實際上最後高通力推的LDPC碼作為eMBB數據信道(無論長短碼)的編碼方案,而Polar碼當作安慰獎作為eMBB控制信道的編碼方案。**這事沒那麼重要。

R16不僅將完善5G場景,包括5G-V2X、高可靠、專網、行業局域網,mMTC(eNB升級空口+5GC),還將有力提升5G性能:MIMO增強、大氣波導干擾規避、大數據採集標準化等。2019年6月3GPP RAN#84會議上確定R16計劃將於2020年3月凍結髮布。同時R17的工作內容也確定下來,並計劃在2021年6月凍結。

R17將要涉及的更新將包括:

NR Light:針對中檔NR設備(例如MTC、可穿戴等)運作進行優化設計;小數據傳輸優化:小數據包/非活動數據傳輸優化;Sidelink增強:sidelink是D2D直聯通信採用的技術,Rel-17會進一步探索其在V2X、商用終端、緊急通信領域的使用案例,實現這幾個應用中的最大共性。定義52.6GHz以上頻率:Rel-15中定義FR1為410MHz - 7.125GHz,FR2為24.25GHz – 52.6GHz,R17將5G NR的頻段範圍從52.6GHz擴展到了71GHz。進一步把室內定位精準度提升到釐米級,大概是20-30釐米左右。在工業物聯網的應用中加強室內資產追蹤、AGV追蹤等。

關於NR-Light,如果説uRLLC針對的是“高端”物聯網應用場景,而mMTC針對的是“低端”物聯網應用場景,那麼在eMBB、mMTC與uRLLC之間存在的“中端物聯網市場”的空白地帶將是NR-Light將要研究和定義的內容。

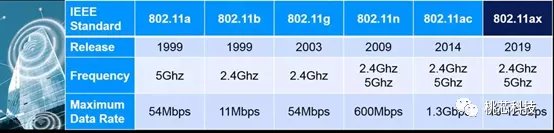

二)WiFi演進

1990年,基於未授權頻譜中的無線通信,IEEE 802.11工作組成立,初始版Wi-Fi最終於1997年正式實現標準化,但並未產生廣泛影響。直到1999年,802.11b應運而生,該技術使用與初始802.11無線標準相同的2.4GHz ISM頻段,但將支持的吞吐量大幅提高到了11Mbit/s,實現了對標10 Mbit/s以太網的網絡標準。可以看出WiFi同以太網的密切歷史淵源,所以説他是具有互聯網基因的一項無線技術。

同時為了匹配以太網的高網速,以及解決2.4G頻段比較擁擠的情況,802.11a也幾乎同時誕生,他採用5.8G的載頻,速率達到54Mbps。

然而由於802.11a採用了不同的頻段,需要不同的射頻,與802.11b不兼容,所以應用並不廣泛。