從ISSCC 2020 看Chiplet的研究現狀_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2020-02-27 09:41

來源:內容由公眾號半導體行業觀察(ID:icbank)原創,謝謝!日前,ISSCC 2020已落下帷幕。有“集成電路奧林匹克”之稱的ISSCC一直是集成電路新技術的風向標,每年的ISSCC都會有一系列的集成電路新技術和新設計方法被報道出來。此次ISSCC 2020中有一個非常鮮明的特徵,就是多篇論文都在討論Chiplet這一技術。

Chiplet是近兩年被熱炒的一種技術,我們也在此前多次報道過這一技術(此處可以給之前文章的鏈接)。其本質是把多個“小芯片”通過先進的封裝技術封裝到一起來組成了系統級的芯片。因此Chiplet有兩項關鍵問題需要解決。一個是如何將各個“小芯片”連接起來,這就是先進的封裝技術。另一個則是如何去劃分、定義這些“小芯片”的功能、接口、互聯協議等,這部分屬於是架構設計的範疇。這兩部分的研究需要相互配合才能構造出優秀的基於Chiplet的系統級芯片。在ISSCC2020中,這兩方面的技術都被廣泛的介紹到了。這種我們之前還以為的“未來技術”,其實已經開始大行其道。

讓人“恍然大悟”的AMD

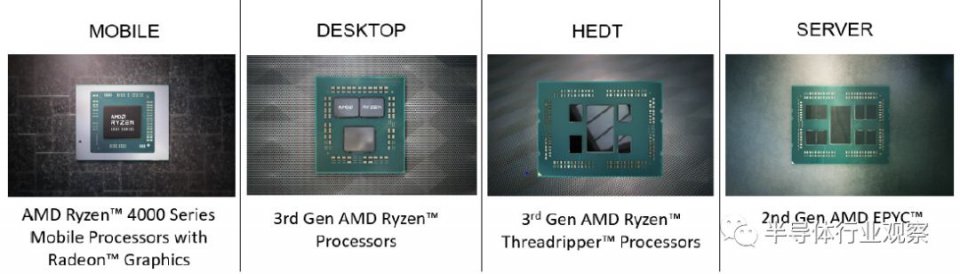

ISSCC 2020的Session 2是處理器專場。在開篇介紹了AMD的Zen 2處理器,第二篇馬上就介紹瞭如何基於Chiplet的思想用多個Zen 2處理器的小芯片來構建服務器或者桌面處理器。其實AMD利用Chiplet技術來構造高性能處理器。下圖中時AMD列舉的他們已經採用了Chiplet技術的高性能處理。

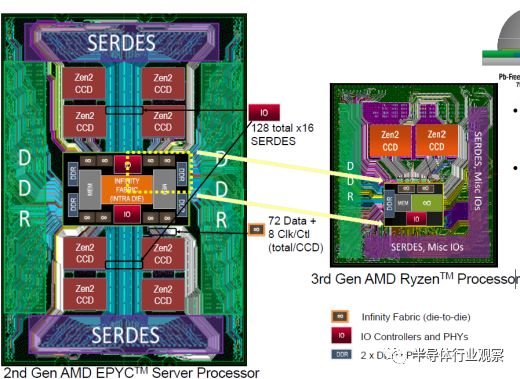

分解成Chiplet以後,可以根據需求組合出不同版本的系統芯片。但這種組合對於佈局佈線,尤其是電源網絡的設計是一個巨大的挑戰。圖2是AMD給出的服務器處理器和桌面處理器設計組合的區別。

在後續AMD還介紹和操作系統有關的調度方法以及電源管理方法。可見基於Chiplet的設計從架構的角度、從電路系統的角度都還有很多可以優化的點。而這些已經脱離了固態電路的研究範圍,進入到了計算機系統結構、電路與系統、封裝技術等研究的範疇。

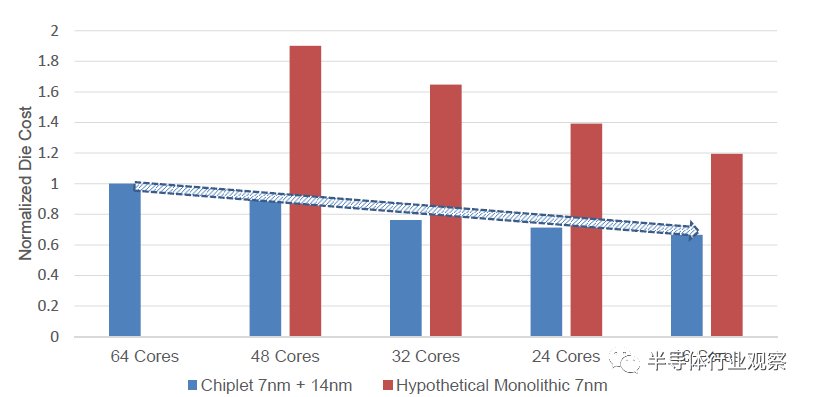

通讀了AMD的論文並多次研讀其報告PPT,發現AMD在Chiplet領域的研究非常詳實,涵蓋了多個關鍵技術點。對認識理解Chiplet技術有非常大的裨益。最後AMD還非常耿直的貼了一個歸一化的價格圖。説明確實省錢了不少。不過論文中指出用Chiplet造價隨着核數下降得更慢,因此可能有一個價格的均衡點來取決於是否採用Chiplet。

如果説AMD的兩篇論文是一道開胃菜的話。Grenoble Alpes大學等機構一起發表的基於6個Chiplet來構造的96核處理器就更是讓人驚豔。此前我們也對此做過報道(上鍊接)。

當然,他們給出用Chiplet的原因和AMD類似。首當其衝的還是成本問題,其次是模塊化設計和異構集成。其實後者本質上也可以看成是成本問題。而他們提出Chiplet需要解決的3個挑戰:生態系統成熟度,技術和架構劃分,芯片接口、可測試性、3D CAD流程等。但就我們看來,這三個問題是從宏觀到微觀的。生態系統成熟度是一個很宏觀的概念,其背後要依賴於技術(主要是各種封裝與集成技術)和架構劃分的成熟,這個我們在文章的開篇就已經討論過了。而技術和架構劃分最終落地到實處,就是芯片的接口如何定義、如何保證基於Chiplet的芯片是可以被測試的、如何形成設計方法學並研發出對應的CAD/EDA工具。

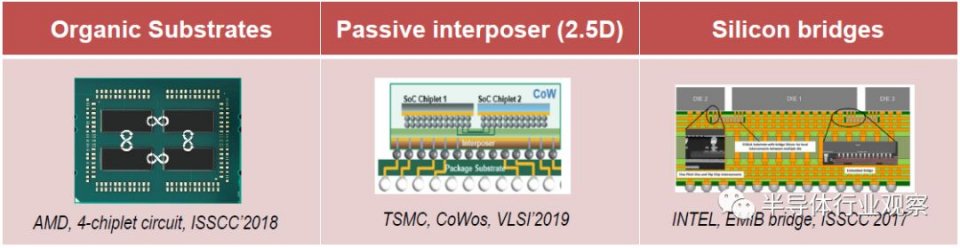

目前已有的Chiplet包括了Organic Substrates、Passive interposer (2.5D)以及Silicon bridges等。如圖4所示:

部分技術只支持Chiplet的邊到邊互聯(如AMD在ISSCC 2018中的介紹的,以及Intel的EMIB橋),可擴展性較差;如何集成異構芯片或有差異化的模塊;如何集成不容易擴展但卻很必要的部分(如IO、模擬電路、電源管理等);

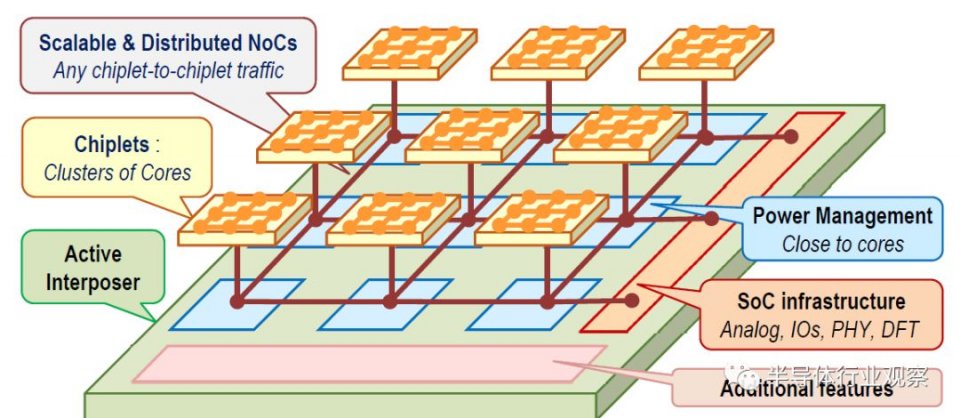

為了解決上述問題,他們提出了一種叫Active Interposer 的技術。與上圖中的Passive Interposer對應。也就是説在中介層(Interposer)上研究如何去集成一些主動器件(有源器件)。圖5説明了這個問題。

其後還詳細介紹了L1(第一級Cache)到L2(第二級Cache)的互聯方法,L2(第二級Cache)到L3(第三級Cache)的互聯方法,以及L3(第三級Cache)到外部存儲器的互聯方法。L1到L2依靠的是在中介層直接走線,L2到L3採用了多個異步握手電路構成的片上網絡來傳遞信號,而L3到外部存儲器接口則依靠同步的片上網絡來傳輸。

電源管理也被放到了中介層上面,可以實現對於每個裸片近距離的電源管理。從而得到更高的能源利用率。

除了在Session 2以外,在Session 8的Highlighted Chip Releases中,Intel實際上介紹他們自己的Chiplet技術Foveros。當然,在這裏Intel主要秀的是他們的封裝技術和接口電路設計。相比於AMD討論了很多系統架構的設計,Intel幾乎沒有提及這方面的內容。

在其它的一些Session中還有介紹分可用於Chiplet的高速接口電路設計,在這裏就不一一詳述了。

從以上的分析我們可以看出,在這一次的ISSCC 2020中。Chiplet的研究和討論已經比較深入了。相較於此前發佈的研究,現在Chiplet的研究從單純的封裝技術、接口電路逐漸開始向從工藝到架構全方位優化設計研究發展。這其實也標誌着Chiplet技術正在迅速的成熟起來。因此,Chiplet的未來,也許已經來到。

**注:**本文在創作過程中獲得電子科技大學黃樂天副教授指導,特此感謝。

**黃樂天:**電子科技大學電子科學與工程學院,副教授, 電子科技大學博士,CCF集成電路設計專業組委員。主要研究方向為計算機系統架構與系統級芯片設計,已在IEEE Transactions on Computers (CCF A 類期刊)等高水平期刊和CODE+ISSS、FCCM、ASPDAC、ISCAS等頂級會議上發表高水平論文50 餘篇,申請專利11項,出版學術著作1部。參加工作以來主持和參與過國家自然科學基金項目重點項目、裝備預研重點項目、國家科技重大專項、國家“863”重點研究計劃等國家級重點科研項目,曾榮獲Altera公司(Intel PSG)金牌培訓師、 第七、第八、第十二屆研究生電子設計大賽優秀指導教師、電子科大網絡名師等稱號。先後擔任過國際會議ICICM 2016年Publicity Chair, ISOCC 2016年Session Co-Chair、APCCAS2018 Special Session Chair等學術職務。