全球首款多陣列憶阻器“存算一體”系統問世_風聞

一洗闲愁十五年-2020-02-28 17:22

全球首款多陣列憶阻器“存算一體”系統問世

來源:科學網 科技日報 作者:金鳳 時間:2020/2/27

原文網址:http://news.sciencenet.cn/htmlnews/2020/2/436321.shtm

科技日報北京2月26日電 隨着摩爾定律趨近極限,通過集成電路工藝微縮的方式獲得算力提升越來越難;而計算與存儲在不同電路單元中完成,會造成大量數據搬運功耗增加和額外延遲。如何提高算力,突破技術瓶頸?

26日,記者從清華大學獲悉,該校微電子所、未來芯片技術高精尖創新中心錢鶴、吳華強教授團隊,與合作者共同研發出一款基於多個憶阻器陣列的存算一體系統,在處理卷積神經網絡時的能效比圖形處理器芯片高兩個數量級,大幅提升計算設備的算力,且比傳統芯片的功耗降低100倍。相關成果近日發表於《自然》雜誌上。

如何用計算存儲一體化突破AI算力瓶頸,是近年來國內外的科研熱點。尋找合適的硬件,是提升算力的基礎之一。

錢鶴、吳華強教授團隊通過優化材料和器件結構,成功製備出高性能憶阻器陣列。為解決器件非理想特性造成的系統識別準確率下降問題,他們提出一種新型的混合訓練算法,僅需用較少的圖像樣本訓練神經網絡,並通過微調最後一層網絡的部分權重,使存算一體架構在手寫數字集上的識別準確率達到96.19%,與軟件的識別準確率相當。

同時,他們提出空間並行的機制,將相同卷積核編程到多組憶阻器陣列中,各組憶阻器陣列可並行處理不同的卷積輸入塊,提高並行度來加速卷積計算。

在此基礎上,該團隊搭建了全硬件構成的完整存算一體系統,在系統裏集成了多個憶阻器陣列,並在該系統上高效運行了卷積神經網絡算法,成功驗證了圖像識別功能,證明了存算一體架構全硬件實現的可行性。

“基於憶阻器的新型存算一體架構,可以打破算力瓶頸,滿足人工智能等複雜任務對計算硬件的高需求。”清華大學未來芯片技術高精尖創新中心教授吳華強説。

轉者按:另附錢鶴、吳化強科研團隊舊聞一則

清華微納電子系錢鶴、吳華強團隊在物理不可克隆函數芯片領域取得重要進展

來源:清華大學官網 2019年03月22日

原文網址:https://www.tsinghua.edu.cn/publish/thunews/10303/2019/20190320143543082222110/20190320143543082222110_.html

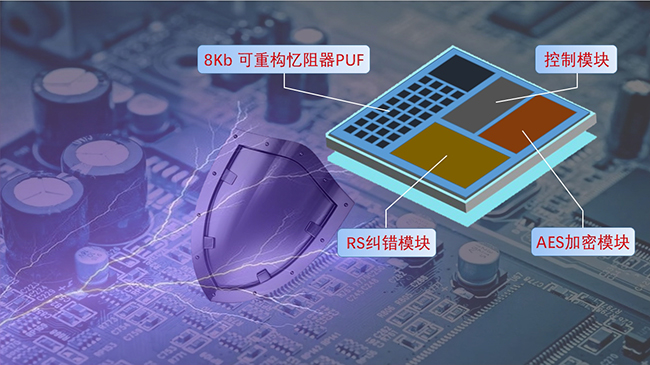

清華新聞網(2019年)3月22日電 近日,微納電子系錢鶴、吳華強教授團隊在第66屆國際固態電路會議(ISSCC 2019)上以“基於阻變存儲器的具有6×10-6原始比特錯誤率的可重構物理不可克隆函數芯片(A Reconfigurable RRAM PUF Utilizing Post-Process Randomness Source with <6×10-6 N-BER)”為題,報道了國際首個基於阻變存儲器(RRAM)的物理不可克隆函數(PUF)芯片設計,該芯片在可靠性、均勻性上相對於之前工作都有明顯提升,且具有獨特的可重構能力,能夠實現高效硬件安全防護。該芯片代號取名為XUANWU,意為具有超凡防禦能力的中國古代四大神獸之一“玄武”。

物理不可克隆函數芯片(XUANWU X01)

這項工作得到了《自然·電子》(Nature Electronics)的關注。3月15日,在其最新發布的刊物中以研究亮點(Research Highlight)的方式給予了重點報道,認為具備可重構一個全新的PUF芯片的能力是一種獨特特點,大大降低了密鑰過度使用以及更改硬件所有權的風險。文章中還指出:“清華大學研製出了一種基於阻變存儲器的PUF芯片,通過了美國國家標準與技術研究院的隨機測試……採用差分阻值的方法,實現了原始位誤碼率低於<6×10-6,驗證了該PUF芯片優異的抗環境變化的穩定性。”

隨着智能硬件的廣泛普及,半導體供應鏈安全威脅的增加,硬件安全變得越來越重要,僅基於軟件的安全防護已經不能滿足需求。近年來,物理不可克隆函數已經成為一種新的硬件安全防護手段。集成電路PUF可以利用器件固有的隨機性(如工藝的隨機性)在特定的激勵下產生不可預測的響應,進而充當了唯一性識別芯片的硬件“指紋”。然而,傳統的集成電路PUF存在兩個明顯的缺點:首先,工藝的偏差存在一定的固有偏執,導致PUF輸出的隨機性不足。其次,由於工藝偏差直接產生於集成電路製造過程中,一旦產生則不可進行改變,進而導致PUF的輸出不可進行重構。在這種情況下,當PUF遭遇多次攻擊或壽命用盡時,被PUF保護的硬件則會重新遭遇硬件安全威脅。

RRAM作為一種新型存儲器,利用器件的電阻值完成對信息的存儲。相比於傳統的閃存(flash)以及動態隨機存儲器(DRAM),RRAM具有高速、低功耗、面積小等多項優勢,是新一代高性能存儲器的重要候選之一。此外,RRAM因其所特有的類神經元特性也被廣泛用於類腦計算領域。由於RRAM的工作原理是基於導電細絲的斷裂與生長,而這個過程存在較強的隨機性,使RRAM的電阻存在器件與器件之間(D2D)以及循環與循環之間(C2C)的隨機性,這些隨機特性也使其適用於硬件安全防護。

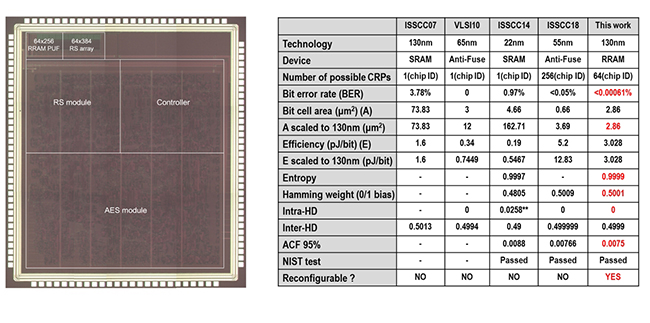

針對傳統集成電路PUF的不足,利用RRAM的優勢,清華大學微納電子系博士研究生龐亞川在ISSCC2019上首次介紹了一種基於RRAM電阻隨機性的可重構物理不可克隆函數芯片設計。該報告提出了一種電阻差分方法用於產生PUF輸出以消除工藝固有偏差以及電壓降(IR drop)的不利影響。為了在電路層次實現該方法,該團隊設計了一款高精度的靈敏放大器電路以精確比較兩個RRAM器件的電阻。大量的測試數據顯示所設計的RRAM PUF與之前的工作相比,具有最低的原始比特錯誤率、最小的單元面積、最好的均勻性以及獨特的可重構能力,能夠有效抵抗物理攻擊,具有很好的發展潛力。

XUANWU X01技術指標情況

IEEE ISSCC(International Solid-State Circuits Conference 國際固態電路會議)始於1953年,是集成電路設計領域最高級別的學術會議,素有“集成電路領域的奧林匹克”之稱。

清華大學微納電子系博士生龐亞川為該論文的第一作者,吳華強教授為通訊作者。該研究得到了國家自然科學基金委、國家科技部、北京市科委、北京未來芯片技術高精尖創新中心等相關項目的支持。

團隊合影(從左至右分別為錢鶴、龐亞川、吳華強、高濱)

近年來,微納電子系錢鶴、吳華強團隊圍繞阻變存儲器的關鍵科學問題,從材料器件優化、架構設計到系統集成、芯片應用等方面開展了系統研究,在國際期刊如《自然·通訊》《先進材料》《納米快報》及領域頂級學術會議如國際電子器件會議(IEDM)、超大規模集成電路會議 (VLSI)、國際固態電路會議(ISSCC)等發表多篇學術論文,為阻變存儲器芯片的產業化打下技術基礎。

報道鏈接:

https://www.nature.com/articles/s41928-019-0227-0