芯片測試科普_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2020-03-16 14:45

來源:內容由半導體行業觀察(ID:icbank)授權轉載自公眾號【桃芯科技】 ,作者桃可芯,謝謝!作為一個芯片設計公司(fabless),我們也非常關注集成電路產業鏈的各個環節,以此更好地給客户提供價值。

這次我們給大家説説芯片測試相關。

測試在芯片產業價值鏈上的位置

如下面這個圖表,一顆芯片最終做到終端產品上,一般需要經過芯片設計、晶圓製造、晶圓測試、封裝、成品測試、板級封裝等這些環節。

在整個價值鏈中,芯片公司需要主導的環節主要是芯片設計和測試,其餘的環節都可以由相應的partner來主導或者完成。

圖(1)

測試如何體現在設計的過程中

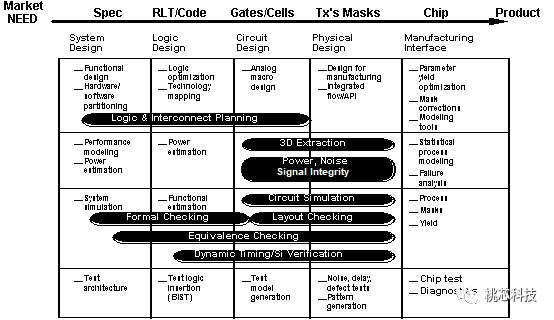

下圖表示的是設計公司在進行一個新的項目的時候的一般流程,從市場需求出發,到產品tape out進行製造,包含了系統設計、邏輯設計、電路設計、物理設計,到最後開始投入製造。

最下面一欄標註了各個設計環節中對於測試的相關考慮,從測試架構、測試邏輯設計、測試模式產生、到各種噪聲/延遲/失效模式綜合、進而產生測試pattern,最後在製造完成後進行測試,對測試數據進行分析,從而分析失效模式,驗證研發。

所以,測試本身就是設計,這個是需要在最初就設計好了的,對於設計公司來説,測試至關重要,不亞於電路設計本身。

設計公司主要目標是根據市場需求來進行芯片研發,在整個設計過程中,需要一直考慮測試相關的問題,主要有下面幾個原因:

1) 隨着芯片的複雜度原來越高,芯片內部的模塊越來越多,製造工藝也是越來越先進,對應的失效模式越來越多,而如何能完整有效地測試整個芯片,在設計過程中需要被考慮的比重越來越多。

2) 設計、製造、甚至測試本身,都會帶來一定的失效,如何保證設計處理的芯片達到設計目標,如何保證製造出來的芯片達到要求的良率,如何確保測試本身的質量和有效,從而提供給客户符合產品規範的、質量合格的產品,這些都要求必須在設計開始的第一時間就要考慮測試方案。

3) 成本的考量。越早發現失效,越能減少無謂的浪費;設計和製造的冗餘度越高,越能提供最終產品的良率;同時,如果能得到更多的有意義的測試數據,也能反過來提供給設計和製造端有用的信息,從而使得後者有效地分析失效模式,改善設計和製造良率。

測試的各種

對於芯片來説,有兩種類型的測試,抽樣測試和生產全測。

抽樣測試,比如設計過程中的驗證測試,芯片可靠性測試,芯片特性測試等等,這些都是抽測,主要目的是為了驗證芯片是否符合設計目標,比如驗證測試就是從功能方面來驗證是否符合設計目標,可靠性測試是確認最終芯片的壽命以及是否對環境有一定的魯棒性,而特性測試測試驗證設計的冗餘度。

這裏我們主要想跟大家分享一下生產全測的測試,這種是需要100%全測的,這種測試就是把缺陷挑出來,分離壞品和好品的過程。這種測試在芯片的價值鏈中按照不同階段又分成晶圓測試和最終測試(FT,也叫封裝測試或者成品測試),就是上面圖(1)中的紅色部分。

測試相關的各種名詞:

ATEAutomatic Test Equipment,自動化測試設備,是一個高性能計算機控制的設備的集合,可以實現自動化的測試。

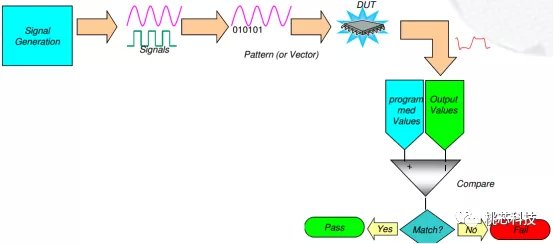

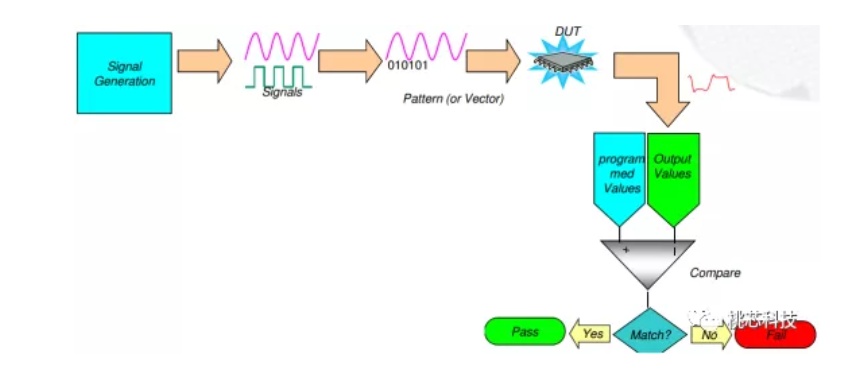

Tester---------測試機,是由電子系統組成,這些系統產生信號,建立適當的測試模式,正確地按順序設置,然後使用它們來驅動芯片本身,並抓取芯片的輸出反饋,或者進行記錄,或者和測試機中預期的反饋進行比較,從而判斷好品和壞品。

Test Program---測試程序,測試機通過執行一組稱為測試程序的指令來控制測試硬件

DUTDevice Under Test,等待測試的器件,我們統稱已經放在測試系統中,等待測試的器件為DUT。

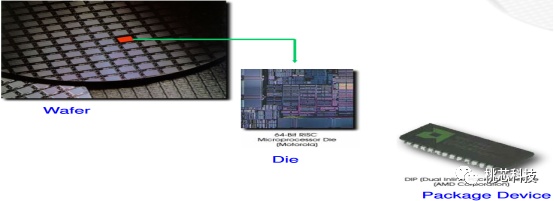

晶圓、單顆die和封裝的芯片----如下面圖(3)所示

Wafer就是晶圓,這個由Fab進行生產,上面規則地放着芯片(die),根據die的具體面積,一張晶圓上可以放數百數千甚至數萬顆芯片(die)。

Package Device就是封裝好的芯片,根據最終應用的需求,有很多種形式,這個部分由芯片產業價值鏈中的封裝工廠進行完成。

測試系統的基本工作機制:

對測試機進行編寫程序,從而使得測試機產生任何類型的信號,多個信號一起組成測試模式或測試向量,在時間軸的某一點上向DUT施加一個測試向量,將DUT產生的輸出反饋輸入測試機的儀器中測量其參數,把測量結果與存儲在測試機中的“編程值”進行比較,如果測量結果在可接受公差範圍內匹配測試機中的“編程值”,那麼這顆DUT就會被認為是好品,反之則是壞品,按照其失效的種類進行記錄。

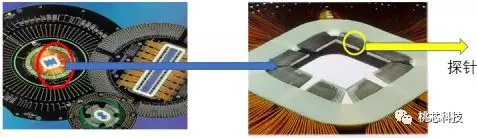

晶圓測試(wafer test,或者CP-chip probering):

就是在圖(3)中的晶圓上直接進行測試,下面圖中就是一個完整的晶圓測試自動化系統。

Prober--- 與Tester分離的一種機械設備,主要的作用是承載wafer,並且讓wafer內的一顆die的每個bond pads都能連接到probe card的探針上,並且在測試後,移開之前的接觸,同時移動wafer,換另外的die再一次連接到probe card的探針上,並記錄每顆die的測試結果。

當 probe card 的探針正確接觸wafer內一顆 die的每個bond pads後, 送出start信號通過Interface給tester開始測試, tester完成測試送回分類訊號 ( End of test) 給Prober, 量產時必須 tester 與 prober 做連接(docking) 才能測試。

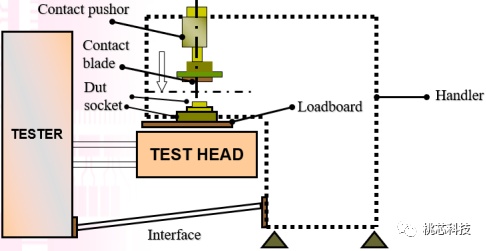

最終測試(FT,或者封裝測試):

就是在圖(3)中的Package Device上進行測試.下圖就是一個完整的FT的測試系統。對比wafer test,其中硬件部分,prober換成了handler,其作用是一樣的,handler的主要作用是機械手臂,抓取DUT,放在測試區域,由tester對其進行測試,然後handler再根據tester的測試結果,抓取DUT放到相應的區域,比如好品區,比如壞品1類區,壞品2類區等。

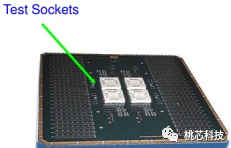

而probe card則換成了load board,其作用是類似的,但是需要注意的是load board上需要加上一個器件—Socket,這個是放置package device用的,每個不同的package種類都需要不同的socket,如下面圖(7)所示,load board上的四個白色的器件就是socket。

Handler 必須與 tester 相結合(此動作叫 mount 機)及接上interface才能測試, 動作為handler的手臂將DUT放入socket,然後 contact pusher下壓, 使 DUT的腳正確與 socket 接觸後, 送出start 訊號, 透過 interface 給 tester, 測試完後, tester 送回 binning 及EOT 訊號; handler做分類動作。

如何進行一個產品的測試開發

**各種規格書:**通常有三種規格書,設計規格書、測試規格書、產品規格書。

設計規格書,是一種包含新電路設計的預期功能和性能特性的定義的文檔,這個需要在設計項目啓動階段就要完成,通常由市場和設計人員共同完成,最終設計出來的產品的實際功能和性能需要和設計規格書的規定進行比較,以確認本次設計項目的完成度。

測試規格書,其中包含詳細的逐步測試程序、條件、方法,以充分測試電路,通常由設計人員和產品驗證工程師在設計過程中完成。

產品規格書,通常就是叫做datasheet,由設計公司對外發布的,包含了各種詳細的規格、電壓、電流、時序等信息。

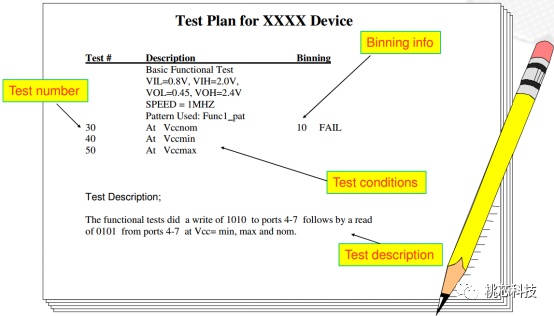

測試計劃書:就是test plan,需要仔細研究產品規格書,根據產品規格書來書寫測試計劃書,具體的需要包含下面這些信息:

a)DUT的信息,具體的每個pad或者pin的信息,CP測試需要明確每個bond pads的座標及類型信息,FT測試需要明確封裝類型及每個pin的類型信息。

b)測試機要求,測試機的資源需求,比如電源數量需求、程序的編寫環境、各種信號資源數量、精度如何這些,還需要了解對應的測試工廠中這種測試機的數量及產能,測試機費用這些。

c)各種硬件信息,比如CP中的probe card, FT中的load board的設計要求,跟測試機的各種信號資源的接口。

d)芯片參數測試規範,具體的測試參數,每個測試項的測試條件及參數規格,這個主要根據datasheet中的規範來確認。類型與下面圖(8)這樣

e)測試項目開發計劃,規定了具體的細節以及預期完成日期,做到整個項目的可控制性和效率。

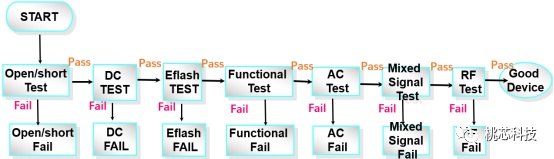

**測試項目流程:**桃芯科技目前量產的是BLE的SOC產品,裏面包含了eflash、AD/DA、 LDO/BUCK、RF等很多模塊,為了提供給客户高品質的產品,我們針對每個模塊都有詳細的測試,下面圖(9)是我們的大概的項目測試流程:

Open/Short Test: 檢查芯片引腳中是否有開路或短路。

DC TEST: 驗證器件直流電流和電壓參數

Eflash TEST: 測試內嵌flash的功能及性能,包含讀寫擦除動作及功耗和速度等各種參數。

Function TEST: 測試芯片的邏輯功能。

AC Test: 驗證交流規格,包括交流輸出信號的質量和信號時序參數。

Mixed Signal Test: 驗證DUT數模混合電路的功能及性能參數。

RF Test: 測試芯片裏面RF模塊的功能及性能參數。

上面我們給大家介紹了芯片的測試目的,原理,以及方法和流程,接下來我們將比較詳細的給大家介紹芯片的錯誤類型,對應的測試策略,以及跟芯片整體質量相關的一些具體測試方法。

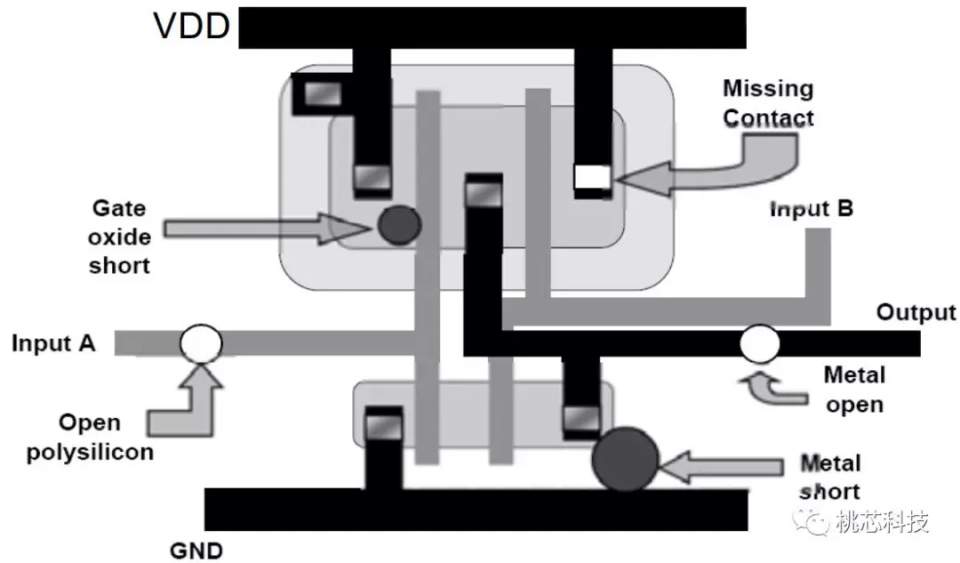

半導體芯片的defects、Faults

芯片在製造過程中,會出現很多種不同類型的defects,比如柵氧層針孔、擴散工藝造成的各種橋接、各種預期外的高阻態、寄生電容電阻造成的延遲等等,如下面圖(1)所示,大概展示了各種基本的defects。

這些defects單獨、或者組合一起,造成了電路的表現不符預期,這就是造成了Faults.而且各種Faults的表現也是不一樣的:

永久的Faults,就是徹底的壞品,各種不同的條件下都會表現出來,易於測試發現。

間或的Faults,時有發生的不符合預期,不是總能發現,需要一定的外部條件刺激。

偶然的Faults,只是偶然的,在特定的外部硬件或者工作模式條件下才表現出來。

可靠性問題的Faults,這種一般不會表現出來,只會在一些極端條件才會表現出來,比如高低温或者偏壓情況下。

為了更有效地檢測出各種faults、避免浪費更多芯片的資源、節省費用,業界定義了很多種Faults Model,並提供了各種測試方法論。

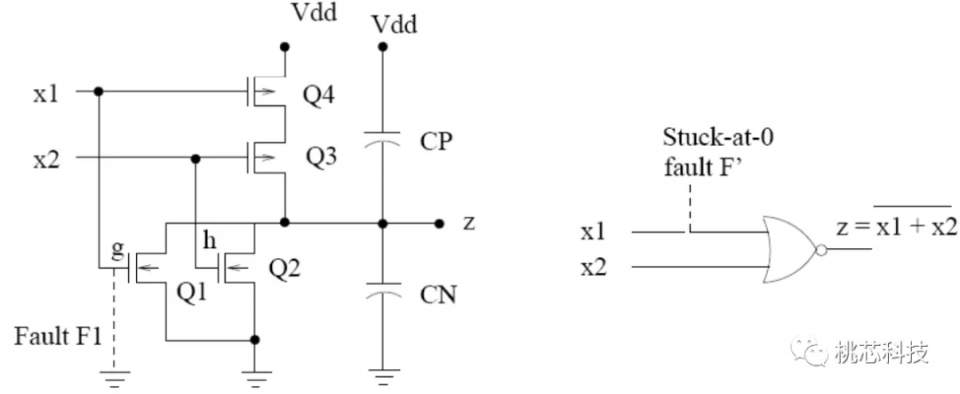

Stuck At Faults

工藝製造過程中造成的硬件defects,使得某個節點Stuck At 0或者Stuck At 1, 如下面圖(2)所示的一個或非門:輸入節點x1發生了Stuck At 0的defect; x1和x2輸入了00時候,Q1和Q2斷開,Q3和Q4導通, z輸出為H,正確;x1和x2輸入了01時候,Q1和Q3斷開,Q2和Q4導通, z輸出為L,正確;x1和x2輸入了10時候,此時x1被Stuck At 0了,等同於輸入00,結果還是Q1和Q2斷開,Q3和Q4導通,z輸出為H,錯誤;至此,通過輸入00,01,10就發現了這個defect。這種順序輸入00,01,10,而比較z輸出的結果與預期的值進行判斷的方法,就是所謂的Function測試。

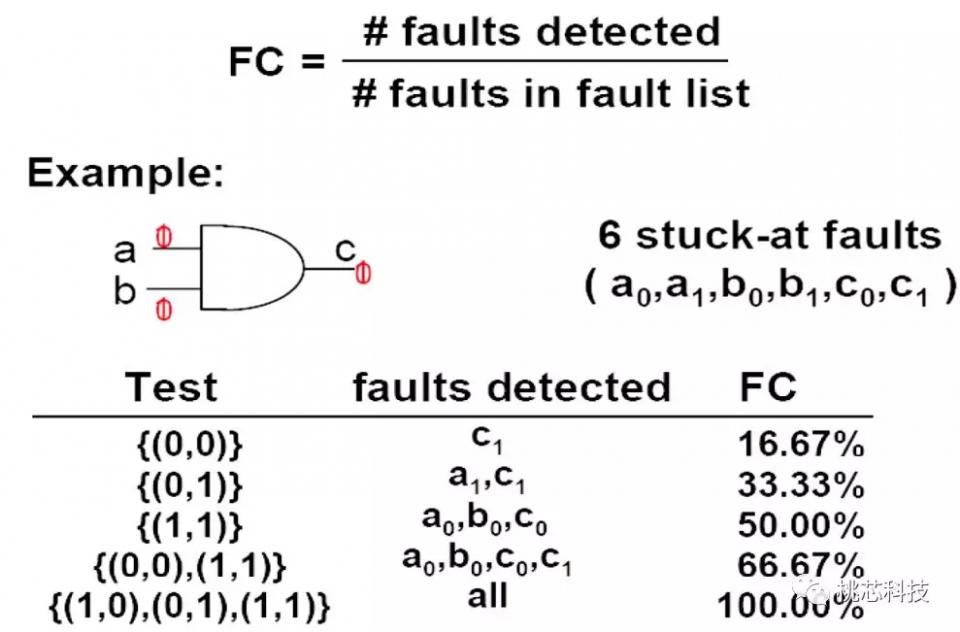

那對於一個電路,需要生成多少pattern,能達到多少的測試覆蓋率呢?下面圖(3)就以一個與門為例,説一下生產測試向量及計算測試覆蓋率的基本理念。

如上面圖示,一個與門,有三個節點a、b、c, 每個節點都有兩種fault的情況(Stuck At 0或者1),那麼一共就有6種stuck-at faults情況:a0,a1,b0,b1,c0,c1.

那麼如上面圖中列出的,需要輸入(1,0),(0,1),(1,1)可以完全測試出所有的6種可能的Stuck-at Faults的情況,測試覆蓋率為:可以發現的faults/所有可能的Faults,上面的輸入的測試覆蓋率為100%。

Stuck Open(off)/Short(on) Faults

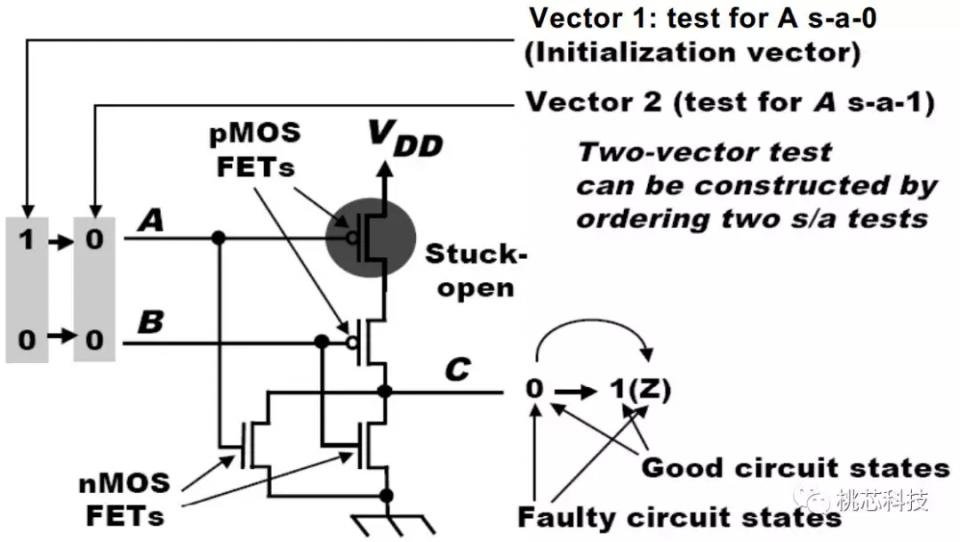

製造過程種造成的晶體管的defects,使得某個晶體管常開或者常閉了,如下面圖(4)所示的時一個晶體管發生了Stuck Open(off)的錯誤了。

如上圖,這種Stuck open可以用兩組Stuck At的向量進行測試,AB輸入從10變換到00,可以檢測出這種Stuck Open的fault,也就是説大部分的Stuck Open/Short的faults都是可以通過Stuck At model的測試向量覆蓋的。

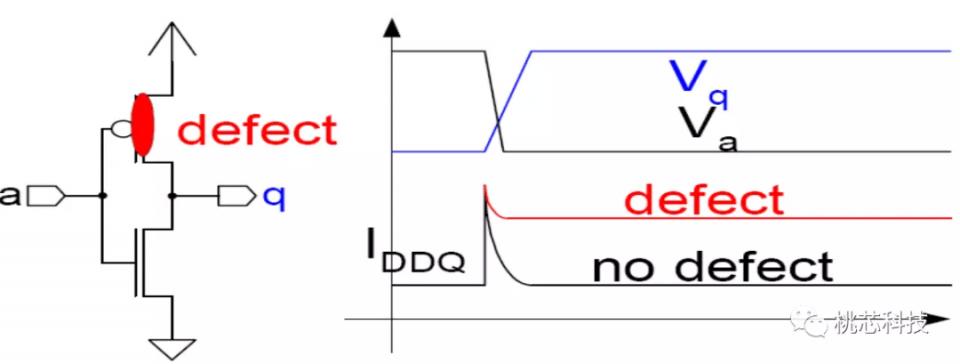

這種通過向量(function)的方式來測試Stuck Open/short,可能需要非常多的測試圖形,需要的測試時間和成本都很多。還有一種測量電流的方式,也可以有效的測試一些這種Stuck open/short的faults,但是會節省很多測試時間和測試成本。

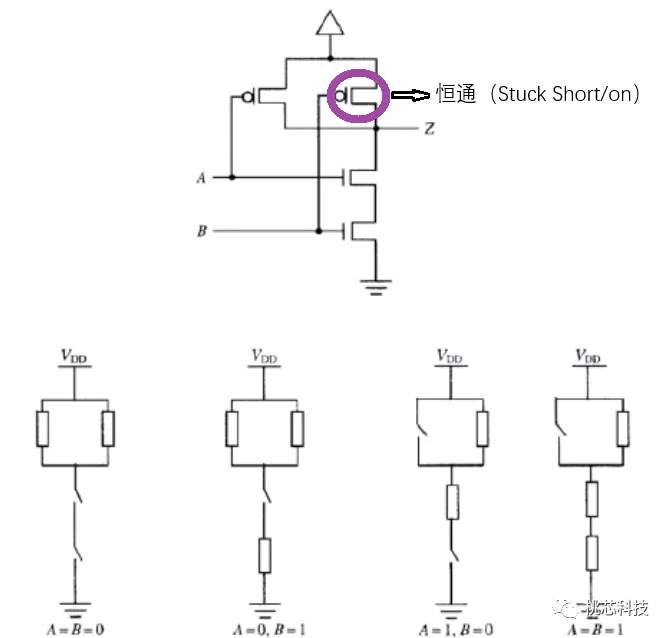

如下面圖(5)上半部分所示,右邊的那個P溝道MOS管發生了Stuck short(on)的faults,圖的下半部分展示了輸入AB的四種不同的情況,當AB輸入為00時,看起來這個晶體管表現的正常;但是當AB輸入為11時,地和電源間存在一個直接導通的電路,輸出端Z的狀態是異常的。

此時VDD上的漏電比較大,也可以通過測量VDD上面的電流來判斷正誤,即IDDQ的測試方法,後面會詳細的介紹這種方法。

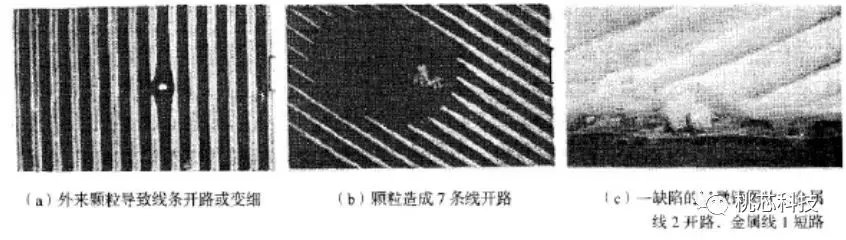

橋接(Bridge Faults)

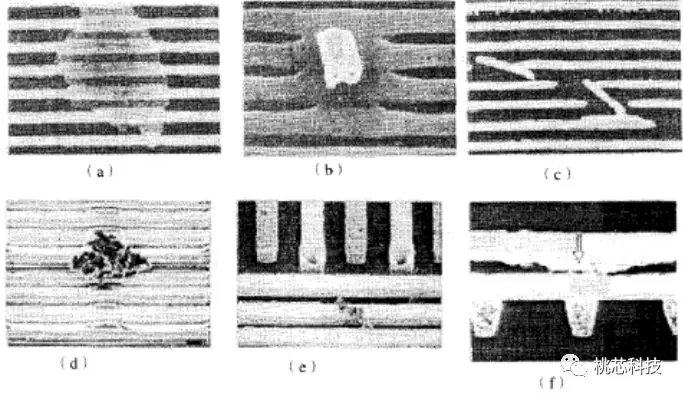

橋接缺陷是由於電路中兩個或多個電節點之間短路造成的,而設計中並未設計這種短接。這些短接的節點可能是某一個晶體管的,也可能是幾個晶體管之間的,可能處於芯片上同一層,也可能處於不同層。下面圖(6)是橋接缺陷的幾種圖例。

上圖中,(a)是因曝光不足導致7條金屬線橋接子在一起的情形;(b)是外來顆粒的介入導致4條金屬線橋接在一起的情形;(c)是因掩模劃傷導致橋接的情形;(d)是1um大小的缺陷造成短路的情形;(e)是金屬化缺陷導致2條金屬線橋接的情形;(f)則是層間短路情形。上述情形中雖然導致缺陷的原因各有不同,但結果都是橋接。

同樣的,橋接測試也可以通過電壓的方法完成,即run pattern方式,也就是stuck at的模式進行檢測,但是電流測試是發現電壓測試無法檢查的故障的有效方法。

下面圖(7)表示的是mos管的source和drain橋接了。

上面圖中,因為上面的P溝通的MOS管的source和drain橋接了,電源VDD上會有很大的漏電,用電流測試方法,可以很快發現問題。

開路故障(Open)

開路缺陷是製造工藝不當造成的,物理缺陷中大約40%屬於開路缺陷。典型的開路缺陷包括線條斷開、線條變細、阻性開路和漸變開路等。如下面圖(8)所示:

圖中(a)和(b)是電路存在開路的情形,(c)則是造成同時開路和短路缺陷的情形。

開路缺陷的形式取決於缺陷的位置及大小。例如,對於柵極開路(一般稱為浮柵,floating gate)這種缺陷,在缺陷面積小的情況下,隧道電流仍可流動,但信號的上升和下降時間增加;在缺陷面積大的情況下,輸入信號就在柵極形成耦合,形成的浮柵就獲得偏壓,此電壓可能導致晶體管導通,因此開路故障是否可檢測,取決於缺陷的面積和位置。

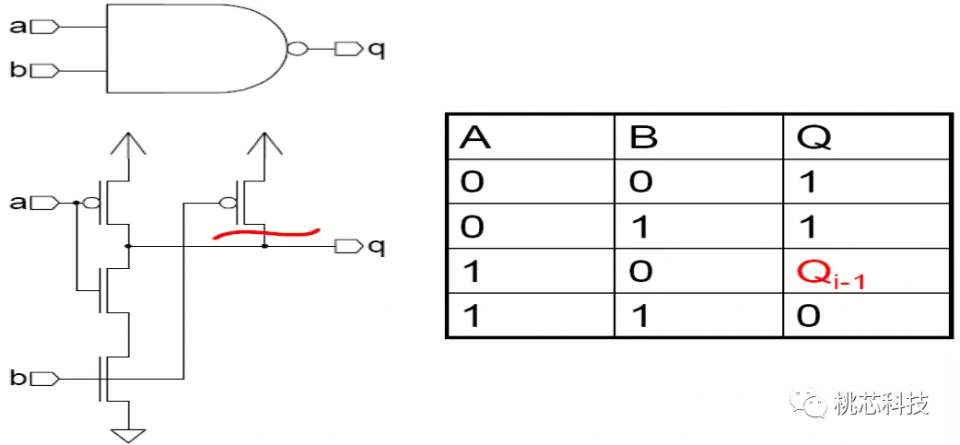

開路缺陷不一定都可以用Stuck At的模式檢測到,如下面圖(9)所示:

上圖中,紅線部分表示那個mos管的drain與輸出開路了,當順序輸入ab為00、01、10、11,從01變換為10的時候,輸出Q保持了上面一個狀態1,看起來還是正常的,這種情況下,就沒有檢測出來這個fault。但是如果調整一下輸入的向量的順序為00、01、11、10,就可以發現這個fault。

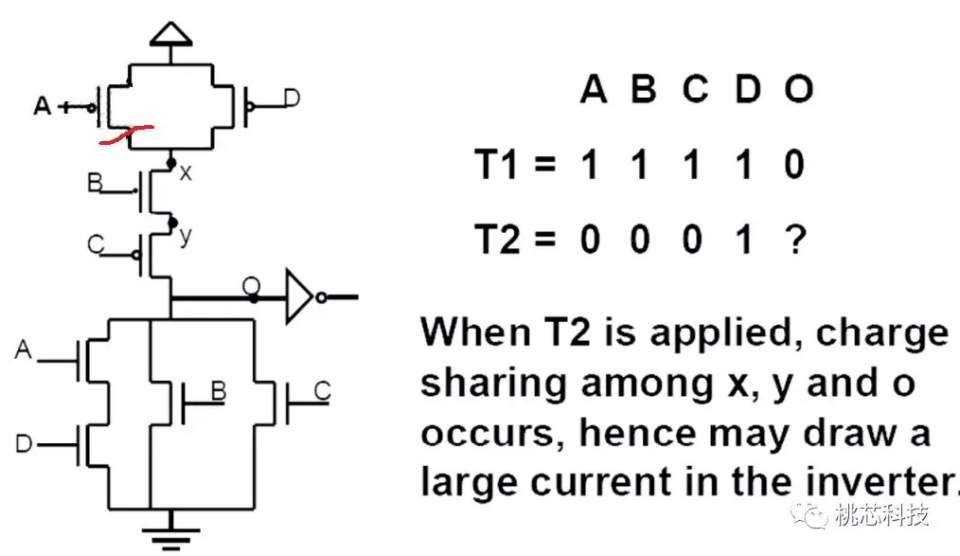

通過IDD的測試方法,也可以測試出一些open缺陷,如下面的圖(10)所示

上面紅色表示open的缺陷,當輸入ABCD為1111時,輸出O為0,當輸出轉為0001時候,在x、y和o之間出現了充放電,會有大電流出現。

延遲缺陷(delay faults)

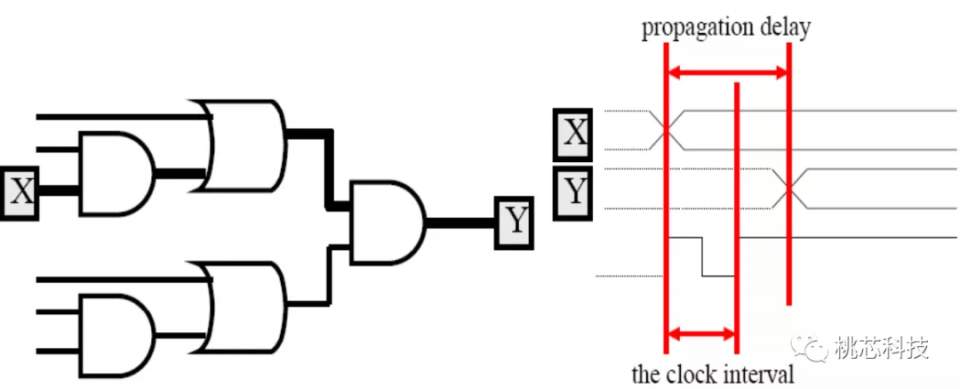

在一些高速芯片應用中,延遲缺陷特別重要,這種缺陷有很多原因,比如小面積的open導致某段線路的阻值偏大。如下面圖(11)所示:

這個path的delay已經超過了一個clock的間隙,通過stuck At的測試方式,可以檢測到這個缺陷。但是有的時候,延遲沒有超過clock的間隙,就會造成潛在的失效,在某些情況下,比如硬件變化、外界温度變化等,延遲超過clock的間隙,導致缺陷。這種延遲缺陷,可以通過AC測試的方法進行補充,比如測試上升沿的時間、下降沿的時間等等。

Pattern向量測試及IDDQ測試方法

上面給大家介紹了一下各種失效模式及測試原理。通過Pattern向量測試,加以電流測試為補充,可以有效地測試各種faults。

Pattern向量測試的方法

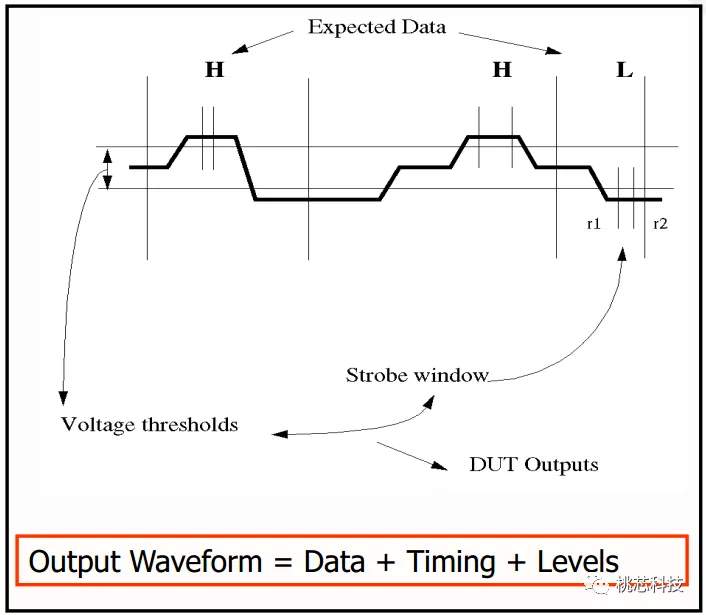

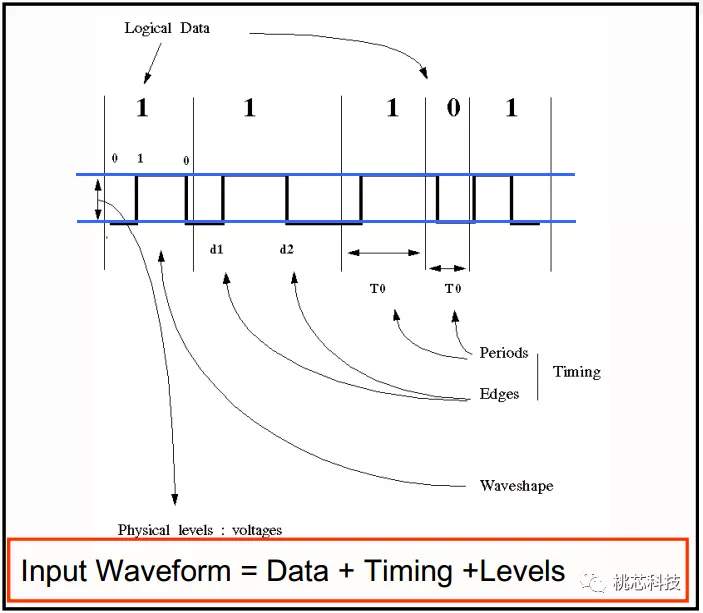

設計人員對某種fault模型進行仿真,給出波形向量,通常是VCD格式或者WGL格式,測試人員需要結合時序、電平和邏輯,進行編程,來對芯片輸入向量,以檢測輸出。如下面圖(12)表示的就是測試機force給芯片的一段波形。

而芯片在接受到這段輸入的波形後,運行特定的邏輯,輸出波形如下面圖(13),測試機需要在指定的strobe window進行比較輸出的與預期的邏輯值的情況,以此來判斷DUT是否邏輯功能正常。