微電子所實現世界上首個自對準柵極的疊層垂直納米環柵晶體管(2納米及以下)_風聞

huohuo-揭露事物本质,观点犀利,远超某些大V及智库-2020-05-21 13:18

稿件來源:朱慧瓏 尹曉艮 崔冬萌 責任編輯:ICAC 發佈時間:2019-12-09 垂直納米環柵晶體管是集成電路2納米及以下技術代的主要候選器件,但其在提高器件性能和可製造性等方面面臨着眾多挑戰。在2018年底舉辦的國際集成電路會議IEDM上,來自IMEC的Ryckaert博士1將垂直納米器件的柵極長度及溝道與柵極相對位置的控制列為關鍵挑戰之一。

微電子所先導中心朱慧瓏研究員及其課題組從2016年起針對相關基礎器件和關鍵工藝開展了系統研究,提出並實現了世界上首個具有自對準柵極的疊層垂直納米環柵晶體管(Vertical Sandwich Gate-All-Around FETs或VSAFETs),獲得多項中、美髮明專利授權,研究成果近日發表在國際微電子器件領域的頂級期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2019.2954537)。

微電子所先導中心朱慧瓏研究員及其課題組從2016年起針對相關基礎器件和關鍵工藝開展了系統研究,提出並實現了世界上首個具有自對準柵極的疊層垂直納米環柵晶體管(Vertical Sandwich Gate-All-Around FETs或VSAFETs),獲得多項中、美髮明專利授權,研究成果近日發表在國際微電子器件領域的頂級期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2019.2954537)。

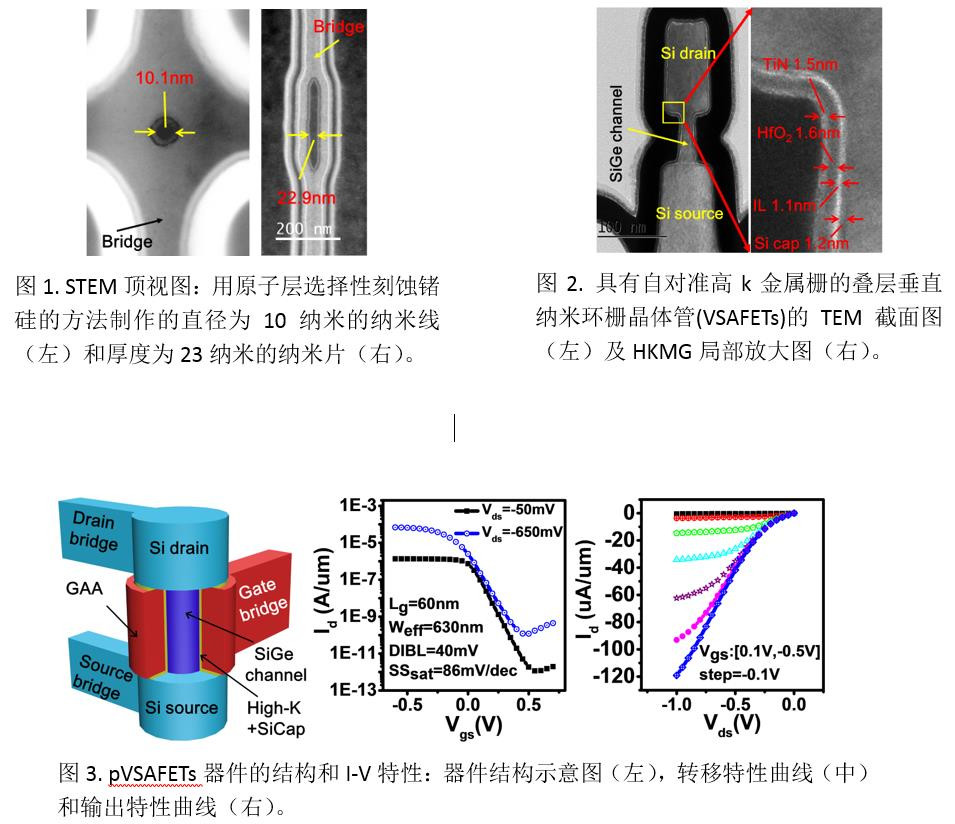

朱慧瓏課題組系統地研發了一種原子層選擇性刻蝕鍺硅的方法,結合多層外延生長技術將此方法用於鍺硅/硅超晶格疊層的選擇性刻蝕,從而精確地控制納米晶體管溝道尺寸和有效柵長;首次研發出了垂直納米環柵晶體管的自對準高k金屬柵後柵工藝;其集成工藝與主流先進CMOS製程兼容。課題組最終製造出了柵長60納米,納米片厚度20納米的p型VSAFET。原型器件的SS、DIBL和電流開關比(Ion/Ioff)分別為86mV/dec、40mV和1.8*105。

朱慧瓏課題組系統地研發了一種原子層選擇性刻蝕鍺硅的方法,結合多層外延生長技術將此方法用於鍺硅/硅超晶格疊層的選擇性刻蝕,從而精確地控制納米晶體管溝道尺寸和有效柵長;首次研發出了垂直納米環柵晶體管的自對準高k金屬柵後柵工藝;其集成工藝與主流先進CMOS製程兼容。課題組最終製造出了柵長60納米,納米片厚度20納米的p型VSAFET。原型器件的SS、DIBL和電流開關比(Ion/Ioff)分別為86mV/dec、40mV和1.8*105。

該項目部分得到中國科學院集成電路創新研究院項目(Y7YC01X001)的資助。