碳納米管能否拯救摩爾定律?_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2020-06-19 10:40

來源:內容由半導體行業觀察(ID:icbank)原創,作者:李飛,謝謝。

編者按:

近年來,因為製程工藝的演進,傳統硅材料的極限開始凸顯。為此產業界在尋找新的替代者,並且有了很多方案。在本文,我們試淺談一下最近比較火熱的碳納米管的前景。

硅基晶體管的極限與碳納米管的優勢

隨着半導體特徵尺寸的逐漸縮小,硅基半導體晶體管正在越來越接近物理極限。隨着硅基晶體管逐漸接近極限,各種生產問題正在一一浮現。首先,CMOS晶體管在溝道尺寸很短時,使用普通的平面工藝會造成漏電流(leakage current)非常大,這就造成了芯片待機功耗的問題。為此,16nm以下節點的CMOS普遍使用立體結構,例如FinFET,而隨着溝道尺寸進一步降低,晶體管的結構也在變得越來越複雜,例如GAA等。這就造成了CMOS工藝在小的特徵尺寸下無論是製備難度還是成本都在快速上升。除此之外,我們看到CMOS工藝在特徵尺寸進一步縮小(小於10nm)的時候,晶體管的性能並沒有相應提升,因此如何獲得高性能和高能效比晶體管就成了半導體業界的重要訴求。

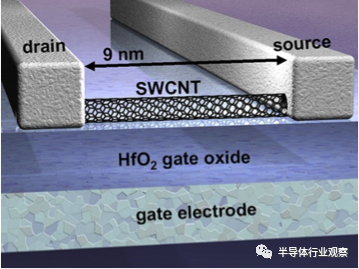

碳納米管晶體管的電氣功能和CMOS 晶體管很接近,同樣都有柵、源、漏極,其溝道則是由碳納米管構成。與CMOS晶體管類似,通過在碳納米管的柵源漏極加電壓可以改變碳納米管的電流,從而形成電路。

碳納米管正在走向量產

碳納米管從提出至今已經有數十年的歷史,而碳納米管真正走向量產是最近五年的事情。

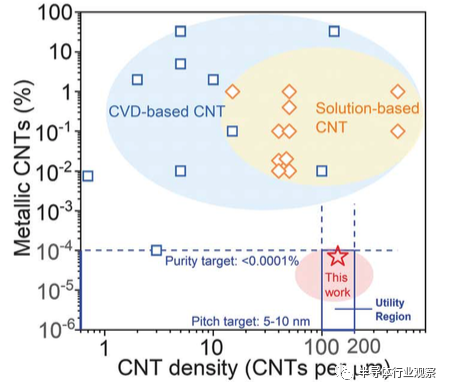

碳納米管的量產存在兩大挑戰,第一是如何在單位面積上製備高密度的碳納米管,第二是如何保證純度。其中的碳納米管純度是指,在生長碳納米管的過程中,會出現部分器件並沒有真正成為碳納米管而是形成了金屬碳納米管,這些金屬碳納米管的電氣特性和真正的碳納米管並不一致,因此碳納米管制備過程中希望純度較高即金屬碳納米管的比例很低。今年五月底,北京大學彭練矛教授領導的發表在《科學》雜誌上的研究可以説是在高密度高純度碳納米管陣列製備方向上的一個重要里程碑。該研究首次同時實現了高密度(可達100-200碳納米管/微米)和高純度(99.9999%純度)的碳納米管陣列製備。該研究中的碳納米管溝道長度為165nm,其本徵延時可低至12.4ps,比起相似溝道長度的CMOS電路來説要低,這也證實了碳納米管晶體管的潛力。

除了我國的團隊之外,美國的科研機構在碳納米管領域也投入了很大精力。MIT的Max Shulaker教授的團隊的一系列工作也是推動碳納米管量產的重要里程碑。2019年,Shulaker團隊成功實現了由14000多個碳納米管晶體管實現的16位處理器,是當時集成度最高的碳納米管芯片。而在本月《自然·電子學》剛發表的論文中,Schulaker教授的團隊則將碳納米管的量產更進一步,和Analog Devices(ADI)以及SkyWater Technology合作成功地在商用Fab中在三塊晶元上製造了近兩百萬個碳納米管,其特徵尺寸接近130nm。在這篇論文中,Shulaker研究組提出了多項重要的新技術,可以大大縮短碳納米管的製備時間(從兩天時間縮短到了兩分鐘),同時其大規模製備的碳納米管陣列也具有相當好的一致性。這一研究可以大大縮短碳納米管的製造成本,這也將成為碳納米管商業化量產的重要里程碑。

碳納米管會在哪裏最先落地?

最近幾年間大規模量產碳納米管的研究正在推進碳納米管的量產和落地。但是,我們也應當看到,大規模碳納米管組成的邏輯電路真正追趕上CMOS電路可能還需要多年的時間。因此,我們認為,碳納米管第一個可能落地的方向或許是傳感器領域。在傳感器領域,碳納米管擁有一系列新穎的特性,在生物領域和化學傳感器領域可以實現高靈敏度的感知。目前,已經有不少研究組推出了碳納米管氣體傳感器(可以檢測各種氣體,例如氨氣、一氧化碳等)以及生化傳感器(可以感知葡萄糖、DNA等),在未來的安全、健康、環境等領域都可能有重要應用。而在碳納米管傳感器的後端則可以集成中小規模的碳納米管邏輯電路,從而可望實現在一種工藝上的全集成傳感器方案。碳納米管晶體管的高能效比也能幫助基於碳納米管的傳感器方案應用到低功耗應用中。

除了傳感器之外,大規模碳納米管一旦能實現,還有機會能為目前的處理器芯片帶來革命性變化。目前,處理器芯片往往都受制於內存牆問題,即和內存之間的互聯帶寬太低,限制了計算邏輯的效率。高級封裝技術中的堆疊技術(如TSV)可以部分解決這個問題——傳統的TSV 3DIC中,不同芯片堆疊在一起並使用TSV來實現互聯,而TSV互聯線的間距在10微米左右。這10微米的TSV互聯間隔則限制了互聯的數量。而如果用上碳納米管,則可以大大縮小這個互聯的間距,從而大大增加互聯密度並提升通信帶寬。傳統的芯片的製造過程是首先製造出有源區,然後在有源區的上方再做多層金屬互聯,每次完成一層金屬互聯後會在其上方沉積一層絕緣層,然後在絕緣層之上再次生長金屬互聯層。同時,在不同的金屬層之間可以通過金屬層間通孔來實現層間互聯。這些金屬通孔的間距可以低至幾十納米。而碳納米管也可以實現類似的方法,在底層標準CMOS有源區製造完成後,可以在絕緣層上面生長金屬和碳納米管或存儲器件(例如RRAM),相當於把碳納米管作為一層金屬互聯來生長。這樣一來,碳納米管和CMOS邏輯/存儲器件之間的互聯密度就可以從TSV的10微米級別下降到10納米數量級,即互聯密度可以提升一千倍,這就能大大緩解內存牆問題,從而進一步為計算架構帶來革命性變化。