深度解讀蘋果M1芯片_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2020-11-12 14:44

來源:本文由半導體行業觀察(ID:icbank)編譯自anandtech,謝謝。

昨天,蘋果發佈了他們全新的MacBook系列產品。這不是一個普通的發佈版本,如果説有什麼不同的話,蘋果今天所做的這一舉動是15年來從未發生過的:開始了整個消費類Mac系列的CPU架構轉型。

這個巨大的改變多虧了該公司在硬件和軟件上的垂直整合,除了蘋果公司,沒有人能夠如此迅速地引入。上一次蘋果公司在2006年進行這樣的嘗試時,放棄了IBM的PowerPC ISA和處理器,轉而支持英特爾x86設計。如今,英特爾正在被拋棄,蘋果轉而採用基於Arm-ISA的內部處理器和CPU微體系結構。

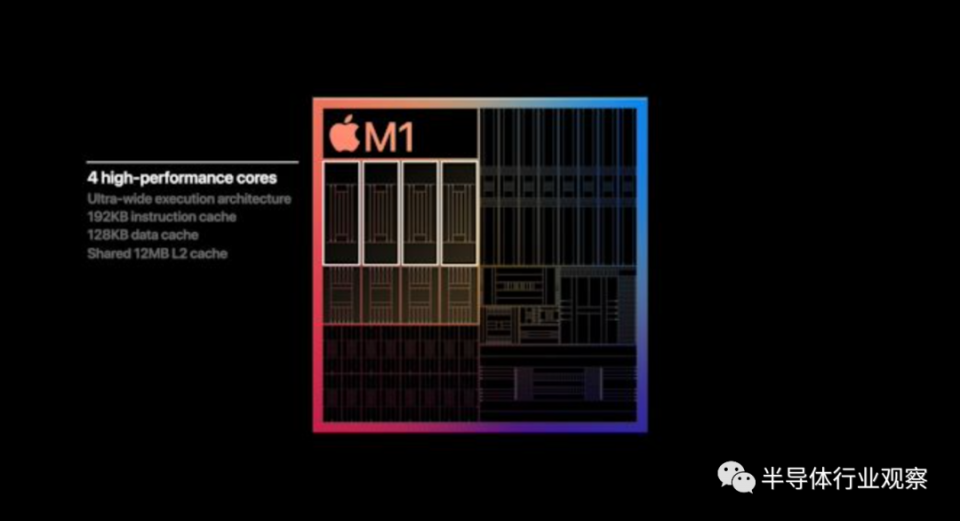

新處理器稱為Apple M1,這是該公司首款針對Mac設計的SoC。它具有四個大型性能內核,四個效率內核和一個8-GPU內核GPU,在5nm工藝節點上具有160億個晶體管。蘋果公司正在為這種新的處理器系列啓動新的SoC命名方案,但至少在理論上它看起來很像A14X。

今天的活動包含了許多新的官方公告,但也缺少(以典型的Apple方式)詳細信息。今天,我們將剖析新的Apple M1新聞,並基於已經發布的Apple A14 SoC進行微體系結構的深入研究。

Apple M1 SoC:適用於Mac的A14X

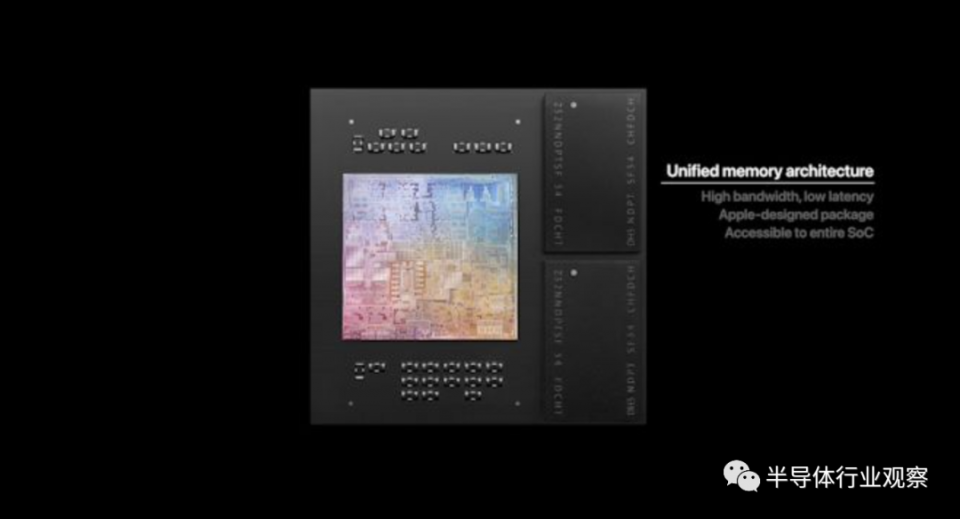

新款Apple M1確實是Apple進行新的重大旅程的開始。在蘋果公司的演講中,該公司並未在設計細節上透露太多,但是有一張幻燈片告訴了我們很多有關芯片的封裝和架構的信息:

這也意味着,我們幾乎可以肯定地看到新芯片上的128位DRAM總線,與上一代a-X芯片非常相似。

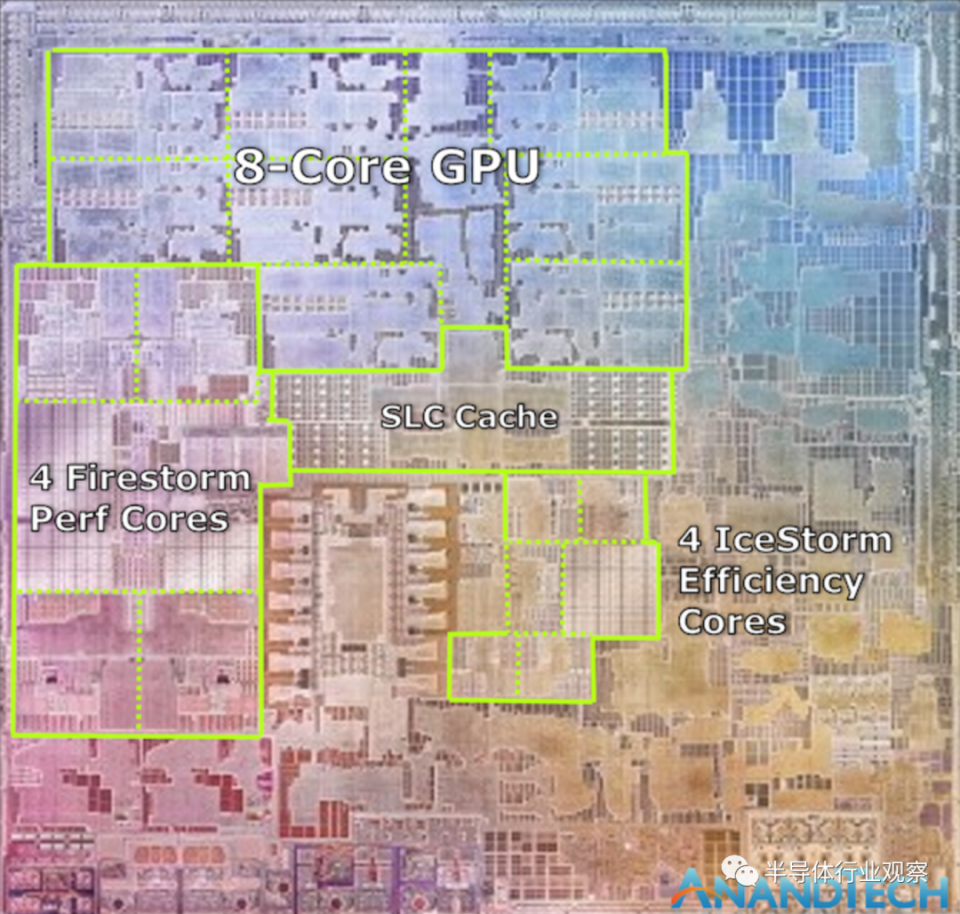

在同一張幻燈片上,蘋果似乎也使用了新M1芯片的實際裸片(die)鏡頭。它完全符合蘋果公司所描述的芯片特性,看起來就像一個真正的裸片照片。這可能是我做過的最快的裸片註釋了:

同時,在SoC中心附近找到了4個Icestorm效率核心,在上面,我們可以找到SoC的系統級緩存,該緩存在所有IP塊之間共享。

最後,8核的GPU佔據了大量的die space,並且位於這個die shot的上半部。

M1最有趣的地方是它與Intel和AMD其他CPU設計的比較。上述所有模塊仍然只覆蓋了整個裸片的一部分,並帶有大量的輔助IP。蘋果提到M1是一個真正的SoC,包括之前Mac筆記本電腦內部的幾個分立芯片的功能,比如I/O控制器和蘋果的SSD和安全控制器。

向Arm進軍

事實上,蘋果甚至可以如此無縫地完成一個重大的架構轉換,只是一個小小的奇蹟,畢竟蘋果在實現這一點上有着相當豐富的經驗。畢竟,這並不是蘋果第一次為他們的Mac電腦切換CPU架構。

在21世紀中期左右,這家長期經營的PowerPC公司走到了一個十字路口,當時負責PowerPC開發的Apple-IBM-Motorola(AIM)聯盟越來越難以進一步開發芯片。IBM的PowerPC970(G5)芯片在台式機上有着可觀的性能指標,但它的功耗卻相當可觀。這使得該芯片無法用於日益增長的筆記本電腦領域,蘋果仍在使用摩托羅拉的PowerPC 7400系列(G4)芯片,雖然該芯片的功耗確實更好,但其性能無法與英特爾的核心繫列處理器相媲美。

因此,蘋果打出了一張他們保留的牌:Marklar項目。利用Mac OS X及其底層Darwin內核的靈活性(與其他Unix一樣,達爾文內核設計為可移植),蘋果一直在維護Mac OS X的x86版本。儘管最初主要被認為是一種良好編碼實踐的練習,但要確保蘋果編寫的操作系統代碼沒有不必要的約束PowerPC及其big-endian內存模型——Marklar成為蘋果從停滯不前的PowerPC生態系統中退出的策略。該公司將改用x86處理器,尤其是英特爾的x86處理器,顛覆其軟件生態系統,同時也為更好的性能和新的客户機會敞開大門。

從所有指標來看,切換到x86都是Apple的一大勝利。英特爾的處理器提供的每瓦性能優於蘋果留下的PowerPC處理器,尤其是英特爾在2006年底推出Core 2(Conroe)系列處理器之後,英特爾就牢固地確立了自己在PC處理器領域的主導地位。最終,這奠定了蘋果在未來幾年的發展軌跡,使他們成為擁有筆記本超本(MacBook Air)和令人難以置信的MacBook Pro的筆記本電腦公司。同樣,x86具有Windows兼容性,引入了直接啓動Windows的功能,或者可以在開銷非常小的虛擬機中運行它。

至少在某種程度上,縮小了差距的是Rosetta,這是Apple用於x86的PowerPC轉換層。Rosetta允許大多數PPC Mac OS X應用程序在x86 Mac上運行,儘管性能有些過失(x86上的PPC並不是最簡單的事情),但是Intel CPU的更高性能有助於攜帶東西適用於大多數非密集型應用。最終,Rosetta對蘋果來説只是一個創可貼,而蘋果很快就撕毀了它;在2011年Mac OS X 10.7 (Lion)面世時,蘋果已經放棄了Rosetta。因此,即使有了Rosetta,蘋果公司也向開發者明確表示,如果他們想繼續銷售並讓用户滿意,他們希望他們為x86更新他們的應用程序。

最終,PowerPC向x86的轉變為現代、敏捷的蘋果定下了基調。從那時起,蘋果就創造了一整套快速發展的理念,並在他們認為合適的情況下改變事物,只在向後兼容性方面做了有限的考慮。這給了用户和開發者很少的選擇,只能享受這段旅程並跟上蘋果的發展趨勢。但它也給了蘋果提早推出新技術的能力,如果有必要的話,還可以打破舊的應用程序,這樣新功能就不會因為向後兼容的問題而受阻。

所有這些都是以前發生的,並且所有這些都會在下週蘋果發佈其首批基於Apple M1的Mac時再次發生。通用二進制文件又回來了,Rosetta又回來了,蘋果公司敦促開發人員在Arm上啓動並運行他們的應用程序已全面展開。從PPC到x86的過渡為Apple進行了ISA更改創建了模板,在成功過渡之後,隨着Apple成為自己的芯片供應商,他們將在接下來的幾年中再次進行此操作。

在接下來的頁面中,我們將研究A14的Firestorm內核,它也將在M1中使用,也會在iPhone芯片上做一些廣泛的基準測試,設定M1的最低標準:

蘋果龐大的CPU微體系結構

那麼蘋果打算如何在這個市場上與AMD和Intel競爭呢?過去幾年來一直在關注蘋果在硅技術方面的努力的讀者一定不會驚訝地看到蘋果在活動中宣稱的性能。

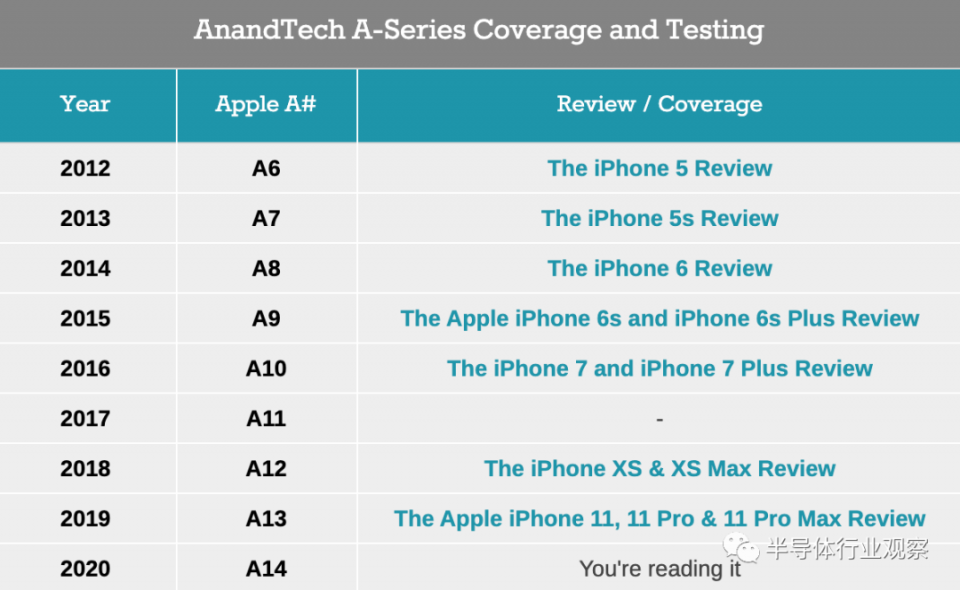

秘密之處在於蘋果公司內部的CPU微體系結構。蘋果在定製CPU微體系結構方面的漫長旅程始於2012年在iPhone 5中發佈的Apple A6。即使在那時,憑藉其第一代“ Swift”設計,與移動競爭對手相比,該公司的性能數據仍然令人印象深刻。

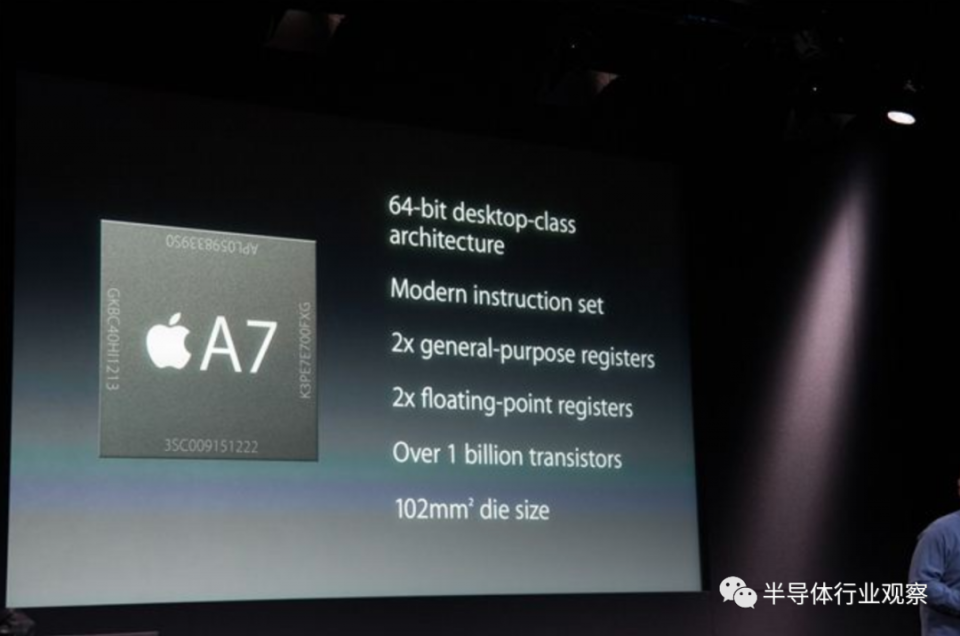

然而,真正在業界引起轟動的是蘋果隨後在2013年的Apple A7 SoC和iPhone 5S中發佈的Cyclone CPU微體系架構。蘋果早期採用的64位Armv8震驚了所有人,因為該公司是業界首個實施新指令集架構的公司,但他們甚至比Arm自己的CPU團隊早了一年多,因為Cortex-A57 (Arm自己的64位微架構設計)要到2014年底才問世。

考慮到蘋果沒有透露任何細節,蘋果的CPU在很大程度上仍然是一個黑匣子設計,而且關於此事的唯一公開資源可以追溯到A7旋風時代的LLVM補丁,這與今天的設計已經不再相關。雖然我們沒有官方的手段和信息來説明蘋果的CPU是如何工作的,但這並不意味着我們無法弄清楚設計的某些方面。然而,通過我們自己的內部測試以及第三方微基準測試(這是@Veedrac的微體系結構測試套件的一項特殊學分),我們可以公佈蘋果設計的一些細節。以下披露是基於測試iPhone 12 Pro中最新的Apple A14 SoC的行為得出的:

蘋果的Firestorm CPU核心:更大更大

蘋果最新一代A14內部的大核心CPU設計代號為“Firestorm”,延續了去年蘋果A13內部的“Lightning”微架構。今天討論的核心是新的Firestorm核心和它多年來不斷改進的血統,這也是蘋果如何從英特爾x86設計大幅跳躍到他們自己內部的SoC的關鍵部分。

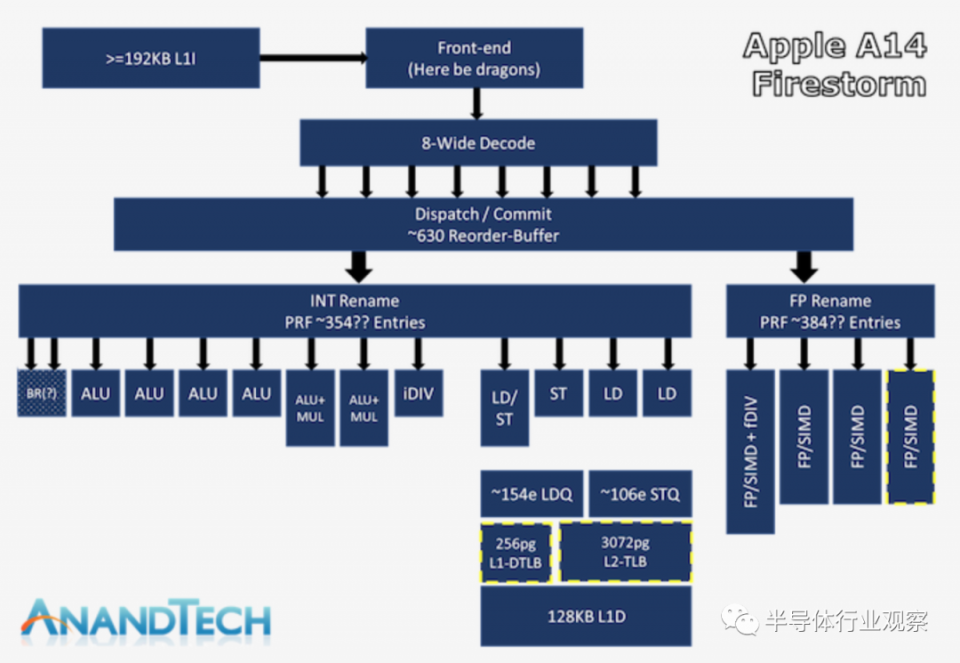

與業內其他設計相比,真正定義蘋果的Firestorm CPU核心的是其微架構的寬度。具有8-wide解碼塊,蘋果的Firestorm是目前行業中最廣泛的商業化設計。IBM即將在POWER10中推出的P10內核是唯一一個有望在市場上發佈的具有如此寬解碼器設計的官方設計,此前三星取消了他們自己的M6內核,後者也被描述為具有如此寬的設計。

今天的其他現代設計,例如AMD的Zen(1至3)和英特爾的µarch,x86 CPU仍僅採用4-wide解碼器設計,由於ISA固有的可變指令長度特性,目前似乎無法將其擴展到更大的範圍,與ARM ISA的固定長度指令相比,設計能夠處理體系結構方面的解碼器更加困難。在ARM方面,三星的設計從M3開始已經達到了6-wide,而Arm自己的Cortex內核隨着每一代的發展都在穩步擴大,目前在現有的硅片中達到4-wide,並且預計會增加到即將推出的Cortex-X1內核具有5-wide設計。

蘋果的微架構是8-wide實際上對新的A14來説並不新鮮。回到A13,似乎我在測試中犯了一個錯誤,因為我最初認為它是一台 7-wide機器。最近我對它進行了重新測試,證實蘋果正是在這一代升級了A11和12的7-wide解碼。

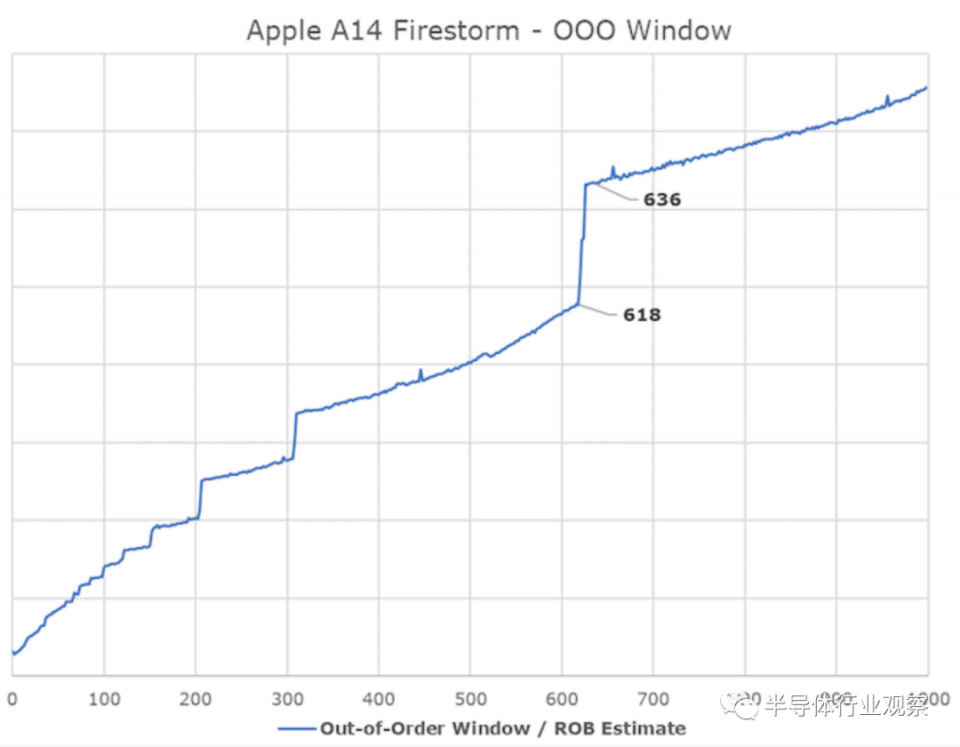

對於蘋果的新核心來説,A+-630 deep ROB是一個巨大的無序窗口,因為它遠遠超過了業內其他設計。英特爾的Sunny Cove和Willow Cove型內核是第二大“深”OOO設計,擁有352個ROB型架構,AMD最新的Zen3型內核有256個條目,最近的Arm設計如Cortex-X1有224個架構。

與業內其他設計師相比,蘋果是如何以及為什麼能夠實現如此不成比例的設計還不清楚,但這似乎是蘋果實現高指令水平並行的設計理念和方法的一個關鍵特徵。

很多很多的執行單位

擁有高ILP也意味着這些指令需要由機器並行執行,這裏我們還可以看到蘋果的後端執行引擎具有非常廣泛的功能。在整數方面,我們估計其在運行中的指令和重命名物理寄存器文件的容量大約為354個條目,我們找到了至少7個用於實際算術操作的執行端口。其中包括4個簡單的算術邏輯單元能夠加法指令,2個複雜的單元也具有MUL(乘法)功能,以及一個似乎是專用的整數除法單元。核心每個週期可以處理2個分支,我想這是由一個或兩個專用的分支轉發端口實現的,但我無法100%確認這裏的設計佈局。

這裏的Firestorm核心在整型設計方面似乎沒有重大變化,因為唯一值得注意的變化是該單元的整型除法延遲明顯略有增加(是的)。

在浮點和矢量執行方面,新的Firestorm內核實際上更令人印象深刻,因為蘋果增加了第四個執行管道,使其功能增加了33%。在這裏,FP重命名寄存器似乎有384個條目,這也是相當龐大的。因此,這四個128位的NEON管道在理論上可以與AMD和Intel的桌面內核的當前吞吐量相匹配,儘管它們的吞吐量更小。這裏的端點操作吞吐量與管道計數是1:1,這意味着Firestorm可以每循環執行4個FADD和4個FMUL,分別有3個和4個週期延遲。這是英特爾CPU和之前AMD CPU的四倍,也是最近的Zen3的兩倍,當然,仍然在較低的頻率運行。這可能是蘋果在瀏覽器基準測試中表現如此出色的原因之一(JavaScript數字是浮點雙精度數)。

這四個管道的向量能力似乎是相同的,唯一看到吞吐量較低的指令是在四個管道之一上的FP除法,倒數和平方根運算僅具有1的吞吐量。

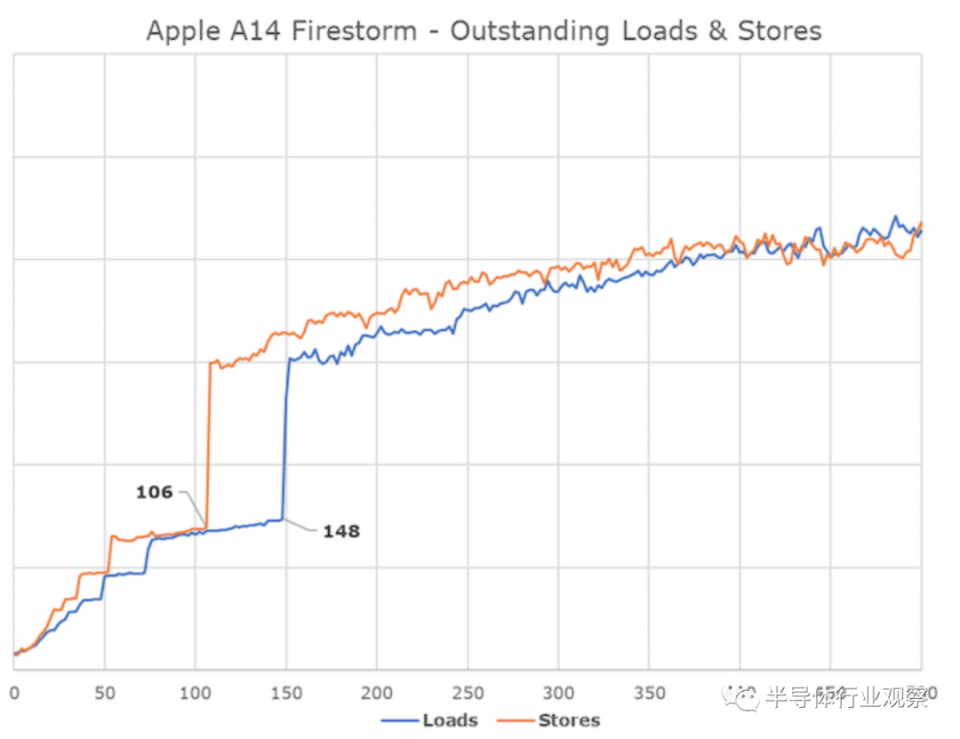

這裏有趣的是蘋果處理內存事務的深度。我們測量了大約148-154個未完成的負載和大約106個未完成的存儲,這應該是內存子系統的負載隊列和存儲隊列的等價數字。毫不奇怪,這也比市場上的任何其他微體系結構都要深入。相比之下,AMD的Zen3和英特爾的Sunny Cove分別為128/72和128/ 64。英特爾在這裏的設計與蘋果相差不遠,實際上這些最新的微架構的吞吐量是相對匹配的——如果蘋果將這種設計部署到非移動內存子系統和DRAM上,那將是很有趣的。

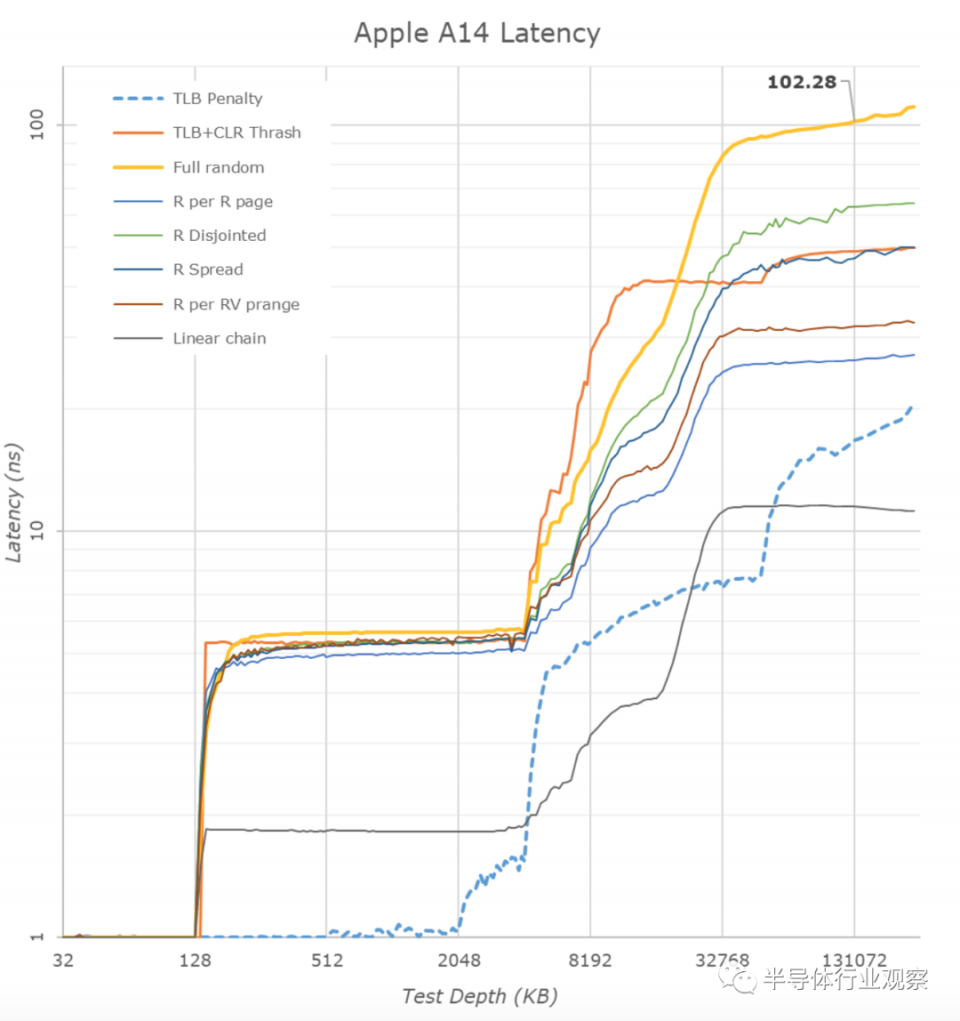

在這一代的Firestorm核心方面,最大的改進就是TLB。L1 TLB從128頁增加了一倍,達到256頁,L2 TLB從2048頁增加到3072頁。在當今的iPhone上,這是一個絕對過大的更改,因為頁面大小為16KB,這意味着L2 TLB覆蓋48MB,甚至超過了A14的緩存容量。隨着蘋果將微體系結構轉移到Mac系統上,與4KB頁面兼容並確保設計仍提供足夠的性能,這將成為蘋果為何選擇在這一代進行如此大規模升級的關鍵部分。

巨大的高速緩存似乎也非常快– L1D以3個週期的負載使用延遲進入。我們不知道這是否是如三星核心所描述的那樣巧妙的負載級聯,但是無論如何,對於如此大的結構來説,這是非常令人印象深刻的。AMD具有32KB的4週期緩存,而英特爾最新的Sunny Cove在將大小增加到48KB時看到了5週期的迴歸。慢頻或快頻設計的優缺點值得深思。

在L2方面,Apple一直採用兩個大核心共享的8MB結構。這是一個非常不尋常的緩存層次結構,與其他人使用的中間大小的私有L2和更大的較慢的L3形成對比。蘋果在這裏不理會規範,而是選擇大型而快速的L2。奇怪的是,這一代A14看到了大核的L2在訪問延遲方面進行了迴歸,從14個週期回到了16個週期,還原了A13所做的改進。我們不確定為什麼會發生這種情況,我確實看到標量工作負載有更高的並行訪問帶寬進入緩存,但是峯值帶寬似乎仍然與上一代相同。另一個假設是,由於Apple在內核之間共享L2,因此這可能是Apple Silicon SoC發生變化的指標,因為只有兩個以上的內核連接到單個緩存,這與A12X代很相似。

蘋果已經在其SoC上使用大型LLC了好幾代了。A14上,這似乎又是一個16MB的緩存,服務於SoC上的所有IP塊,當然對CPU和GPU最有用。相對而言,這種緩存層次結構並不像其他設計的實際CPU-cluster l3那麼快,而且近年來,我們看到越來越多的移動SoC供應商為了提高功率效率而在內存控制器前使用這種LLC。蘋果會在更大的筆記本或台式電腦芯片上做什麼還不清楚,但我認為我們會看到類似的設計。

我們已經討論了蘋果設計的更多具體方面,比如它們的MLP(內存級並行)功能,而A14在這方面似乎沒有改變。我注意到A13的另一個變化是,新的設計現在也利用了Arm更輕鬆的內存模型,它能夠自動優化流媒體存儲到非臨時存儲中,模仿Cortex-A76和Exynos-M4中引入的變化。從理論上講,x86設計無法實現類似的優化,如果有人嘗試這樣做,將非常有趣。

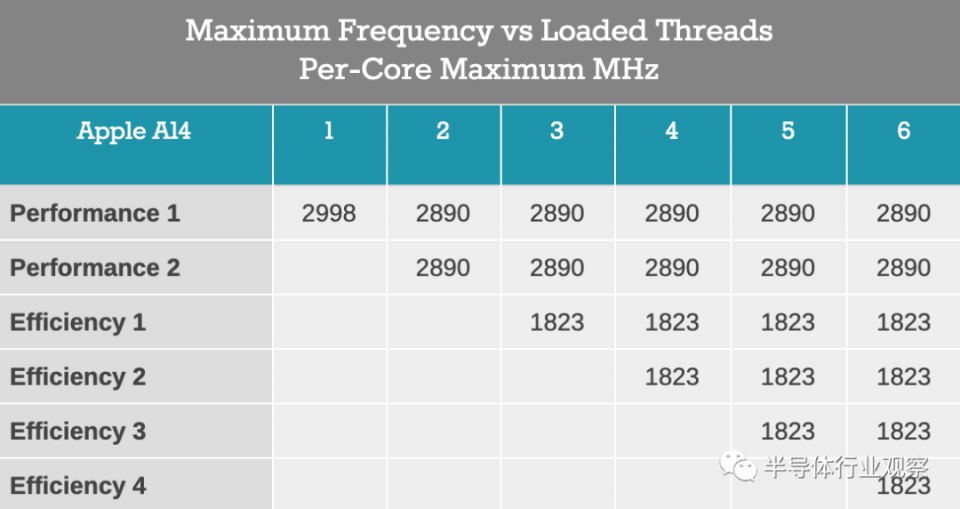

我們將稍後詳細研究功耗,但是我目前看到Apple受實際手機散熱的限制,而不是微體系結構的固有時鐘上限。新的Firestorm內核現在的時鐘速度與Arm上其他移動CPU微體系結構的速度大致相同,即使它的設計範圍更廣。因此,由於設計更加複雜而不得不降低時鐘速度的論點似乎也不適用於這個實例。蘋果不僅可以在筆記本電腦這樣的高温度封裝設備上做什麼,還可以在Mac這樣的壁掛式設備上做什麼,這將是一件非常有趣的事情。

主導移動性能

在我們深入探討x86與Apple Silicon的爭論之前,有必要更詳細地研究A14 Firestorm內核在A13 Lightning內核基礎上的改進方式,以及詳細介紹新芯片5nm工藝的功率和功率效率改進節點。

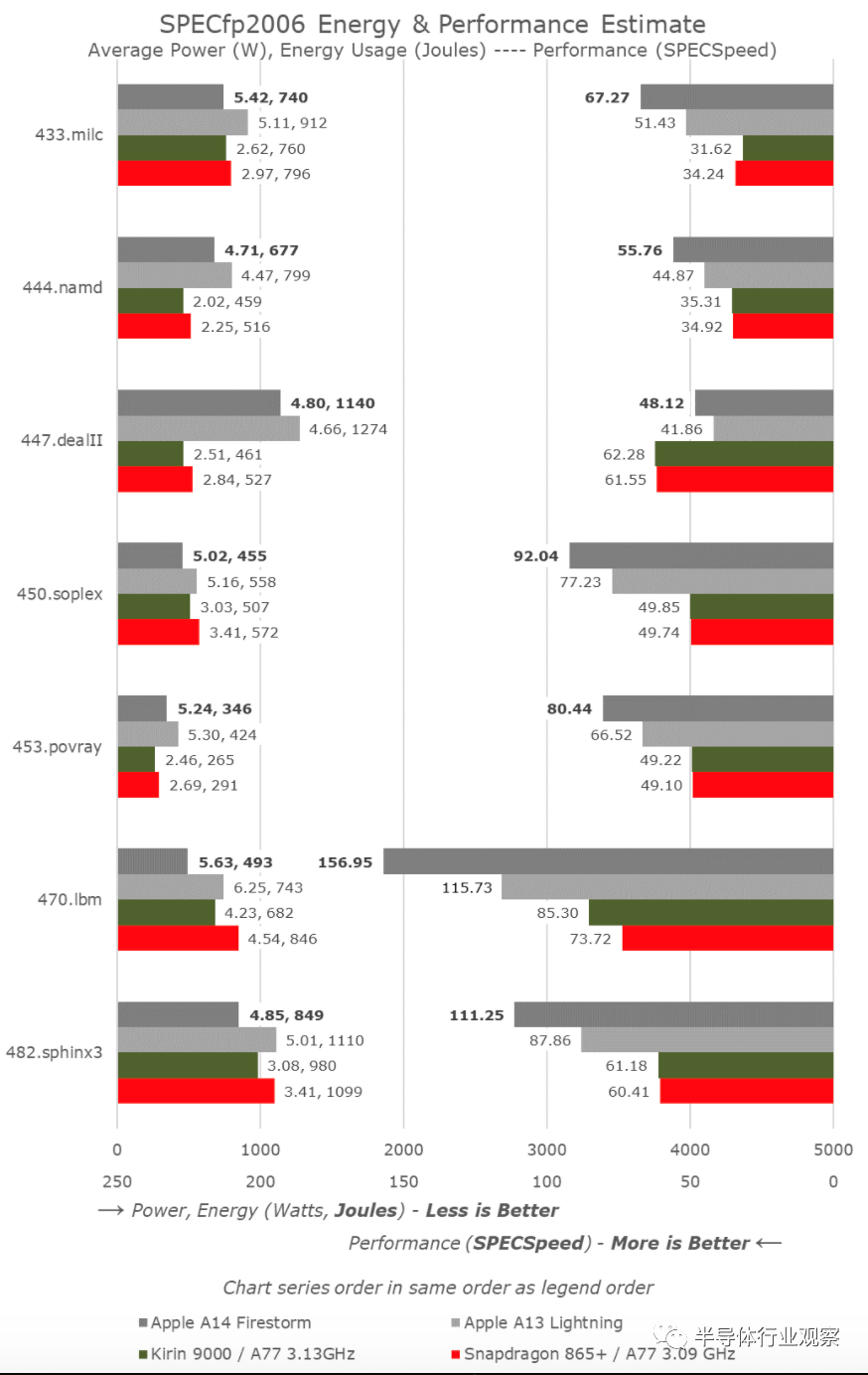

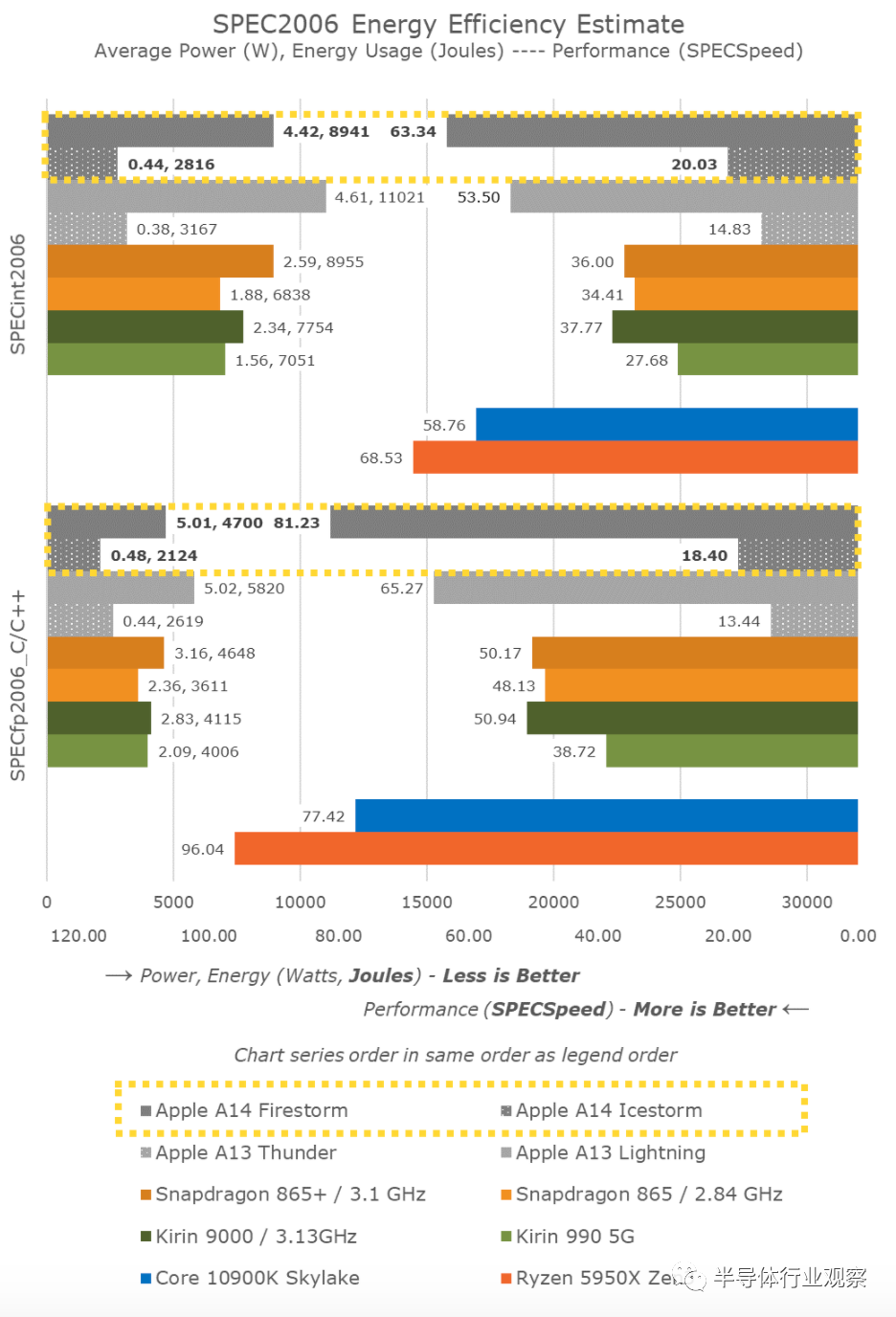

在這裏的比較中,流程節點實際上是一個通配碼,因為A14是市場上第一個5nm芯片組,緊隨其後的是華為Mate 40系列的麒麟9000。我們碰巧有設備和芯片在內部進行測試,對比一下麒麟9000(N5上的Cortex-A77 3.13GHz)和Snapdragon 865+(N7P上的Cortex-A77 3.09GHz),我們可以從某種程度上推斷出處理節點在功率和效率方面有多大影響,將這些改進轉化為A13與A14的比較。

從SPECint2006開始,我們沒有看到A14分數有什麼不尋常的,除了456的巨大進步。實際上,這並不是由於微架構的飛躍,而是由於Xcode 12中新的LLVM版本進行了新的優化。在這裏,編譯器似乎使用了類似於在GCC8上發現的循環優化。A13的分數實際上已經從47.79提高到了64.87,但我還沒有在整個套件上運行新的數字。

對於其餘的工作負載,A14通常看起來像一個相對於A13的線性進程,因為時鐘頻率從2.66GHz增加到3GHz。IPC的整體漲幅在5%左右,略低於蘋果的前幾代產品,不過時鐘速度的漲幅要大於通常的水平。

新芯片的功耗實際上是一致的,有時甚至比A13更好,這意味着這一代的工作負載能源效率已經看到了明顯的改善,即使在峯值性能點。

與當代的Android和以Cortex-core為核心的SoC相比,蘋果的性能似乎相當不平衡。最突出的一點是內存密集型、稀疏內存,其特點是工作負載(如429.mcf和471.omnetpp),蘋果的設計功能遠遠超過性能的兩倍,儘管所有芯片都運行着類似的移動級LPDDR4X/LPDDR5內存。在我們的微體系結構調查中,我們發現Apple設計上存在“記憶魔力”的跡象,我們可能會認為它們正在使用某種指針追隨預取機制。

還有非常重要的一點需要注意的是,蘋果在實現這一切的同時,還保持了扁平狀態,甚至降低了新芯片的功耗,顯著降低了相同工作負載下的能耗。

看看麒麟9000和Snapdragon 865+,我們發現功率在相對相似的性能下降低了10%。兩種芯片都使用相同的CPU IP,只是它們的處理節點和實現方式不同。看起來蘋果的A14不僅能夠實現工藝節點的改進,而且能夠取得更好的數據,這也是考慮到它也是一種新的微體系結構設計。

還有一點需要注意的是A14小型效率核心的數據。在這一代中,我們看到了這些新內核的巨大微體系結構提升,與去年的A13效率內核相比,這些新內核現在的性能提高了35%,同時還進一步降低了能耗。我不知道小核將如何在Apple的“ Apple Silicon” Mac設計中發揮作用,但是與其他當前的現代Arm設計相比,它們肯定仍然非常高效且非常高效。

最後,是x86與蘋果的性能比較。通常對於iPhone的評論,我會在這篇文章的這一部分對此進行評論,但是考慮到今天的背景和蘋果為蘋果硅所制定的目標,讓我們用一個完整的專門章節來研究這個問題…

從移動設備到Mac:會發生什麼?

迄今為止,我們對Apple芯片組的性能比較一直是在iPhone評論的背景下進行的,與x86設計並列的內容在本文中只是一個很小的腳註。今天的Apple Silicon發佈會完全改變了我們對性能的描述,拋開了人們通常爭論的典型蘋果與橘子的比較。

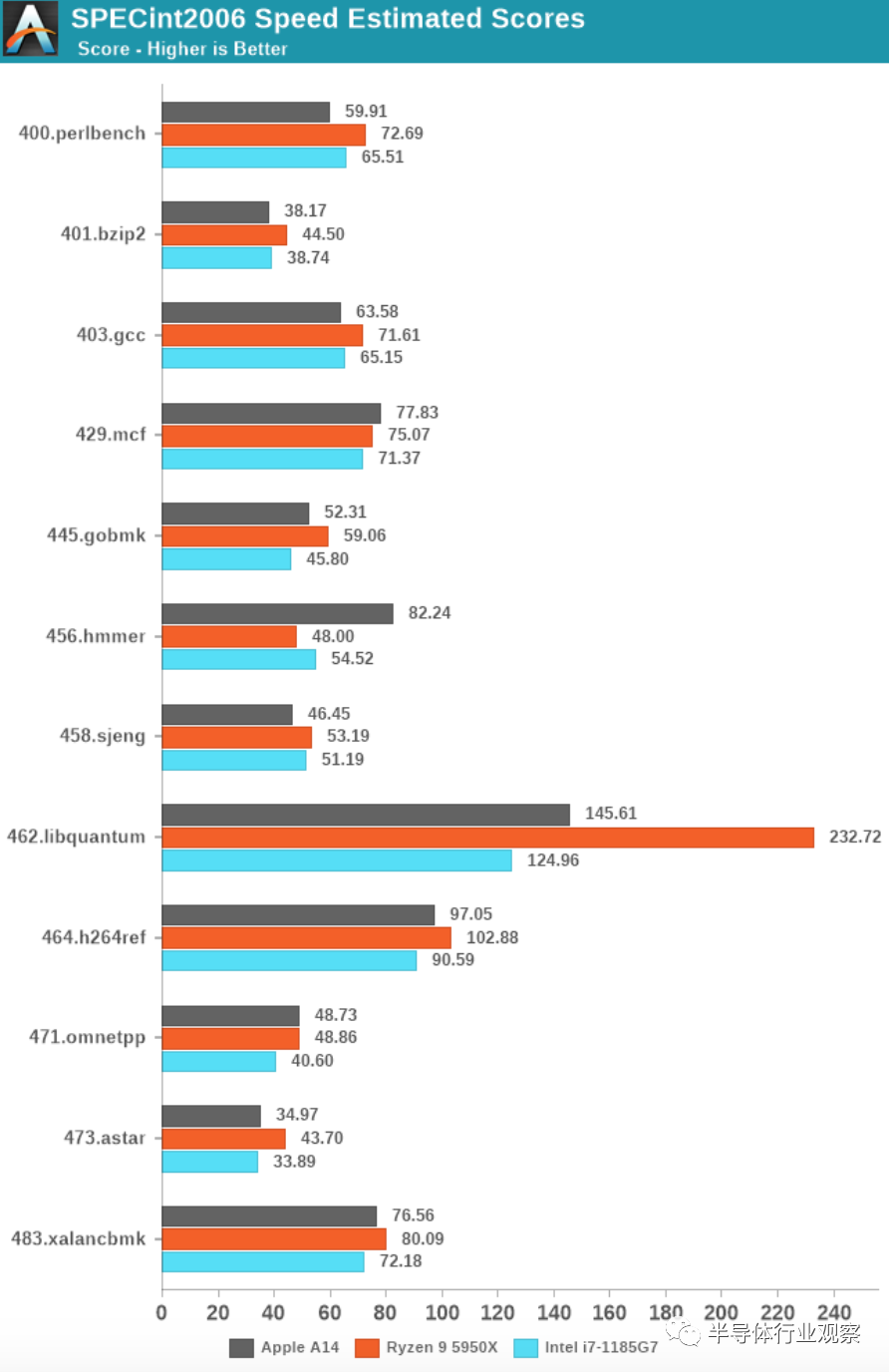

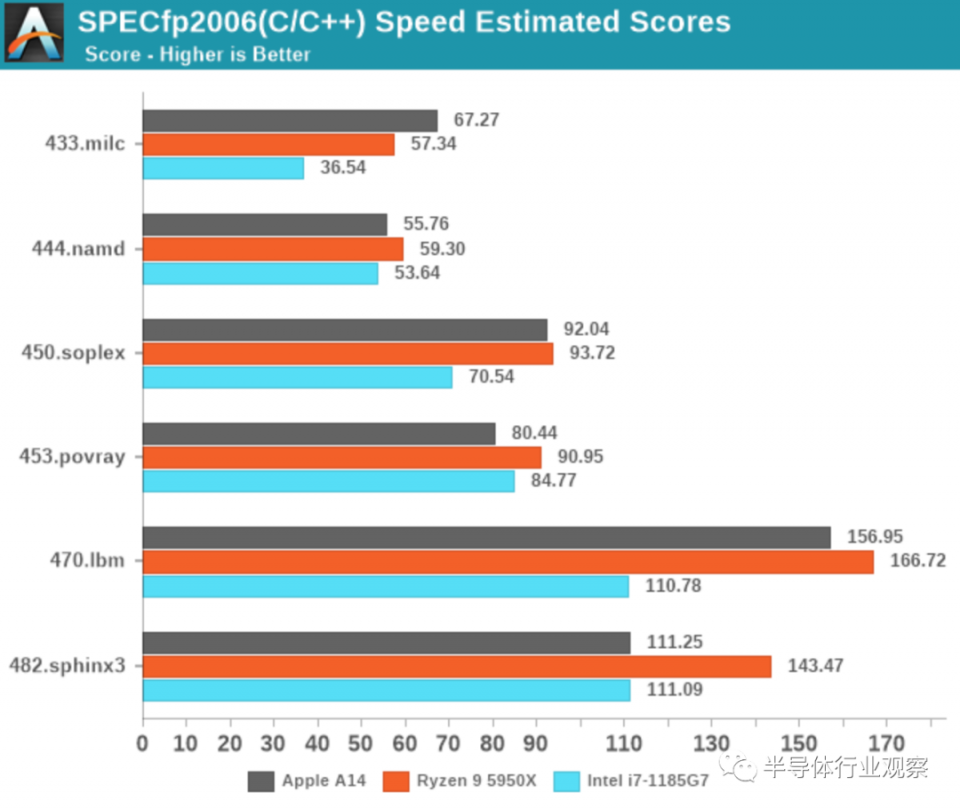

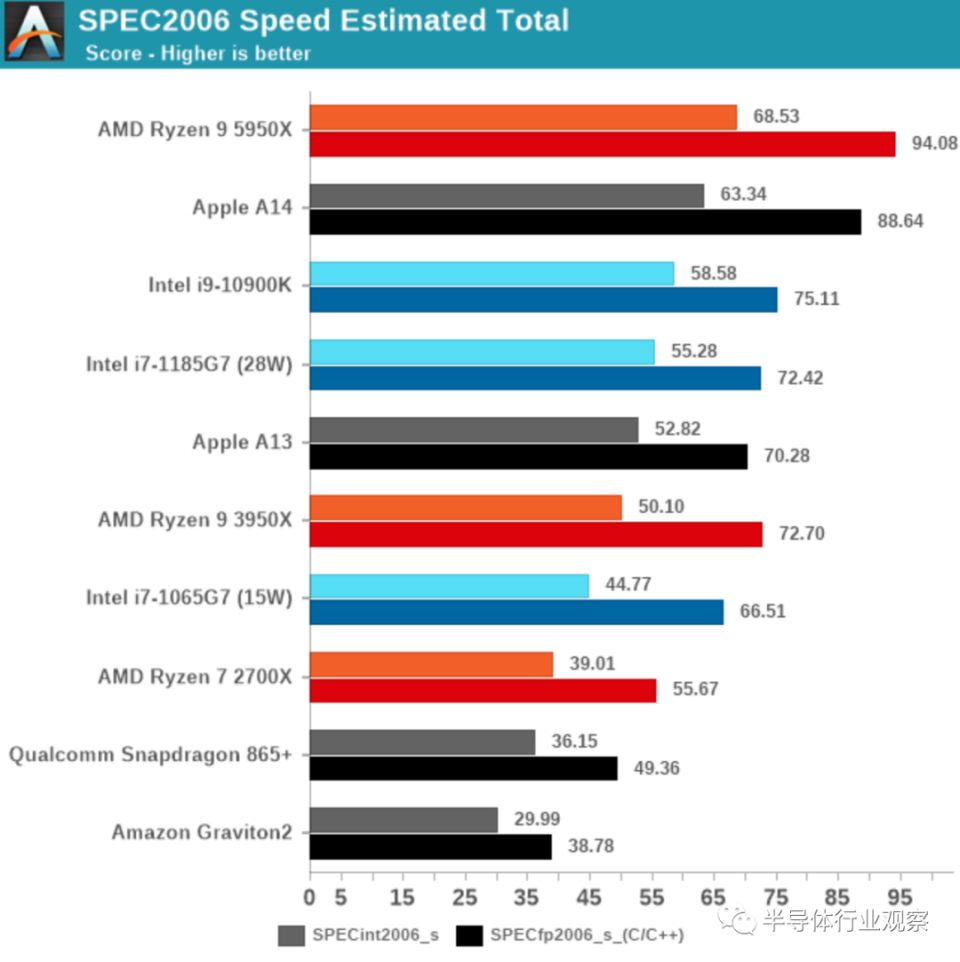

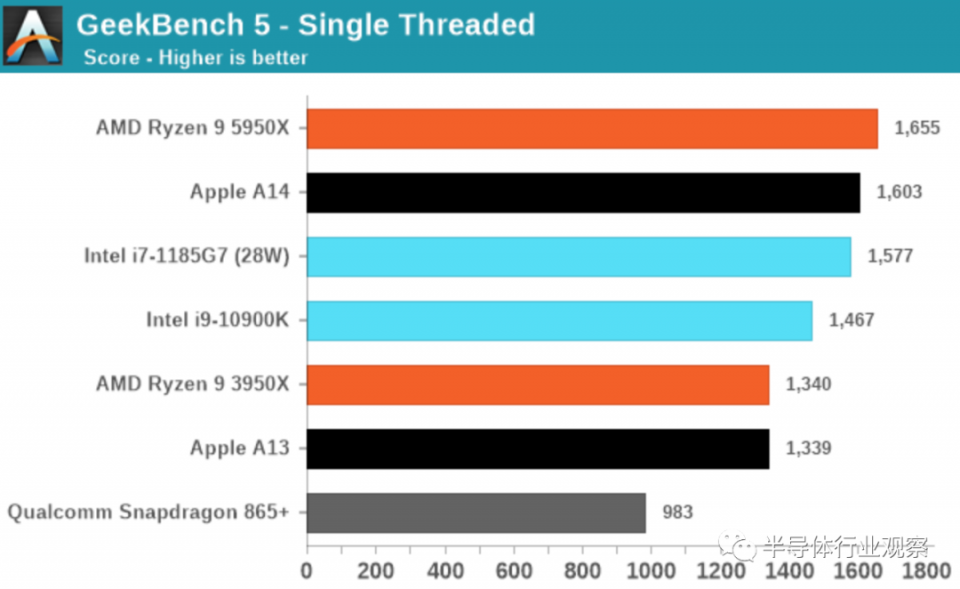

我們目前沒有Apple Silicon設備,很可能再過幾周都不會使用它們,但我們確實有A14,並且預計新的Mac芯片將基於我們在iPhone設計中看到的微架構。當然,我們仍然在比較手機芯片與高端筆記本電腦,甚至是高端台式機芯片,但考慮到性能數字,這也正是我們在這裏要説的重點,這是蘋果新推出的Apple Silicon Mac芯片所能達到的最低限度。

查看詳細分數,再次令我感到驚訝的是,A14不僅保持了這種速度,而且在內存延遲敏感型工作負載(例如429.mcf和471.omnetpp)上實際上擊敗了這兩個競爭對手,即使它們具有相同的性能內存(帶LPDDR4X-4266的i7-1185G7)或台式機級內存(帶DDR-3200的5950X)。

同樣,請忽略A14的456.hmmer得分優勢,這主要是由於編譯器差異造成的,請減去33%,以獲得更合適的比較數字。

事實上,蘋果能夠在一個包括SoC、DRAM和監管機構在內的設備總功耗為5W的情況下實現這一點,而在沒有DRAM或監管的情況下,設備功耗為+21W (1185G7)和49W (5950X)。這絕對是令人震驚的。

蘋果公司在兩種工作負載中均表現出色,這證明它們具有極其平衡的微體系結構,並且Apple Silicon將能夠在性能方面擴展至“桌面工作負載”而不會出現太大問題。

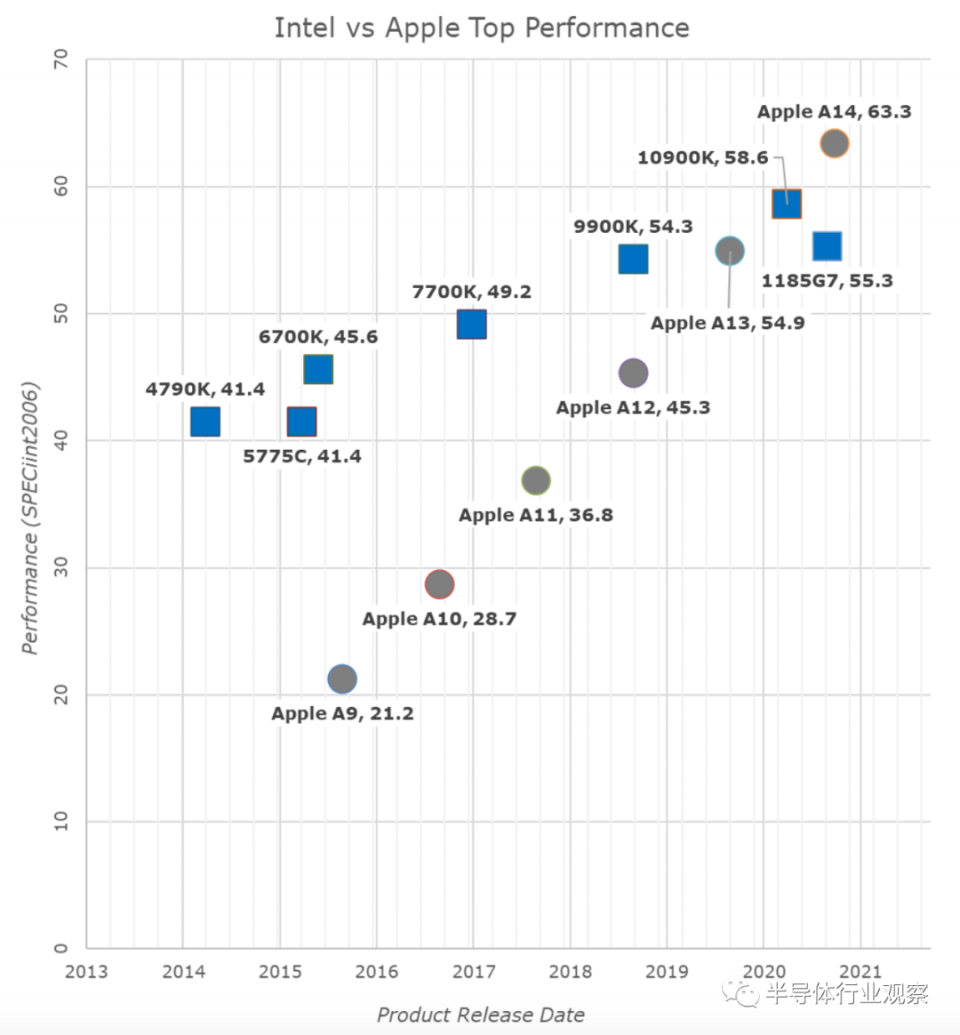

性能軌跡最終在哪裏相交

在A7發佈期間,人們對蘋果稱其微體系結構為桌面類設計的事實相當不屑一顧。人們對我們幾年前把A11和A12稱為接近桌面水平的性能數據也非常不屑一顧,今天標誌着這個行業的一個重要時刻,因為蘋果A14現在顯然能夠展示出英特爾所能提供的最佳性能。這是一個多年來一直在穩步執行和進步的績效軌跡:

這些年來,Apple的性能軌跡和毫無疑問的執行力已使Apple Silicon成為當今的現實。任何看到這張圖表的荒謬之處的人都會意識到,蘋果除了放棄英特爾和x86、轉而採用自己的內部微架構之外,沒有其他選擇——按部不動將意味着停滯不前和更糟糕的消費產品。

今天的公告只涉及蘋果筆記本電腦級的蘋果硅芯片,雖然我們在撰寫本文時還不知道蘋果將推出什麼產品的細節,但蘋果巨大的能效優勢意味着新芯片將能夠提供大幅延長的電池壽命和/或大幅提升的性能當前的英特爾MacBook產品線。

蘋果公司聲稱,他們將在兩年內將整個消費產品線完全轉換為蘋果硅芯片,這也預示着我們將看到未來的Mac Pro將採用高TDP 多核設計。如果該公司能夠繼續目前的表現軌跡,它將看起來非常令人印象深刻。

蘋果瞄準明星:在任的x86要小心了

前幾頁是在蘋果正式宣佈新的M1芯片之前寫的。我們已經看到了A14的出色表現,並超過了英特爾所能提供的最好的性能。新的M1的表現應該明顯高於這一水平。

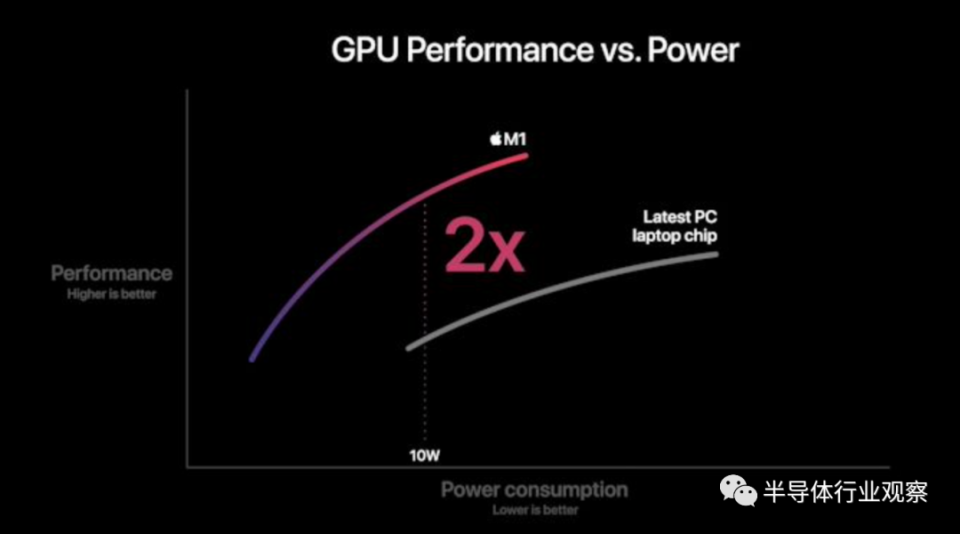

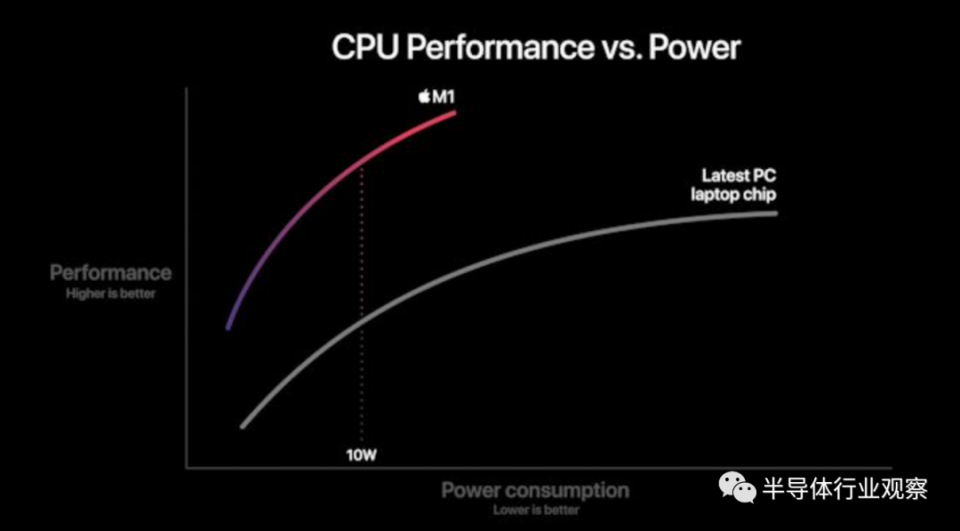

在演示過程中,我們將回顧蘋果的幾張幻燈片,以期對性能和效率有何期待。特別是性能/功率曲線,這是蘋果目前分享的最詳細的信息:

蘋果公司使用了更為先進的微體系結構,該體系結構提供了顯着的IPC,可在低內核時鐘下實現高性能,與現有的x86處理器相比,可顯着提高電源效率。該圖顯示,與現有競爭產品相比,M1在峯峯值處的性能提升約40%,而功耗僅為40%。

蘋果公司對隨機性能點的比較是值得批評的,但是蘋果聲稱其性能是2.5倍的10W測量點確實是有道理的,因為這是基於Intel的MacBook Air使用的芯片的標稱TDP。同樣,這要歸功於Apple在移動領域已經實現的能效特性,因此M1有望展現出如此大的收益-它肯定與我們的A14數據相匹配。

不要忘了GPU

今天,我們主要討論了CPU方面的問題,因為這是發生前所未有的行業轉變的地方。但是,我們不應忘記GPU,因為新的M1代表了Apple首次將其自定義設計引入Mac領域。