是時候該重視DTCO了_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2020-12-21 18:50

隨着先進半導體節點尺寸的進一步下降以及工藝越來越複雜,如何最大化先進半導體節點給芯片帶來的收益越來越得到重視,相應的電路設計與工藝協同優化(design technology co-optimization,DTCO)也成為了熱門概念。本文將分析DTCO的歷史,現狀以及未來的發展走向。

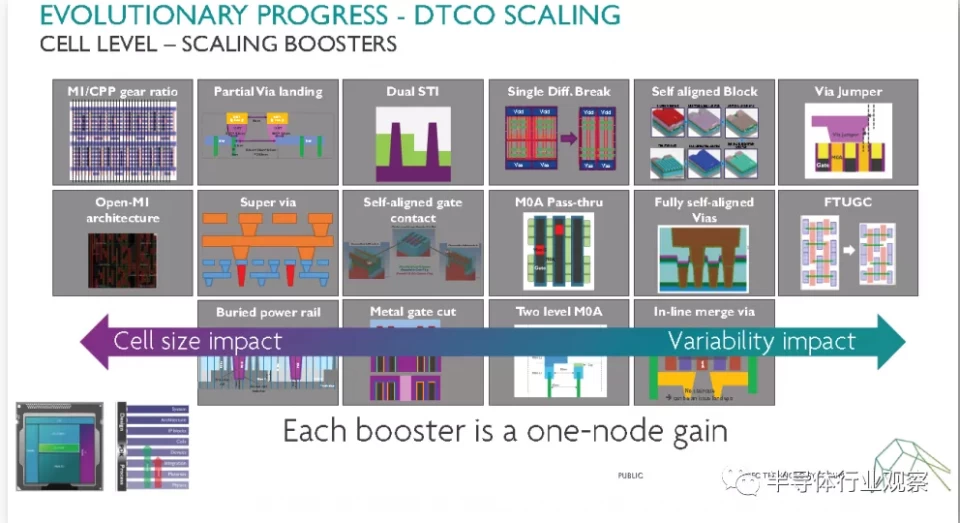

DTCO的定義DTCO的定義相當寬泛,任何將半導體工藝和具體電路設計做協同優化的措施都可以成為DTCO。通常來説,常規的半導體芯片設計是在工藝和PDK給定的情況下去優化電路設計,因此,在近幾年的語境下,DTCO主要是指如何根據半導體芯片的具體要求去做半導體工藝的相應優化。具體的工藝優化可以包括金屬連線的材料,通孔設計,具體的CMOS器件設計(如Fin的優化)等等。

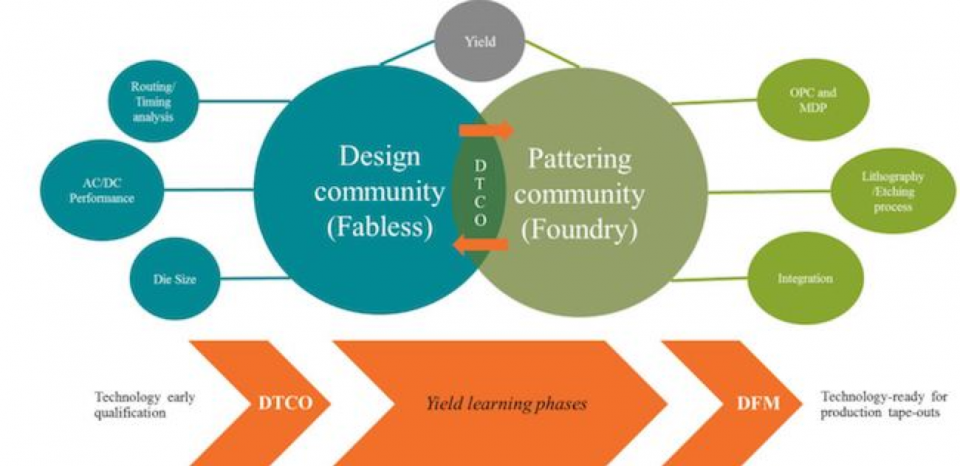

DTCO的慣常做法是Fab在開發新一代工藝時,會使用一些常規的電路設計來評估各種新一代工藝中的選項,從而決定最佳方案。另一方面,Fab也會與合作的Fabless提供早期評估版本的PDK,Fabless使用PDK來設計一些關鍵電路並評估其性能,並且為Fab來提供反饋以幫助Fab去迭代工藝設計。

DTCO的沿革根據具體芯片設計的需求去調整工藝的做法其實由來已久。在IDM時期,這樣的做法可謂是標準操作,尤其是在針對模擬電路的半導體生產線中,根據電路的需求去調整半導體器件和工藝的設計甚至可以説是不少老牌模擬芯片公司的核心競爭力。

然而,隨着摩爾定律和Fabless模式的興起,根據具體電路去調整工藝相對IDM時代有所減少。這有多方面的原因。

首先,摩爾定律指出了一條非常直接而且可操作性極強的半導體工藝發展路線圖。因此,在摩爾定律的黃金時代,DTCO流程能調整的參數並不多。此外,從Fabless的角度來看,因為每過一年多都會有新一代的半導體工藝出現導致性能大幅提升,花大量時間和資源去幫助本代工藝做DTCO優化的收益並不大。最後,晶圓代工模式的一個重要假設就是平台化標準化的工藝設計,因此Fab更傾向於去提供一兩套標準的工藝(例如低功耗,高性能等等),而並沒有很強的根據客户設計公司的反饋去定製化工藝的意願。總體來説,在摩爾定律的黃金時代,DTCO更多的起的是評估和驗證作用,用來指導工藝設計尤其是Fabless走DTCO流程去指導Fab的工藝設計的成分相對來説較少。

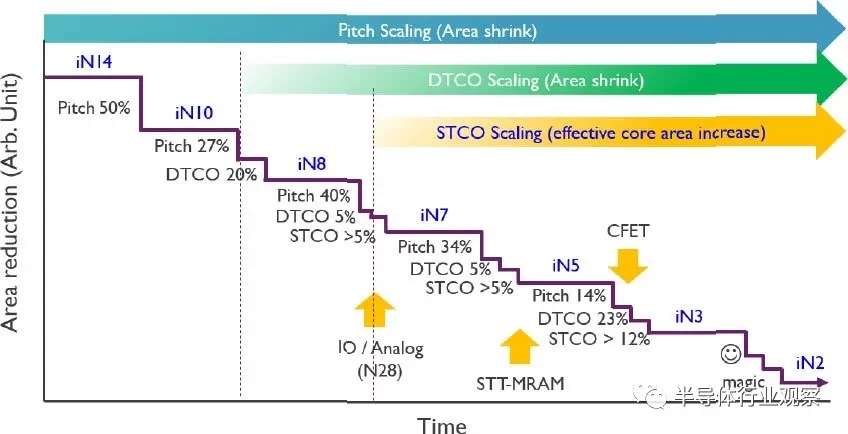

然而,隨着摩爾定律的延續越來越有挑戰性,開發和使用新一代半導體工藝的成本都越來越高,同時新一代半導體工藝帶來的性能提升卻越來越小,今天我們看到藉助DTCO來儘可能多地優化半導體工藝以及電路設計正在變得越來越熱門。在未來,我們甚至會看到系統級別的DTCO(即system-technology co-optimization,STCO),即在常規電路-工藝優化之外額外考慮2.5D/3DIC封裝的協同優化。根據頂級半導體研究機構IMEC的分析,DTCO和STCO從10nm開始對於半導體工藝節點進一步演進起的作用來時逐步提升,並逐漸取代之前摩爾定律中的簡單減小工藝特徵尺寸的模式。

從Fab的角度來説,開發新一代的半導體工藝越來越複雜,新一代工藝中可選的選項和參數也越來越多,每一個可選的選項和參數都有自己的優缺點,那麼如何決定下一代工藝的具體使用選項和參數,這還是要依靠DTCO。原因很簡單,因為最終半導體工藝是要提供給客户使用的,那麼具體的工藝選項怎麼調整,它的金標準就應該是客户使用下一代工藝的設計是否能滿足需求,因此使用客户的具體設計來評估並調整Fab工藝的DTCO正在變得越來越重要。

從Fabless的角度來看,先進半導體工藝節點的成本越來越高,因此如果計劃在新一代半導體工藝節點大批量出貨的話當然會希望該工藝節點能滿足自己的需求,甚至能為自己的產品量身定做。在今天我們看到了越來越多的大型Fabless和Fab協同做DTCO的案例,而DTCO也成為了越來越熱門的關鍵詞。例如,高通在今年VLSI Symposium上發表了自己使用EUV 7nm工藝的驍龍765 SoC中DTCO的案例分析,其中高通通過和Fab合作使用DTCO成功地將處理器的最低電源電壓降低了80 mV,從而大大改善了芯片良率以及處理器的能效比。另外,在上個月剛剛結束的IEDM 2020中, DTCO成為了一個核心議程(Focus Session),Intel,IMEC,TSMC等頂級的Fab和半導體研究機構都發表了自己的DTCO研究,其中TSMC的研究正是將DTCO的流程使用在3DIC領域並提升了15%的性能,可見這個領域的發展方興未艾,未來將會變得越來越重要。

DTCO未來的趨勢我們認為,未來的DTCO將會變得越來越重要。具體來説,DTCO有以下這些趨勢值得我們關注。

首先,就是通過DTCO,大型Fabless對於半導體工藝開發將會有越來越多參與度。如前所述,Fab開發下一代半導體工藝的成本越來越高,Fabless使用新一代半導體工藝的成本也越來越高,因此通過DTCO達成Fab和Fabless在新一代半導體工藝上的緊密合作將是降低新一代半導體工藝開發和使用風險的重要舉措。從這個意義上,大型Fabless將在下一代半導體工藝的開發中有更多的話語權,未來將會出現越來越多的為大型Fab的核心產品量身定做的專用半導體工藝。從某種意義上説,這樣Fab和Fabless的緊密合作使得半導體代工模式正在慢慢地靠攏IDM。

其次,DTCO的範圍將不僅僅是半導體工藝,未來將越來越多地考慮半導體先進封裝工藝,例如3DIC等。普遍認為3DIC等先進封裝技術將會逐漸接過摩爾定律成為下一代半導體工藝演進的核心推力,而由於3DIC的設計中也存在大量的工藝參數並且客户的設計更靈活,因此使用DTCO流程來幫助先進封裝技術的設計將會成為主流。

最後,DTCO流程相關的工具鏈和人才儲備也值得我們關注。從工具鏈角度,如果能有一套環境能打通工藝器件模擬和相關電路設計仿真將會大大簡化DTCO的流程,而在這個角度Synopsys的相關工具可以説是最齊全的。從人才角度來説,之前的半導體工藝和半導體電路設計往往是兩個涇渭分明的學科,而在未來隨着DTCO變得越來越主流,我們可望會看到更多對工藝和電路複合型人才的需求。