淺談台積電的先進封裝_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2021-08-30 18:07

來源:內容由半導體行業觀察(ID:icbank)原創,作者:熱心網友投稿,謝謝。

編者按:

在之前,半導體行業觀察發佈了台積電在hotchips 33上的一個演講,並以《台積電更新封裝路線圖》為題,呈現給了讀者。現在我們將一位讀者的初步解讀,分享出來,希望能夠給大家提供一些思考。後續我們將發佈更多的解讀,希望有意分享的讀者與我們聯繫,謝謝!

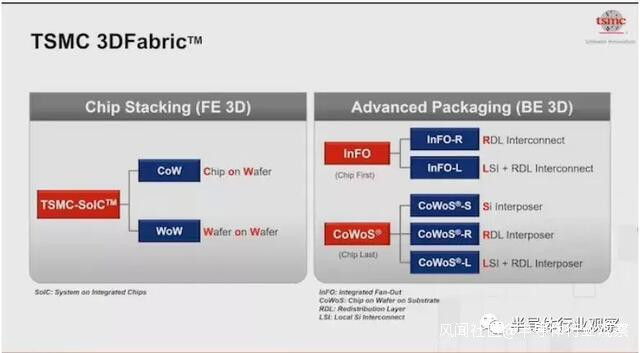

Die-to-die ,ODI ,TSV所有這些單詞和首字母縮略詞都有着相同點——它們都與兩塊硅的物理連接有關。一般來説有多種方法將多個芯片連接在一起,而台積電有許多這樣的技術。為了統一技術,它將其命名為2.5D和3D封裝等。最近台積電推出了有一種新的封裝解決方案DFabric。3DFabric將台積電提供的十幾種包裝技術結合起來,總的來説,3DFabric分為兩個部分:一邊是所説的“前道”芯片堆疊技術,如Cow(Chip on wafer);另一邊是“後道”封裝技術,如InFO (Integrated Fan-Out)和CoWoS (chip-on-wafer -on- substrate)。

台積電引入了許多的專業的術語,如RDL或LSI等,這些術語有別於英特爾的術語,下文中我們會做詳細的解釋:

台積電引入了許多的專業的術語,如RDL或LSI等,這些術語有別於英特爾的術語,下文中我們會做詳細的解釋:

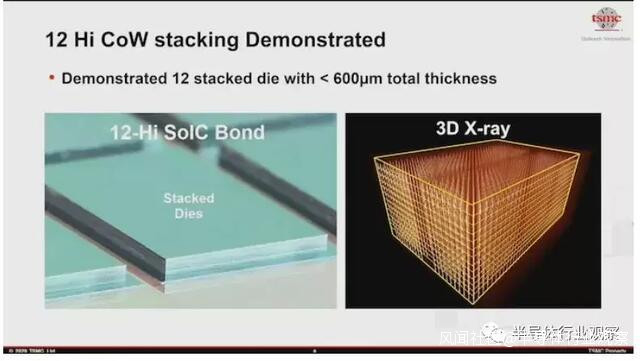

前道芯片堆疊技術,被統稱為“SoIC”,或集成芯片系統。這些技術的主要的特徵峯是不會使用後端集成用到的凸點技術,而是直接將硅片堆疊到一起。就好似是一整個硅片一樣。

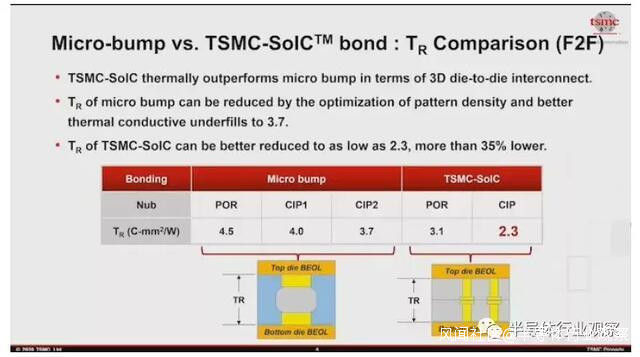

這種技術相對來説更加的複雜,但是在熱阻方面有着很大的有優勢。

如下圖所示 SoIC連接的熱電阻比微凸連接低35%,隨着封裝技術的發展芯片的 集成度越高,這種連接出的熱阻是一個非常大的挑戰。然而這些SoIC技術的缺點是堆疊設計必須與其他芯片共同設計並且在最開始芯片設計方案就需要確定下來,然而微凸點技術只是需要後期把芯片連接在一起。

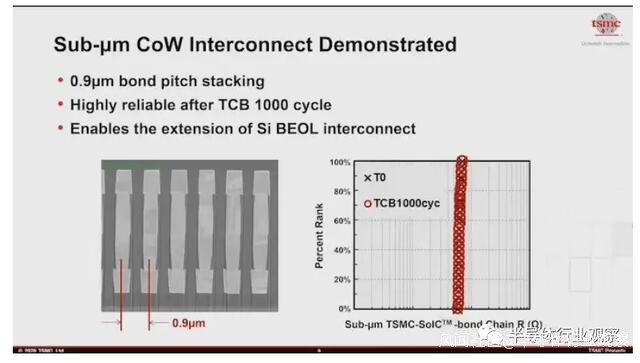

雖然有上述的缺點但是台積電仍然努力的推銷它的SoIC技術。在一般情況下人們自然會擔心這種連接的可靠性,和連接密度。但是台積電表示,它們可以實現0.9微米的鍵合間距。相比於因特爾它們的間距提高了兩個數量級。

雖然有上述的缺點但是台積電仍然努力的推銷它的SoIC技術。在一般情況下人們自然會擔心這種連接的可靠性,和連接密度。但是台積電表示,它們可以實現0.9微米的鍵合間距。相比於因特爾它們的間距提高了兩個數量級。

台積電計劃在其7納米,五納米和三納米工藝節點上為客户提供SoIC技術,屆時TSV 的間距將從9微米縮減到4.5微米。

台積電計劃在其7納米,五納米和三納米工藝節點上為客户提供SoIC技術,屆時TSV 的間距將從9微米縮減到4.5微米。

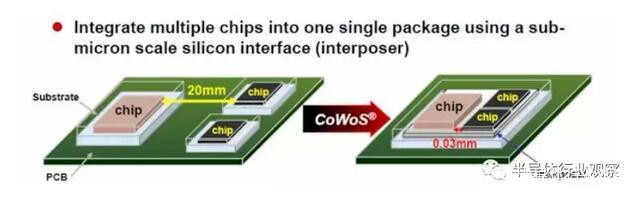

台積電後道先進封裝有三種形式,大多數人都熟悉的一種方法是轉接板方法,在所有互連的芯片下面放置一大塊硅,這是一種比簡單地通過PCB封裝更好的佈線方法。

台積電後道先進封裝有三種形式,大多數人都熟悉的一種方法是轉接板方法,在所有互連的芯片下面放置一大塊硅,這是一種比簡單地通過PCB封裝更好的佈線方法。

另一種方法是,與之類似,轉接板是嵌入在PCB中,只用於連接一個特定的芯片到另一個(英特爾叫這種方法為的嵌入式多芯片互連橋,或EMIB)。

另一種方法是,與之類似,轉接板是嵌入在PCB中,只用於連接一個特定的芯片到另一個(英特爾叫這種方法為的嵌入式多芯片互連橋,或EMIB)。

第三種是直接垂直堆疊,然而這與上面提到的SoIC實現方式不同,因為在兩片硅之間使用微凸點,而SoIC並不使用。事實上,台積電有一半的產品中所有的實現都是基於微凸點的——不同芯片之間可以更好地混合和匹配場景,但它沒有獲得SoIC提供的密度或功率優勢。這就是為什麼它被稱為“後道”高級封裝——例如,支持hbm的GPU。

許多支持HBM的GPU有一個GPU芯片,幾個HBM芯片,都放置在一個轉接板上。GPU和HBM是由不同的公司製造的(甚至可以使用不同的HBM),而轉接板也可以在其他地方製造。這個轉接板可以是無源的(不包含邏輯,只有模對模路由),也可以是有源的,如果需要的話,可以為許多的芯片實現連接,儘管這意味着消耗電力。台積電的將這種封裝的形式叫做CoWoS,根據技術的不同的類型,CoWoS有三個方案。

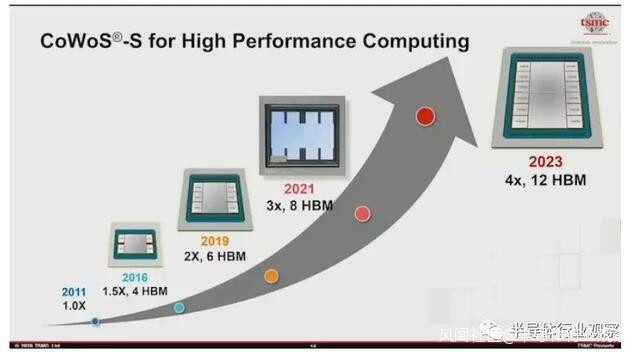

大家都熟悉的是CoWoS, S代表Silicon Interposer。通常是在65 nm 的製程中製造,因為是一整塊的單晶片,所以必須以同樣的方式製造,隨着我們進入小芯片的時代,需要有更多的芯片集成所以轉接板的尺寸越來越大,但是受到掩模版尺寸的限制,所以台積電研發出了大於掩模版尺寸的技術,根據他的路線圖道2023年,這些轉接板的尺寸將四倍於掩模版。

大家都熟悉的是CoWoS, S代表Silicon Interposer。通常是在65 nm 的製程中製造,因為是一整塊的單晶片,所以必須以同樣的方式製造,隨着我們進入小芯片的時代,需要有更多的芯片集成所以轉接板的尺寸越來越大,但是受到掩模版尺寸的限制,所以台積電研發出了大於掩模版尺寸的技術,根據他的路線圖道2023年,這些轉接板的尺寸將四倍於掩模版。

台積電也正在實現一個名為CoWoS – S STAR的技術方案,用於標準架構。這將允許客户在2/4/6 HBM堆棧的特定設計協議下工作,最小化轉接板的尺寸,同時也加快了上市時間並提高產量。

台積電也正在實現一個名為CoWoS – S STAR的技術方案,用於標準架構。這將允許客户在2/4/6 HBM堆棧的特定設計協議下工作,最小化轉接板的尺寸,同時也加快了上市時間並提高產量。

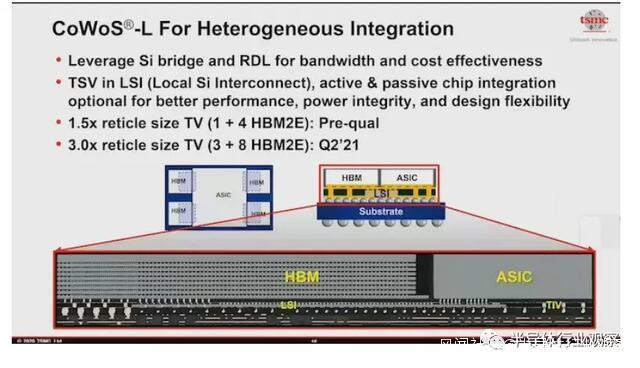

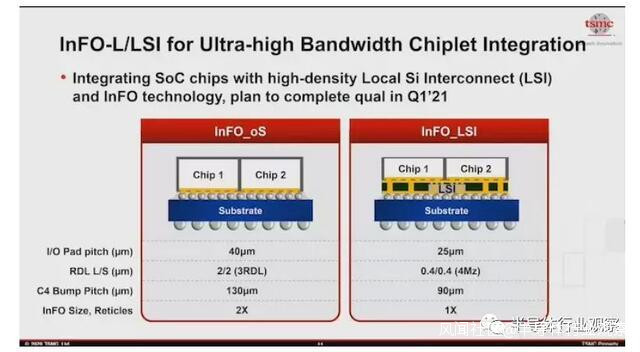

CoWoS - l是另一種方案,使用本地硅互連和再分佈線層。這裏的關鍵詞是“本地”,意思是它在將兩個硅晶片連接在一起。這將是台積電應對英特爾EMIB的方式。雖然英特爾的EMIB已經用於多個產品(Kaby-G, Stratix 10, Agilex FPGA),但台積電目前僅處於驗證階段。

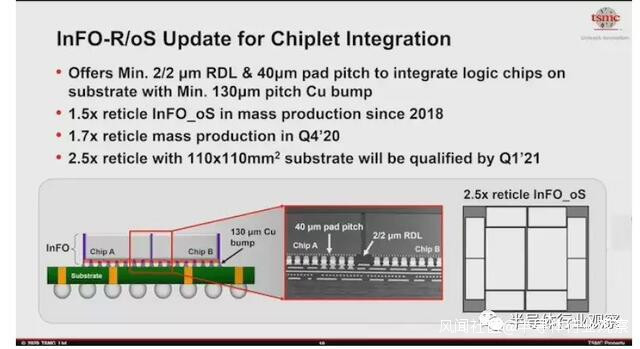

InFO(集成扇出)封裝允許芯片在SoC的標準平面之外“扇出”額外的連接增加I/O接口。台積電多年來一直提供InFO,但在3DFabric下,它現在將提供與包內連接相關的不同類型的InFO。InFO-R(也稱為InFO_oS)允許在芯片和微凸點之間添加再分配層,以便將多個芯片給封裝到一起。這種技術的限制因素也是掩模版的尺寸。

InFO(集成扇出)封裝允許芯片在SoC的標準平面之外“扇出”額外的連接增加I/O接口。台積電多年來一直提供InFO,但在3DFabric下,它現在將提供與包內連接相關的不同類型的InFO。InFO-R(也稱為InFO_oS)允許在芯片和微凸點之間添加再分配層,以便將多個芯片給封裝到一起。這種技術的限制因素也是掩模版的尺寸。

InFO- l與CoWoS - l類似,它使用一個局部的硅互連將多個InFO芯片連接在一起。這項技術仍在進行中。

InFO- l與CoWoS - l類似,它使用一個局部的硅互連將多個InFO芯片連接在一起。這項技術仍在進行中。

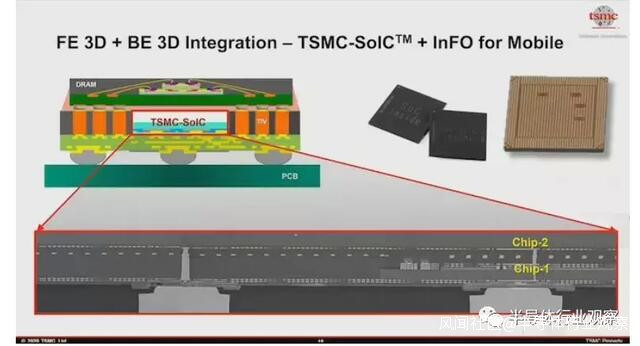

TMSC的封裝技術也可以組合在同一產品中。通過實現前端(SoIC)和後端(InFO)封裝,可以製造新的產品類別。該公司製作了一個這樣的模型:

TMSC的封裝技術也可以組合在同一產品中。通過實現前端(SoIC)和後端(InFO)封裝,可以製造新的產品類別。該公司製作了一個這樣的模型:

台積電,只是説“3 D fabric”可能意味着很多東西,但是CoWoS-S CoWoS-L之間的區別也很難用幾句話來解釋清楚的。

台積電,只是説“3 D fabric”可能意味着很多東西,但是CoWoS-S CoWoS-L之間的區別也很難用幾句話來解釋清楚的。