下一代EUV光刻機,新型晶體管,摩爾定律的“救星”大盤點!_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2021-09-06 16:25

來源:內容由半導體行業觀察(ID:icbank)編譯,作者:湯之上隆,謝謝。編者按

筆者(本文作者湯之上隆)在日本以DRAM席捲世界的時候,就成為半導體技術人員(到2002年為止的16年時間裏一直是技術人員)。從那以後,我覺得半導體沒有像今天這樣被世界所關注。這就會牽扯起一個老生常談的問題——摩爾定律何時會迎來終結?”和“半導體的微縮何時停止?

在1980年代後半期到1990年代中期的時候,由於幹法蝕刻等使用等離子的過程造成的charging damage嚴重,半導體的進一步微縮被認為是不可能的。然而,日本的技術人員們進行了先驅性的研究。之後,日美進行了徹底地研究的結果是,到現在為止仍然持續使用等離子的幹法蝕刻。因此,在這方面看,半導體微縮是不會停止的。

之後,我記得再次開始談及“半導體的微縮已經到了極限了嗎?”是在ArF曝光設備在2006年達到了分辨率極限的時候(圖1)。當時筆者是同志社大學經營學的老師,接受了某個半導體相關企業委託研究,對當時與最先進的精細化相關的關鍵人物們説:“你覺得半導體的精細化極限是幾nm?”進行了這樣的聽取調查。

現在重新審視這個調查結果,相當有趣。因此,本文就“半導體的微縮何時停止?”以及“摩爾法則何時會迎來終結?”為主題。

2007年進行的微縮調查

2006年左右,邏輯器件半導體的微縮正在從65nm向45nm發展。但是,當時最先進的曝光設備ArF(現在稱為ArF幹法)已經達到了分辨率極限,而作為下一代曝光設備的候補的EUV(極端紫外線)問題堆積如山,甚至連R&D設備都不存在。因此,“半導體的微縮不是已經結束了嗎?”這樣的氣氛在半導體業界飄浮着。

當時還是同志社大學經營學老師的筆者説:“半導體的微縮什麼時候停止?”受此委託研究的影響,2007年7~9月(整整2個月)環遊世界,訪問了尖端半導體製造商、製造設備和材料製造商、美國的財團SEMATECH和歐洲imec,對與微縮相關的關鍵人物進行了調查。

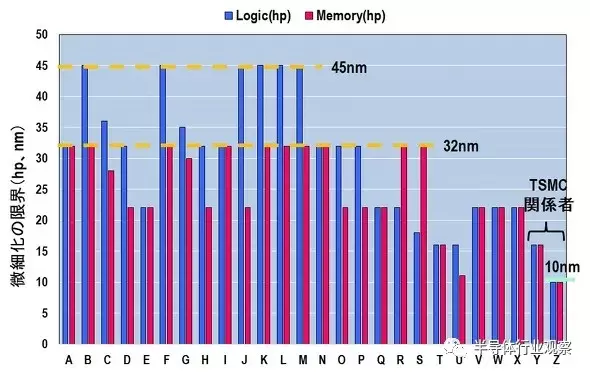

當時詢問的時候,我們把邏輯器件和內存分開來看。問題包括例如你覺得半間距(hp)以幾nm的界限會是什麼”。回顧當時,最細微的金屬佈線(M1)的間距與技術節點大致成比例關係,所以上述問題是“M1的hp界限是多少nm?”(圖2)。

出自:平本俊郎(東京大學生產技術研究所)

另外,關於存儲器,NAND型閃存持續進行二維微縮,其水平比DRAM先進,所以詢問的是“您認為NAND閃存的微配線M1(或柵極長度)的hp是幾nm?”這樣的問題。圖3展示出了這樣進行的調查結果。A、B…、Z表示了回答筆者提問的技術人員的序列號(時間上按A→B→…、Z的順序進行了調查)。

微縮的極限被輕易打破

從結果來看,當時有不少技術人員認為邏輯器件上hp為45nm的時候是極限,而內存則在hp為32nm的時候是極限。這種微縮的界限是通過延長ArF幹法的ArF浸液和SADP(Self-Arigined Double Patterning、)等技術簡單地被打破的。即使當時有相當多的技術人員認為“像浸液一樣複雜的曝光設備無法啓動”、“即使SADP微縮了也不會提高成品率”。

值得一提的是,在訪問TSMC以調查的時候,筆者聯繫了TSMC的朋友,讓他們聚集了5~6個主管級別的人。筆者在台灣新竹的TSMC會議室,將之前的聽取調查結果(A至X)投射到幻燈片上。

當時聚集在一起的TSMC相關人員全體大笑起來。而且,“你在説什麼呢,hp45nm和hp32nm是極限之類的蠢話?我們已經開發了22nm了?”。其中的2人也回答了我提的問題,他們給出的答案分別是hp16nm和hp10nm。

我認為TSMC從2018年開始量產的7nm的M1在hp18nm左右,2020年量產的最先進5nm的M1在hp16nm附近。因此,台積電當時的極限説法在2020年被打破。至於剩下的hp10nm,我認為在TSMC的3nm,未來的2nm上接近其界限,如果再實現下一個1.5nm~1nm的話,這個極限就會被打破。

關於EUV的調查

從“微縮極限的hp是多少nm”的調查中可以看出,2007年的時候正在開發極為困難的EUV,筆者對A~Z的相關人員説:“EUV的量產機是不是不能實現呢?”針對這樣的問題,他們給出結果如圖4所示。

這裏,將圖4分成兩部分,分別是半導體廠商的光刻技術人員、光刻相關的製造設備或材料製造商的技術人員以及光刻以外的技術人員。又或者分成半導體廠商的集成技術人員和光刻以外的製造設備或材料相關人員。

於是,在18名光刻相關人員中,超過半數的10人回答“是(即不能進行EUV量產機)”(圖4-1)。另一方面,除了光刻以外的10名相關人員中有7人回答“NO(也就是EUV量產機可以)”(圖4-2)。這個對比實在有趣。

光刻相關人員大概是因為對EUV開發的困難非常瞭解,才會覺得“無法實現量產機”。然而,除了光刻以外的相關人員卻從一開始就不相信光刻專家,認為“光刻專家總是説做不到而鬧得不可開交”。

並且從結果來看,2019年TSMC在7nm+的時候大量應用EUV光刻機,2020年佈線也適用EUV的5nm上升了。因此,證明了光刻專家説的話不正確。也就是説,不要相信光刻專家“做不到”比較好。

這樣,在半導體業界歷史上,微縮的極限説總是被打破,雖然步伐雖然慢下來,但是沒有停止。那麼,今後的前景如何呢?

關於微縮,從2001年國際半導體技術發展路線圖(International Technology Roadmap for Semiconductors、ITRS)可以看到。如果按照這個路線圖繼續前進,走在最尖端的是量產PC用處理器的美國Intel,所以這個路線圖又被稱為“Intel Technology Roadmap for Semiconductor”(Intel的路線圖)。

然而,在Intel 的10nm於2016年失敗時以後,ITRS也在當年結束,之後被International Roadmap for Devices and Systems(IRDS)繼承,但是已經沒有人再説這是“Intel的路線圖”了。並且,代替Intel躍居到微縮最前端的是TSMC,半導體的路線圖比起IRDS,感覺歐洲財團imec發表的東西更接近現實。

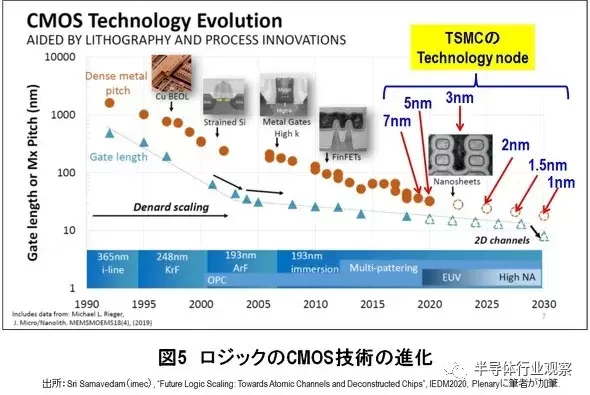

邏輯器件CMOS的進化與微縮

圖5顯示了1990年到2030年CMOS進化和精細化的實際成果和預測。通過這張圖,可以一覽精細化的過去、現在、未來。對筆者來説是一幅令人感動的圖。

直到2000年代中期,IBM的Robert H.Dennard提倡的定標規則的微縮才進展順利。也就是説,2年內實現了70%的微縮,提高了晶體管的工作速度、降低耗電和集成度。但是,從2003年左右開始,柵極長度的微縮速度降低了。從這時候開始,即使微縮晶體管的動作速度也無法提高。因此,作為輔助技術,產業界開始導入Cu/Low-k配線、應變硅(Strain Si)、High-k/Metal門、FinFETs等。

另外,圖5中寫着“Dense Metal Pichi”的最細微的配線(M1)的定標有時一邊減速一邊繼續。

並且,在2016年Intel 10nm的失敗之後,微縮的主角轉移到了TSMC。在該圖中,試着寫入了預計2018年以後TSMC量產以及今後量產的技術節點。

比較imec的路線圖和TSMC的量產時間表可以看到,雖然EUV的適用時期一致,但在CMOS中使用Gate All Arround(GAA)結構的Nanosheets的時期不同。imec設想為3nm,但目前投入該節點風險試產的TSMC依然使用的是FinFET工藝,他們計劃從2nm開始採用Nanosheets。

不管怎樣,到2030年,柵極長度和微佈線M1的微縮都不會停止。根據這個圖,今後10年內,甚至不會減速。相反,如果在1nm處採用了被稱為2D channels的新CMOS結構,則柵極長度的微縮將進步很多。

晶體管和微細布線的微縮

圖6展示出了伴隨邏輯器件微縮的晶體管結構的變遷。

如圖所示,從3nm到2nm,晶體管從FinFET變化為Nanosheets。另外,imec認為從2nm到1.5nm,分開nMOS和pMOS的Forksheets很有前途。與此相對,在TSMC的量產計劃中,在2nm處使用Nanosheets的樣子,卻沒有聽到採用Forksheets的説法。

另外,imec設想在1.5nm附近沿縱向形成nMOS和pMOS的Compulementary FET(CFET),但這在TSMC的研發路線圖中也沒看到任何蛛絲馬跡。但是,對於預計1nm以及之後登場的2D atomic channeels,TSMC也進行着同樣的研發。

像這樣,晶體管有各種各樣的選擇,感覺真的快要進化了。不過,微細布線的開發相當嚴重。在當前成為主流的Cu佈線中,當佈線寬度被精細化時,由於Cu的灰度引起的散射和由於擋板金屬的散射而引起的抵抗增加成為大問題(圖7)。

目前的Cu Dual Damascene只能使用到3nm,從2nm開始將Ru用於VIA的Hybrid,在1.5nm處將Ru等直接加工(Subtractive),然後有必要將層間絕緣膜製成Air Gap。此外, 1nm及其以上需要探索完全新的材料。

綜上所述,到2030年為止,晶體管結構有各種各樣的候補,但是伴隨着佈線的精細化,電阻增大的問題難以避免,如果要進行批量生產,必須要對此進行材料變更等相當大膽的研發。

EUV微縮的路線圖

如上所述,從現在到2030年之間,晶體管在改變結構的同時,微細布線在改變形成方法和材料的同時,繼續進行微縮。為此作為必要的EUV會發生怎樣的變化呢?

圖8展示出了EUV微縮路線圖。在當前最尖端的微縮中,使用鏡頭開口數NA=0.33的EUV(以下稱為ReglarNA)。此後,為了更精細化,在下四個階段的路線圖中實行EUV微縮(與圖8的編號稍有偏差)。

圖8.EUV光刻微縮的路線圖

1.28~32nm間距的微細加工是ReglarNA EUV單曝光的極限。

2.在22~24nm間距的情況下,在ReglarNA的EUV下進行SADP

3.在18nm間距以後,使用NA=0.55(稱為HighNA)的EUV

4.為了進一步的精細加工,使用High NA+SADP

如上展示了到2030年為止得EUV微縮路線圖。問題是,ReglarNA的EUV值為160~180億日元,而在2024年左右登場的High NA的EUV值則達到480億日元。到底,使用如此高額的曝光設備製造的邏輯半導體作為商務成立嗎?使用HighNA EUV時的晶圓成本又是一個要考慮的問題。

據説HighNA的EUV登場是在2024年左右。用TSMC的技術節點來説大約是2nm。該設想與imec也相同,在對2nm+這一世代應用High NA EUV光刻機的前提下,我們計算一下芯片的成本(圖9)。

圖9.使用HighNA EUV時的晶圓成本

在該計算中,假定(1)HighNA的EUV設備價格是ReglarNA的EUV的1.5倍,(2)吞吐量不變。因此,ReglarNA的EUV值為180億日元的話,HighNA的EUV值必須是270億日元(如果傳聞中480億日元的話,以下的計算是不成立的)。

在該假設進行下的話,在芯片製造過程中,有形成晶體管的Front End of Line(FEOL)、連接晶體管和配線的通道等Middle of Line(MOL)、形成多層佈線的Back End of Line(BEOL)等3個工序。

在2nm+的技術節點中,關於是否使用High NA的EUV,使用的話要使用多少,為此我們在3種情況下比較芯片成本。

1.將Regular NA的EUV應用於14層,將ArF浸沒式應用於2層時的芯片成本設為“1”。可能有很多ReglarNA的EUF+SADP的工序。

2.作為前期採用的方案,如果High NA的EUV是4層,Regular NA的EUV是6層,ArF浸沒式是2層,則可以減少5%的芯片成本。

3.如果全部用High NA的EUV替換,則可以削減14%的成本。

那就意味着,即使使用了非常昂貴的High NA的EUV光刻機,也能削減芯片成本(但是必須滿足兩個假設)。並且從圖9可以看出,FEOL的成本幾乎不變,但是MOL和BEOL的處理成本可以大大降低。因此,如果HighNA的EUV值在1台300億日元以下的話,不僅可以進行微縮,還能降低芯片成本,所以只能請ASML加油了。

三強爭霸的時代開始

從現在開始,晶圓廠每年投入的研發都會變得愈加困難,再加上成本昂貴,但微縮絲毫沒有停止的跡象。現在,走在微縮前頭的是TSMC,不過,在Pat Gelsinger先生掌管下的Intel有望在2nm附近追趕上來。但Intel最近變更了其技術節點的叫法,將其正式名稱為“Intel 20A”

這樣的話,今後,以站在首位的TSMC為中心,加上Samsung和Intel,三方的微縮競爭可能會激化。即便如此,委外代工的工廠TSMC為什麼會持續如此瘋狂的微縮呢?

正如我之前的文章所説,10年前的微縮,讓人感覺就像是以時速200公里的速度在歐洲的高速上飛馳。在那之後,細化的減速是事實,但即便如此,TSMC還是以時速100km的速度在田間小道飛馳,那條田間小路的寬度每年都會變窄,稍微開錯了車就要掉到田地裏,危險得很。但是,他們依然以時速100公里的速度持續飛奔着。

為什麼作為生產工廠的TSMC必須以時速100Km的速度在田間小道上奔跑呢?事實上,我認為生產工廠TSMC沒有路線圖(可以説沒有意義)。TSMC始終是委外代工,所以只能按照委託商的要求來讓TSMC生產製造。

那麼,有誰會讓TSMC“以時速100km的速度在田間小道上奔跑”呢?那就是美國蘋果公司。TSMC在Apple要求“看似不可能的微縮”後,拼命回應。

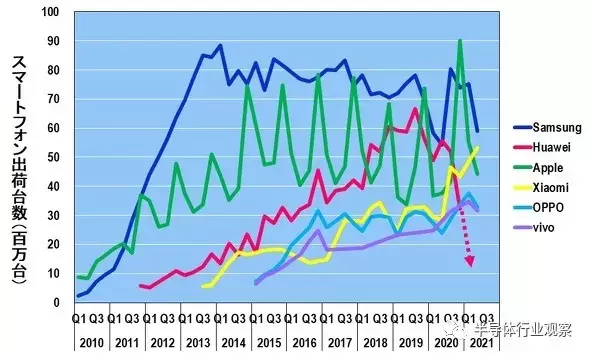

蘋果是芯片產業的最大推動者?

圖11展示出了每個季度各企業的智能手機的發貨台數。2012年以後,出貨量的首位大概是Samsung。另外,2012年左右中國華為開始了驚人的成長,在2020年第二季度(Q2)一瞬間超過了Samsung躍居世界第一,但由於美國的制裁,2020年9月15日以後,由於無法從TSMC等地採購半導體,華為之後快速失速。

而Apple最具特徵的出貨習慣就是在每年第四季度(Q4)登頂。特別是在2020年Q4季度出貨量達到了史上最高的9000萬台。這就是美國聖誕商戰的厲害之處。

蘋果公司每年7月左右發佈新型iPhone,12月的聖誕商戰中目標合計約1億台進行大量生產(實際組裝的是在中國擁有大工廠羣的台灣鴻海)。圖12展示出了2019年到2023年蘋果的新型iPhone和安裝在其上的應用程序處理器(AP)節點,以及該技術節點上他們的芯片是否應用EUV的統計。

圖12.iPhoneのAP、Technology Node、EUV應用的有無

為了趕上這個計劃,TSMC必須最晚在2021年將5nm(N5)的改良版N5P的進程提升,並在Q3製造1億個iPhone AP。與此同時,為了量產預定於2022年量產的N4(N5家族的改良版),他們今年內必須完成研發,且不得不開始風險生產。那就意味着他們似乎好像趕不上3nm了。

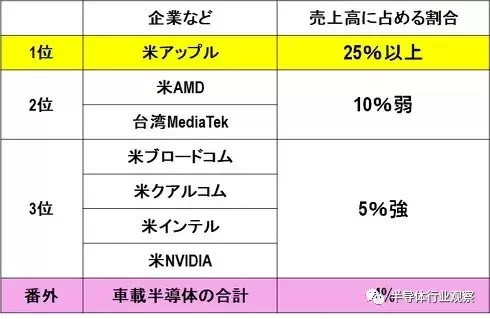

每年TSMC都必須為了蘋果而持續研發和批量生產。因為,如圖13所示,TSMC的蘋果的銷售額達到25%,蘋果是TSMC的最大客户。

摩爾定律是“人類慾望定律”

我們來計算一下,在最先進的邏輯器件中製造一億個AP有多困難。2019年為iPhone 11製造的A13芯片尺寸為98.48mm²。從12英寸晶圓計算為707個,如果將成品率設為90%(我覺得不算太高),則為636個。

在這種情況下製造1億個的話,就必須投入約150萬張晶圓。A13是使用不使用EUV的7nm(N7)製造的,據説N7的月產製造能力是12英寸晶圓150K(15萬張)左右。於是,TSMC為了A13,必須在10個月內使N7的生產線充分運轉。在此期間,AMD的CPU、NVIDIA的GPU、MediaTek的AP、Qualcomm的基帶芯片沒有進入的機會。

因此,每年最先進的邏輯器件幾乎都被蘋果公司的AP壟斷,在騷動結束後,不得不製造其他的FABLESS的尖端產品。

反過來説,TSMC的最大客户Apple每年都會在最先進的流程中要求AP的製造,因此TSMC開發了這個邏輯器件,由於其最先進的工藝,其他的無工晶圓廠(雖然有點晚了)可以得到其恩惠,也就是説生產尖端芯片。

從這樣的狀況來看,可以説TSMC之所以能持續走在世界最先進的,是因為美國的聖誕商戰。也就是説,蘋果每年12月會賣出多少新款iPhone,或是美國人是否願意購買這種新型iPhone。也就是説,TSMC“以時速100km的速度在田間小道上奔跑“的充滿幹勁的原動力,是美國人想要購買 “更高性能,更容易使用,電池更耐用” 的iPhone。

總之,TSMC的推進可以看出摩爾定律是人類慾望的法則。(更確切地説,是美國人的慾望嗎?)。

即使微縮停止,摩爾定律也不會結束

即使説明了以上的事情,也有很多人反駁説:“如果細化變成原子水平的話,定標就會停止吧。”然而即便如此,筆者仍堅持説:“即使細化變成原子水平後停止了摩爾定律也會繼續。”。

在2019年的VLSI研討上,Robert D.Clark先生(Tokyo Electron Technology Center)發表了一個題為“Selective and Self-Limited Thein Film Processfor the Atomic Scale Era”的演講。雖然他在Sunday Workshop上沒有任何配置資料。但是,Robert D.Clark的一個slide讓我深受感動。

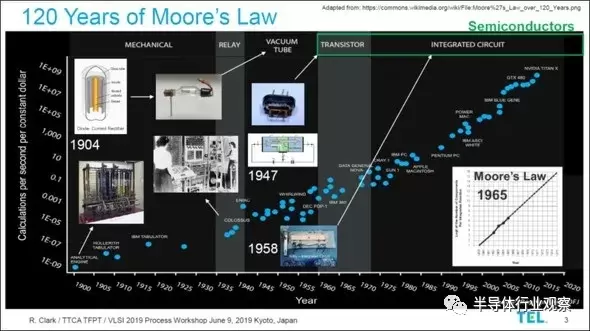

Intel的創始人之一Gordon E.Moore先生所提倡的“摩爾定律”解釋為晶體管的集成度在2年內增加了2倍。但是,Robert D.Clark先生在圖14中説明了如果縱軸不是晶體管的集成度,而是計算機的速度的話, 則“摩爾的法則從1900年到現在持續了120年”。

之前TSMC所説的7nm、5nm、3nm的技術節點只是商品名,其尺寸在芯片的任何地方都找不到。相反,隨着時代的發展,功率的下降、高速等性能提高,晶體管尺寸(或腳印)縮小,芯片尺寸變小。即,Power、Performance、Area(PPA)提高。

因此,即使微縮停止,只要PPA中的某一個在前進,摩爾的法則就不會結束。

總結

那麼,總結一下這段很長的話題吧。首先,至少到2030年為止,微縮是無法停止的。這與2007年TSMC的一個高管所預言的“hp10nm是極限”基本相同。另外,因為光刻專家總是悲觀的,所以他們説的話不太可信。證據就是,“絕對不可能量產”的EUV光刻機制造得以實現了。

並且,現在TSMC瘋狂地進行微縮,因此摩爾定律持續的原動力並非其他,而是“人類的慾望”。因此,只要人類繼續保持慾望,暫時就不會停止細化吧。並且,即使微縮變成原子級停止了,如果將晶體管的集成度以外的參數(例如計算機的速度)設為縱軸,摩爾定律也許會持續到人類滅亡為止。

因此,從目前看來,半導體微縮和摩爾定律的最大課題是:戰勝變異成德爾塔的新冠病毒。