越來越火的Chiplet_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2021-10-21 11:14

來源:內容由半導體行業觀察(ID:icbank)編譯,作者:Linley Gwennap,謝謝。領先的芯片供應商,如AMD和Intel,已經在多個產品中採用了小芯片(Chiplet)技術。根據我們的分析,這項技術可以將大型7nm設計的成本降低高達25%;在5nm及以下的情況下,節省的成本更大。我們預計小芯片將廣泛用於這些高級節點中的數據中心處理器和網絡芯片。Alphawave贊助了這篇白皮書的創作,但其觀點和分析都是作者的觀點和分析。

隨着芯片設計人員努力應對摩爾定律的放緩,許多人正在採取一種稱為小芯片的新方法。這種方法將一個複雜的設計,例如一個高端處理器或網絡芯片,分成幾個小芯片,而不是一個大的單片芯片。數據中心產品通常具有領先的晶體管數量,是小芯片的早期採用者。AMD 和英特爾已經推出了多種基於小芯片的設計,英偉達也在開發小芯片技術。我們預計小芯片技術的使用率會提高。

數據中心客户是最苛刻的客户之一,需要更高的計算性能來提供新的雲服務和更大的網絡帶寬來連接大量服務器。為了滿足這些計算需求,英特爾和 AMD 競相在其服務器處理器中塞入更多內核。英偉達強大的GPU已成為訓練大型人工智能模型的熱門工具,這些模型可以執行標準服務器無法執行的任務。大型數據中心已將以太網速度推至 100Gbps 甚至更高,同時需要具有高端口數的交換芯片。高端 FPGA 客户希望產品具有用於其前沿應用的更多邏輯門。

幾十年來,摩爾定律不斷改進晶體管技術,使芯片供應商能夠滿足這些客户的需求,但它正在失去動力。將晶體管密度加倍現在需要三到四年而不是兩年。密度的每一次增加都伴隨着晶圓成本的急劇上升,每個晶體管的成本幾乎沒有降低,這是摩爾定律的一個關鍵原則。每個新晶體管節點的功率和速度增益也有所減少。簡而言之,遷移到下一個節點變得更加昂貴,而提供的收益卻更少。

小芯片提供了一種創建更高級設計的替代方法。通過使用兩個或更多芯片,公司可以將設計的晶體管數量增加到超出單個芯片所能容納的數量。它可以將較舊的節點用於一些小芯片以節省成本,同時在需要最佳性能的地方使用前沿節點。對於複雜的設計,這種方法可以降低製造成本。隨着設計轉向 5nm 及以下,成本上升提高了小芯片的經濟性。

數據中心中的小芯片

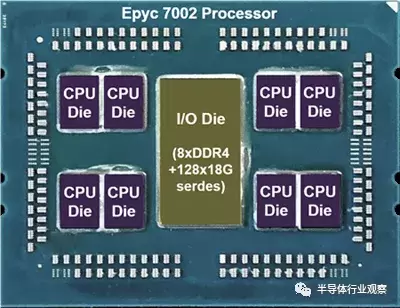

AMD 是第一個引入小芯片架構的主要供應商。其最初的 Epyc 服務器處理器代號為 Naples,於 2017 年推出,在單個封裝中具有四個相同(同類)小芯片,總共提供 32 個 CPU 內核。2019年,該公司又推出了第二款Epyc設計(“羅馬”),使用8塊CPU芯片實現64核,是當時英特爾最好的處理器的兩倍多。。Rome 設計增加了第九個小芯片,它集中了所有的 DRAM 和 I/O 電路,如圖 1 所示;該芯片使用較便宜的 14 nm節點,而 CPU 小芯片使用7 nm晶體管來提高速度和功率。AMD 為其最新的第三代Epyc 處理器(“米蘭”)保留了相同的小芯片配置。

對於Agilex FPGA,Intel採用了芯片,但採用了不同的方法。Agilex將設計的主要部分(包括可編程邏輯、CPU子系統和DRAM控制器)保留在單個芯片上。這些芯片(Intel稱之為tiles)實現額外的I/O連接,如高速serdes、PCIe Gen5、高帶寬內存(HBM2)和Optane持久內存。這種方法允許公司只需更改已安裝的芯片即可提供具有各種I/O組合的Agilex產品。英特爾甚至可以創建特定於客户的芯片來添加特殊功能。公司可以添加新的小芯片,例如112Gbps的serdes或HBM3,即使在基本芯片已經投產之後。

Barefoot Networks 現在是英特爾的一部分,在其名為 Tofino 2 的 400G 以太網交換芯片中使用了小芯片。與 Agilex 一樣,該產品將中央邏輯保留在單個芯片上,但將其 32 個以太網端口劃分為四個小芯片。這種劃分簡化了封裝中 I/O 信號的佈線。我們相信以太網小芯片採用 16nm 技術,相對於將它們保留在主要的 7nm 芯片上,降低了成本。該公司還可以在完成其餘複雜設計之前開發和測試高速以太網電路,從而降低開發風險。

其他生產中的小芯片設計包括華為 Ascend 910,它包括一個計算芯片和一個獨立的 I/O 芯片。它使用硅襯底來連接兩個芯片以及四個 HBM2 堆棧。有傳言稱,英偉達的下一代 GPU(也稱為 Lovelace 或Ampere Next)將使用小芯片。英特爾計劃在未來的處理器中轉向小芯片,優化 CPU、GPU 和 I/O 電路的技術節點。其針對數據中心和超級計算機的 Ponte Vecchio GPU 分為多個小芯片,儘管英特爾尚未透露 2022 年產品的細節。最終,該公司希望通過在小芯片上實現單獨的功能塊、通過混合搭配過程創建新產品來減少處理器設計時間。.

小芯片的好處

將大芯片分成更小的小芯片通過提高產量來降低製造成本。傳統的良率模型假設缺陷在晶圓上隨機散佈,並且芯片上任何地方的缺陷都會使其無法使用。因此,大芯片比小芯片更可能包含缺陷。掩模尺寸 700mm²的設計(可能的最大尺寸)通常會產生大約30% 的合格芯片,而 150mm²芯片的良品率約為 80%。即使考慮到更多數量的小芯片,這種產量的提高也節省了大量成本。

為了提高大芯片的良率,一些供應商包括可以容納某些缺陷的冗餘電路。例如,一塊 SRAM 可以有額外的行來替換任何失效的行。這種方法增加了芯片面積,但減少了易受缺陷影響的“有效面積”。小芯片設計可以去除冗餘電路,減少芯片面積,同時仍然提高產量。

進一步的成本節約來自使用不同的製造節點創建不同的(異構)小芯片,這在單片設計中是不可能的。例如,對於密集封裝的邏輯和存儲器,7nm 晶體管比 16nm 晶體管便宜,但 I/O 接口通常具有模擬電路和其他無法從較小節點中受益的大型功能。出於這個原因,許多小芯片設計將 I/O 功能隔離到在舊節點中製造的單獨芯片中。一些邏輯電路(例如加速器)可能不需要以與主處理器相同的最大時鐘速率運行,因此可以在中間節點中製造。使用較舊的工藝技術可以將這些小芯片的製造成本降低多達 50%。

公司可以通過在多個產品中重複使用小芯片來減少設計時間和流片費用。例如,AMD 在其第一代 Epyc 和 Ryzen 產品中使用了相同的小芯片設計;PC 處理器使用單個小芯片,而服務器處理器最多包含四個小芯片。此外,AMD 可以通過改變封裝中的小芯片數量來輕鬆提供廣泛的 Epyc 核心數量。相比之下,英特爾通常會流片出三款至強芯片,每款都有不同的核心數,以涵蓋每一代的全系列型號。同樣,Barefoot 可以通過更改以太網小芯片的數量來擴展其交換機的端口數。

I/O 接口故障會導致產品無法啓動。為了降低這種風險,Barefoot 將其前沿的以太網設計轉移到一個單獨的小芯片上,使其能夠獨立於主邏輯芯片開發和測試該電路。儘管其 Agilix FPGA 已經開始出貨,但英特爾計劃開發新的小芯片以隨着時間的推移升級產品的 I/O 功能。

小芯片可以通過實例化比單個芯片容納更多的晶體管來實現晶體管數量“超摩爾”的增益。Xilinx 從 2011 年開始使用這種方法,當時它將四個中型小芯片組合在一起,提供的門數是當時最大的單片 FPGA 的兩倍。AMD 的 Rome產品在 9 個小芯片上集成了 400 億個晶體管,而英特爾的現代 Skylake Xeon 單片設計只有 80 億個。然而,對於許多前沿產品,功耗 (TDP) 在設計達到最大芯片尺寸之前限制了晶體管的數量。

小芯片成本研究

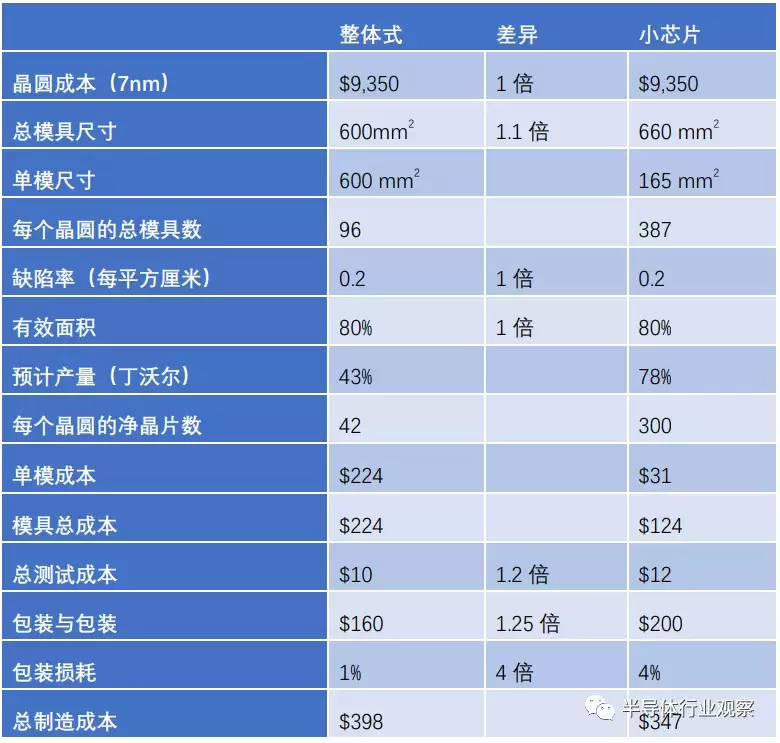

設計人員可以通過多種不同方式實現小芯片。有些使用同構的小芯片,而其他的則將計算和 I/O 功能隔離到不同的小芯片中。硅襯底在小芯片之間提供密集的佈線和更大的帶寬,但有機襯底的成本更低。作為一個簡單的案例研究,讓我們來看一個假想的處理器,它可以被分成四個同質的芯片。單片版本需要 7nm 節點中的 600mm²和昂貴的 60x60mm有機 BGA 封裝,具有許多佈線層來處理大量 I/O。該設計包括一個具有冗餘行的相當大的內存,留下了 80% 的有效區域。

劃分這種設計可能會產生四個 150mm²的芯片,但小芯片需要額外的芯片到芯片連接區域,這需要比芯片上信號大得多的驅動器;為此,我們估計有 10% 的開銷。即便如此,如表 1 所示,較小芯片的良率幾乎是大型單片芯片的兩倍,從而節省了 100 美元的總芯片成本。

然而,由於測試四個芯片而不是一個芯片的開銷,測試成本略高。由於多種原因,該包裝已經很昂貴,但成本會大幅增加。如上所述,小芯片的總面積要大 10%,並且封裝需要小芯片之間有一些空間,因此它增長到 60x80mm²。將 I/O 分佈在更大的封裝中減少了佈置這些信號所需的層數,但新的芯片到芯片信號增加了佈置的層數;我們假設這些變化不重要,並且層數保持不變。最後,多芯片封裝的組裝成本會更高,組裝損耗也會更高。這些封裝成本抵消了大約一半的芯片成本節省,淨收益為 13%。

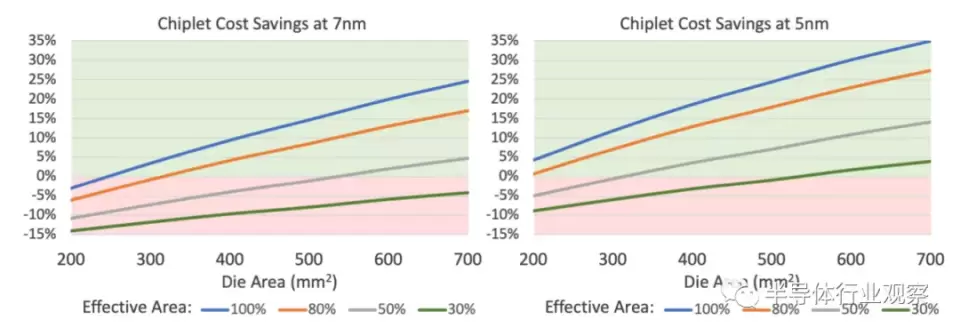

將此成本模型擴展到其他示例,我們看到了在幾乎沒有冗餘或沒有冗餘的情況下最大的節省。在 7nm節點中,小芯片降低了單片設計的成本,有效面積大於 400 mm²,如圖 2a 所示。根據我們的模型,對於相同內核佔用 50% 或更多芯片面積的高度常規處理器,小芯片通常會增加製造成本。在這種情況下,冗餘內核會提高大芯片的良率,從而降低小芯片的良率增益。

在更先進的製造節點中,小芯片在更廣泛的設計中具有優勢。例如,在5nm 工藝中,晶圓成本幾乎翻了一番,達到 17,000 美元。因此,轉移到更小的芯片所節省的成本更大,更容易抵消封裝成本的增加。根據我們的模型,5nm 的淨成本節省比 7nm 高約10%,這意味着小芯片可以降低小至 200mm²的裸片成本。即使對於有效面積為 50% 的處理器,在 300mm² 以上也會節省成本。儘管 3nm 的晶圓成本尚未確定,但成本節約肯定會再次上升,將小芯片的盈虧平衡點推到150mm²以下。

結論

我們的成本分析表明,用於大型數據中心芯片的芯片組架構具有相當大的優勢。在 7nm 中,我們估計分解非常大的芯片最多可節省 20% 的成本,而小至 400mm²的芯片則節省較少的成本。不斷上漲的晶圓成本提高了小芯片方法的價值,將超大芯片的潛在節省推至 5nm 的 30% ,在3nm 上則可能達到 40%。在這些先進的節點中,即使是 300 mm²或更小的中等尺寸芯片,小芯片也會很有吸引力,儘管這些較便宜的設計節省的成本自然會更小。該分析排除了其他潛在好處,例如通過在尾隨節點中構建部分設計來降低製造成本,或通過在多個產品中重複使用小芯片來降低設計成本。

該分析與迄今為止的小芯片部署一致。如果作為單個 7nm 芯片實施,大多數生產中的小芯片產品將是掩模尺寸(或更大),這使得這種方法最適合昂貴的數據中心芯片。一些供應商將他們的 PC 處理器稱為小芯片設計,但他們只是將主處理器和南橋封裝在一起,英特爾已經這樣做了好幾年。到 2022 年,我們預計大多數 PC的GPU 、以及一些中端網絡芯片和 FPGA將採用小芯片設計技術。設計內部 ASIC 的公司也將開始採用該技術。

小芯片並不適合所有設計。PC 和智能手機處理器的尺寸通常為 150 mm²或更小,因此它們不會受益。英特爾和英偉達等供應商通過減少某些產品型號的核心數量以容納有缺陷的核心來提高產量;這種方法還降低了小芯片的成本效益。異構小芯片設計(例如 Agilex 和 Ascend)實際上會增加昂貴的流片數量,儘管其中一些流片通常會轉移到較舊的、成本較低的節點上。在多個產品中重用小芯片可以抵消額外的流片成本,但考慮到不同產品細分和跨代的需求不同,到目前為止,我們很少看到重用示例。

然而,許多數據中心芯片都是小芯片技術的最佳選擇。該技術已經引起了領先供應商的極大興趣,AMD、英特爾和英偉達都在出貨或至少開發基於小芯片的產品。正如這些供應商所證明的那樣,優勢不僅在於節省成本,還包括構建比任何單片芯片都更大的設計、通過解耦新技術降低進度風險以及提供靈活的產品配置。其他在高級節點(包括 ASIC)中構建大型設計的公司應該評估這種新方法,以確定他們是否可以從小芯片技術中受益。