大話FPGA-“萬能的芯片?”_風聞

歪睿老哥-芯片研发工程师-聚焦芯片行业的那些事,唯武侠与芯片不可辜负2021-10-22 10:26

説起FPGA之前,先提個問題。

芯片的本質是什麼?

老哥認為芯片的本質是電路!

簡單來説,數字芯片,不論多複雜,其底層就是 與,或,非的組合。

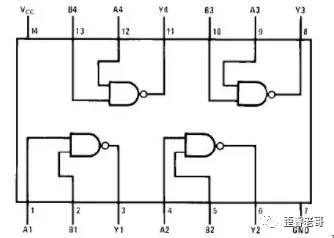

這個是某寶上可以買到的世界上簡單的芯片之一, 74LS系列,很便宜,兩毛錢;

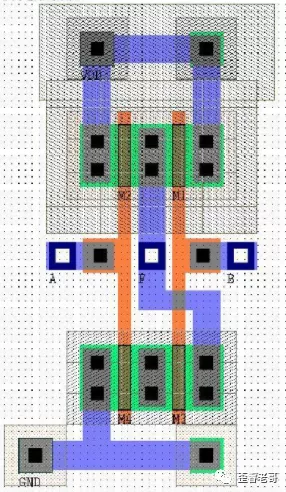

其功能就是二輸入與非門。這是一個最簡單的芯片,其電路和版圖如下

上圖中一共4個二輸入與非門。

而CPU或者GPU等大芯片,有幾千萬門甚至上億門的電路。

但是如果我們深入到大芯片的底層,就會發現這些大芯片也是一個與非門,或非門,等邏輯門組成的。

這就是電路,CPU和GPU也是一種電路的組織形式。

無論多複雜的芯片,都是芯片設計工程師通過硬件描述語言(HDL)來描述電路。

看起來像是和軟件工程師一樣,都在敲代碼,在編程,實際上是在搭電路。

EDA工具把語言轉換成電路,最終得出這個版圖(GDS)。然後這個版本提交給廠家生產。流片廠家把GDS變成硅。封裝廠家完成硅 (DIE)到 CHIP的封裝。

這個過程和設計PCB電路基本上是非常相似的。

都是電路轉換成PCB 到廠家製版。

我們所説的卡脖子,目前看,主要是製造環節,也就是從版圖到硅的階段。其他也有,但是這個問題這個有時間找專題另説。

今天主要説一下 ,設計一款芯片研發最大的問題是啥?

有兩點是大家公認的。

第一,研發迭代週期長:

大芯片花費了一年或者2年研製,這個很常見。或者因為功能缺陷,或者市場變化,最終沒有賣出去,又要重新迭代。這個就是非常恐怖,小的芯片公司,因為芯片失敗,錢花光,直接一波流帶走也是很常見的。

第二,芯片投入高:

芯片研發包括流片成本,IP成本,人力成本等。28nm的MASK在1000萬,12nm接近2500萬,除此之外還有人力,IP等成本。研發一顆28nm的芯片總投入成本投入大幾千萬還是有的,7nm和5nm更是幾億的投入。這麼高的成本(NRE),將來要分攤到每一顆芯片上去的。

如果一個項目或者需求,只有幾千顆或者幾萬顆的量,是否值得來去研發芯片就是一個很大的問題。

流片不合適,那麼沒有一種替代的方案?迭代週期短,代價小的實現這個電路的需求。

FPGA,他來了!

1:FPGA:實現電路的電路

FPGA

Field Programmable Gate Array。

現場可編程門陣列。

FPGA和專用芯片不同。

可以編程。

文章開頭説過了, 芯片的本質就是電路。

那麼FPGA的本質是什麼?

FPGA本質也是一種芯片。

但是可以也可以實現數字電路功能,如CPU,GPU,NPU等這些電路,都可以放在FPGA內部實現,效率另説。。

那FPGA的本質就是可以通過編程實現電路的電路。

這個是怎麼做到的?

或者説,什麼樣的電路可以實現與或非這些基本操作

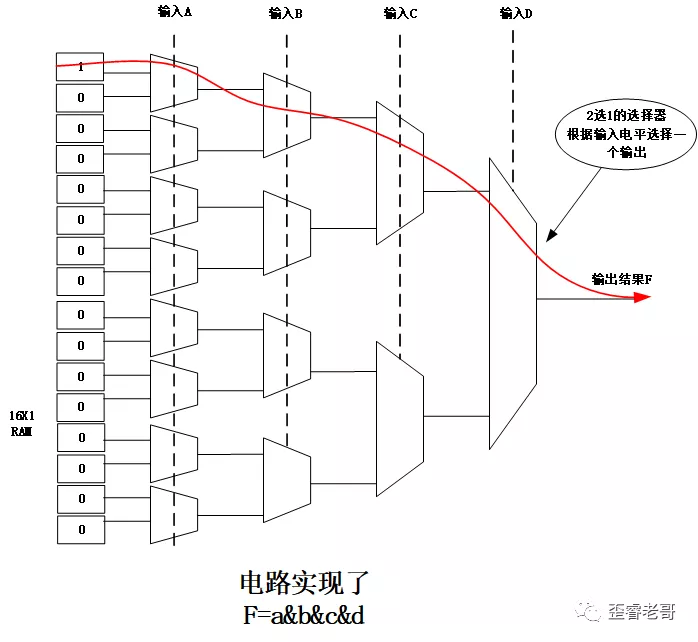

我們以 F=A&B&C&D 這個電路舉例:

一個16x1的RAM,這個RAM的每一bit都可以編程為0或1。

這個RAM有4位地址, DCBA。通過這4bit選擇RAM的輸出。

通過配置RAM中不同的值,實現輸出F 和輸入A,B,C,D的關係

上圖中,我們把16bitRAM 配置為 0000000000000001 ,這個電路 則等效 F=A&B&C&D;

只有A=B=C=D=1時, F=1,其他情況 F=0;

完美實現了 F=A&B&C&D;

重要的事情再説一遍;

16bitRAM 配置為 0000000000000001 , 則等效F=A&B&C&D;

那麼現在“0000000000000001” 這串數就是FPGA的編程。

這就是FPGA最基本的原理;

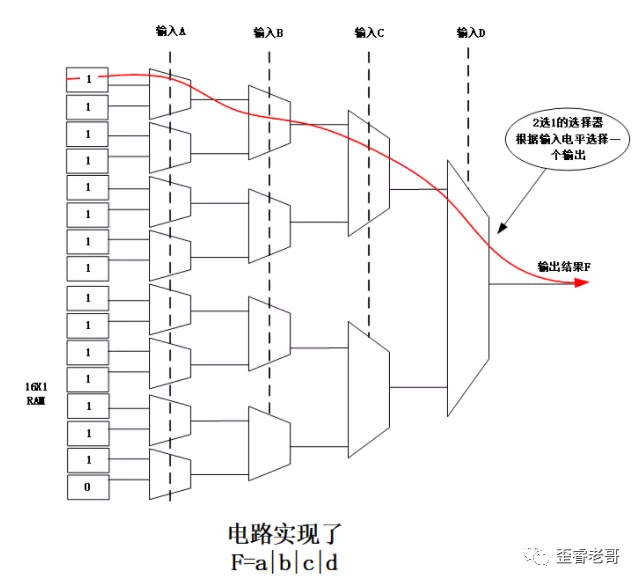

舉一反三,如果實現電路 F=A|B|C|D 。

這個電路如何編程:

16bit RAM 配置為 01111111111111111, 則等效F=A|B|C|D。

大家可以試一下:通過配置16bitRAM 的值,可以實現A,B,C,D四個輸入的任何邏輯操作。

FPGA就是利用了這個轉化,具備了描述任何電路的能力。

上圖這個結構在FPGA中有一個專有名詞,叫做LUT ,lookup table( 查找表)。

LUT就構成了所有FPGA的最基本的單元。

LUT只能實現數字組合邏輯,所以又添加了一個寄存器flipflop (ff),可以實現數據的鎖存;

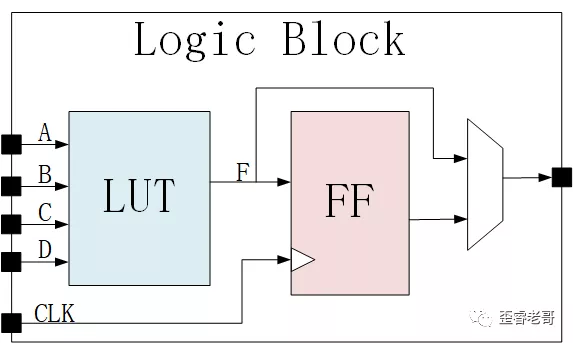

如下圖所示:LUT+寄存器構成了現代FPGA基本結構。

FPGA的基本結構,就是依靠如此簡單的電路實現了無比複雜的邏輯。

這個包括LUT和FF的基本結構,這兩個合併成為一個基本的邏輯單元(LOGIC BLOCK)。

這種能夠實現ABCD四個輸入計算的LUT的叫做4輸入LUT,此外還有5輸入,6輸入等等變種。

萬變不離其宗。

這種結構,從FPGA誕生以來,就沒有怎麼變過。

這個電路,也可以看作是一個最小的FPGA。

現在能實現一個功能的芯片,少則幾萬門,多則幾千萬門,上億門。

單純靠這個電路實現,這就是開玩笑了。

那麼就需要無數的LUT和FF來實現,。

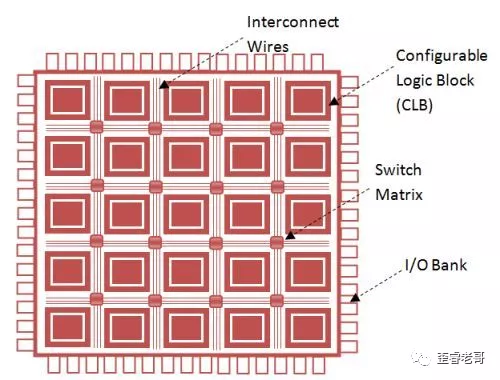

FPGA就實現了一個無數 Logic Block(Logic Block內部就是LUT+FF)的陣列,中間用佈線資源連接起來。

把互聯和邏輯單元結合起來就是一個FPGA芯片,圖如下所示。

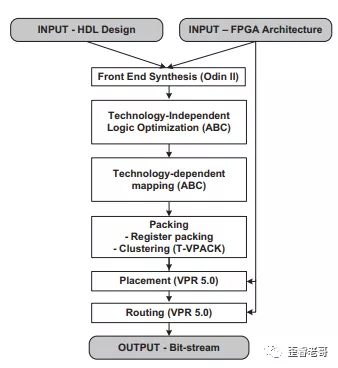

一個典型的FPGA開發流程如下。從HDL(verilog的電路描述語言)到配置文件 bit流

相比一下,專用芯片的開發流程從HDL(verilog的電路描述語言)到硅。這個時間就長多了。

這些bit流包括啥?

開頭説過了,16bitRAM (LUT)配置為 0000000000000001 ,

則等效F=A&B&C&D;

FPGA最終生成的Bit-stream流,包括 LUT 的配置文件,以及佈線資源的配置文件。

到這裏,FPGA的設計及編程就完成了。

簡單明瞭!

2:EDA工具:從知到行的距離

看起來設計一個FPGA芯片也不復雜。

電路不復雜,市場上高性能的FPGA,可選擇的餘地不多。

從知到行,這裏面有一個巨大的鴻溝,

按照本文開頭的原理,假如一個廠商設計完畢了一款FPGA芯片。

等到給客户使用的時候,就碰上了一個大麻煩。

EDA工具。

如果給客户提供FPGA芯片,則需要配套提供給客户一個EDA工具。

沒有EDA工具,難不成讓客户手動生成FPGA的bitstream的文件。

芯片都做出來了,EDA工具,還難嗎?

難,真的難!

這是一個巨大的坑。

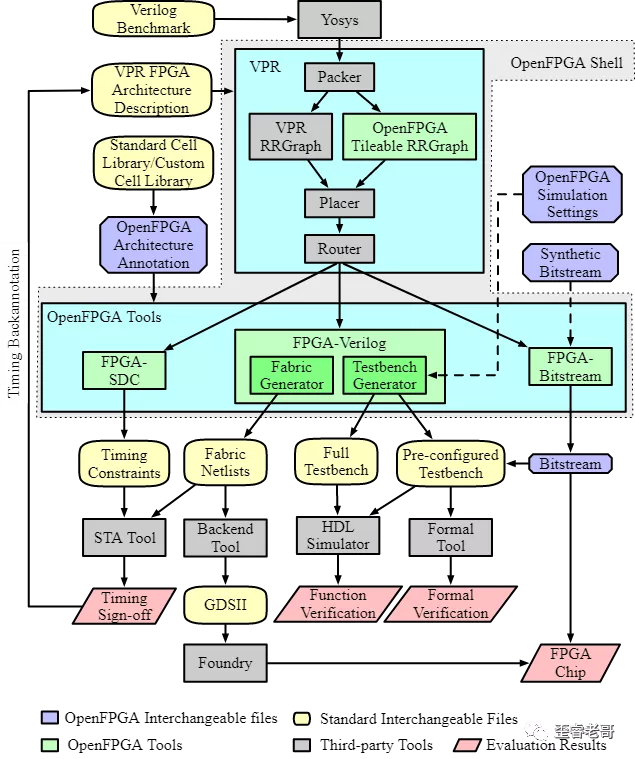

下圖是一個 開源的FPGA的設計流程(OpenFPGA),我們可以看看,即使一個開源項目,其涉及到的EDA工具最少都要有哪些?

這些需要給客户的EDA工具包括:

1:綜合工具

2:佈局佈線工具

3:bit生成工具

4:時序分析工具

5:仿真工具

6:嵌入式邏輯分析儀器等調試工具

7:功耗分析工具

這些還算是最少的集合,但已經比一個CPU芯片提供給用户GCC編譯工具要難多了。

老哥裝過某司的EDA工具,這些大小都是十幾個G,比windows安裝盤還要大。

如果CPU的GCC工具難度是1,FPGA的EDA工具的難度就是10到100。

借用《讓子彈飛》裏的一段話:

項目成功了,芯片功勞怎麼才佔7成。

七成是EDA的,芯片也就三成。

就這三成,還要看EDA的臉色。

辛辛苦苦半天,做出來芯片,還要看EDA工具的臉色。

看看EDA都有哪些“臉色”?

以上圖的佈局佈線工具為例,看起來就比較複雜。

如果做不好,整個FPGA的利用率極低,還布不通,你説重要不重要。

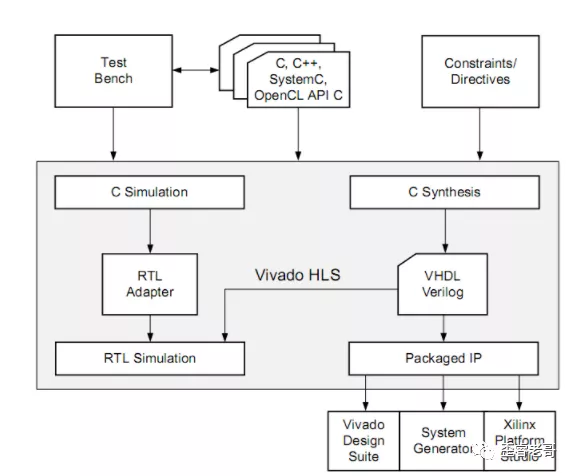

除了傳統的EDA工具,實現HDL,例如verilog這種編程之外,還包括HLS這種高層次綜合的描述語言。

HLS的引入使軟件工程師也能參與到FPGA設計中來,把電路開發屏蔽掉,直接開發軟件,這個就更是EDA工具的能力了。

但是,這個本質上,講高級語言(C,C++)轉換成硬件描述語言(HDL),在通過綜合工具轉換成電路。

好處是,更貼近軟件工程師的習慣,缺點就是加了一層轉換,帶來了效率的損失。

3:FPGA的架構:融合超越

文章開始説了,FPGA就是Logic Block,內部主要是(LUT+FF),以及佈線資源。

除了這些。

FPGA還有很多硬核IP,也叫做宏單元。

例如PLL,SERDES,RAM等常規IP的。

隨着現在芯片的演進。

FPGA內部也集成了很多新的東西。

這些新東西中,比較有特色的就是CPU,在FPGA內部集成了硬核CPU系統,甚至可以運行OS(操作系統)。

這樣CPU+FPGA。

CPU軟件編程,FPGA 硬件電路編程,

這個就是雙劍合璧,更勝一籌。

同樣serdes也是高端FPGA的必須模塊,沒有serdes,FPGA就是孤家寡人,沒有辦法實現和其他芯片電路的高速互聯。

現在與外部器件連接,支持比如PCIe,SATA,10G/100G ethernet這些高速協議。

數字信號處理,FPGA應用於數字信號處理等計算密集型任務,如雷達等等

所以,FPGA內部也集成了了很多DSP單元,實現乘法等操作。

為了在人工智能時代分一杯羹,有的FPGA內部集成了用於AI處理的神經網絡加速的硬核。

總結一下,除了LUT,FPGA內部集成硬核IP包括:

1:RAM:用於實現存儲資源;

2:PLL:提供高速的時鐘信號和資源;

3:DSP:乘法操作,濾波器,數字信號處理模塊;

4:SERDES:實現PCIE,SATA,FC,100G ethernet等高速接口

5:CPU系統:提供軟件編程開發能力;

6:NPU硬核:提供AI處理加速;

而根據市場需要,還可能添加更多的硬核IP 與傳統的FPGA進行融合。

融合更多功能IP。

這就是FPGA架構未來的趨勢。

4:FPGA優勢:解決問題才是王道

FPGA和CPU有什麼區別和優勢?

我們討論一種架構的優劣,重點是解決了什麼問題?

而不是CPU與FPGA,孰優?

只有放在固定的應用場景下,才能説哪種架構更適合解決這些問題。

FPGA編程是電路,本質上還是可以看作,邏輯門(與或非)等等效電路。

CPU是指令操作,運行的是軟件。

FPGA是時間並行運行的,而CPU是時間串行的,單CPU核總是需要一條一條來執行指令來實現功能(也有指令級並行,但原理不變)。

FPGA的並行度較高,相比CPU的計算方式,數據吞吐量大,時延控制比較好。

但是CPU的頻率很高,可以運行操作系統,作為通用計算單元非常靈活,並不是FPGA更能做的。

FPGA更適合做ASSP,配合CPU做專門的運算單元使用,適合專一的大數據量的計算。

FPGA既然是”萬能的芯片“,似乎那就可以替代實現所有芯片功能。

是不是可以不研發專用芯片,只用FPGA。

相比專用集成電路:FPGA有三個劣勢

1:面積大,成本高:

和專用集成電路(芯片)相比,FPGA由於採用LUT來表徵基本邏輯門單元,所以其面積粗略來比是專用電路的10倍,所以其成本簡單類比也會高很多。

2:面積大,功耗高:

同樣功耗也沒有優勢,做低功耗設備,例如手持的供電式設備,基本不太可行。

3:運行頻率低,計算效率低。

FPGA內部LUT之間,由於其互聯較長,導致FPGA的頻率相比同工藝下的ASIC也是慢很多。專用電路門與門之間的延遲要小很多。

但是,FPGA優勢也很明顯。

FPGA最大的優勢,就是靈活性高。

用FPGA不用重新流片,節約了NRE成本。

在一些雷達,5G,網絡,存儲,高性能計算等數據密集型計算領域都有廣泛的應用。

特別是需求不明確,量不大,不值得做芯片,或者,需求老在變化,FPGA都是不錯的選擇。

intel收購後altera後, FPGA的重心變成了數據中心市場,特別是利用FPGA在數據中心加速方面,投入頗大,最新的intel的IPU其中是FPGA技術,用於數據中心基礎設施的卸載,也是類似DPU的一種實現。(見上一篇:大話DPU—從網絡到數據)。

目前很多家DPU都是用Intel和Xilinx的FPGA實現的。

這個就是DPU需求不固定,數據中心對於DPU的需求一直在變化的一種體現。

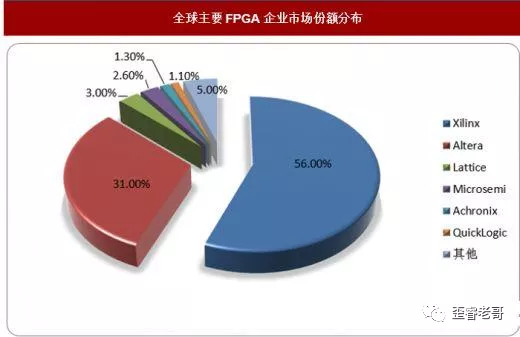

FPGA全球市場2018年大約60億美金,Xilinx 和Altera 是這個FPGA市場上最重要的提供者,其他都是比較小的公司。(2015年英特爾宣佈以167億美元收購FPGA廠商Altera),給其他家留的份額就不多了。

老哥早些年,這兩家FPGA都使用過,各有千秋。

國內也有很多FPGA的公司,有的出貨也比較客觀。與國外巨頭相比,處於解決了有無的問題階段,能夠滿足部分國產化需求。其容量,性能,特別是EDA工具方面,有明顯的差距,還需要繼續市場的磨練。

這裏舉兩個國產FPGA的非典型案例,非常有意思。

2014年,俄羅斯併入克里米亞,美國出售制裁,美國對俄羅斯的封鎖禁運也是很厲害,俄羅斯芯片告急,特別是高端的FPGA芯片,某司FPGA芯片抓住這個機會,解決了國際友人的燃眉之急,成就了某司的FPGA出口,也獲得不錯的利潤。

另外,某手機大廠手機屏幕是有特殊轉碼格式的,所以如果返修,只能使用原廠屏,其他屏幕格式對不上,原廠屏價格很高。某司就定做了一批超小型FPGA,實現了手機屏的解碼,中國的屏幕提供廠很多(LCD+LED等等),直接就可以替代原廠屏,在手機返修屏市場也是賣的風聲水起。

在這些細分領域,找到了定位,實現了很大的突破,不論是利潤還是數量。

如果有數量幾十萬片,幾百萬片,甚至更多,做專用芯片更合適。

如果沒有那麼多數量,需求又不固定,用FPGA更合適。

芯片設計中,其中有個環節叫做FPGA原型驗證,FPGA原型驗證就是把芯片代碼放在FPGA做原型實現,加快芯片設計迭代的速率。

本文開始説:FPGA特性,就是能夠描述芯片電路。

所以數字芯片流片之前,用FPGA裝入芯片邏輯來等效測試,也是非常重要的一個環節。

從這個角度看,FPGA和芯片(專用集成電路)從來就不是對立的,

FPGA,萬能芯片,從功能上看是萬能的,理論上可以實現所有功能。

但是從,PPA上看,性能,功耗,面積(成本),這三個維度來衡量,又是非常受限的。

FPGA也在進化,拓展更多的領域,滿足那些變化的市場需求。

也有部分市場需求更為固化,被專用芯片所取代。

萬能的芯片,變化的應用。

找到市場定位,解決用户的問題,才能獲得一席之地。

FPGA是如此,芯片也是如此。