FPGA,大戰繼續!_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2021-12-13 16:25

來源:內容來自半導體行業觀察(ID:icbank)編譯自seekingalpha。隨着賽靈思併購案的順利進行 ,AMD與英特爾在 FPGA 領域數十年的競爭還將繼續。雖然FPGA不是一個被密切關注的細分市場,但也會出現這樣諸如此類的問題,那就是誰將成為FPGA領域的領導者?

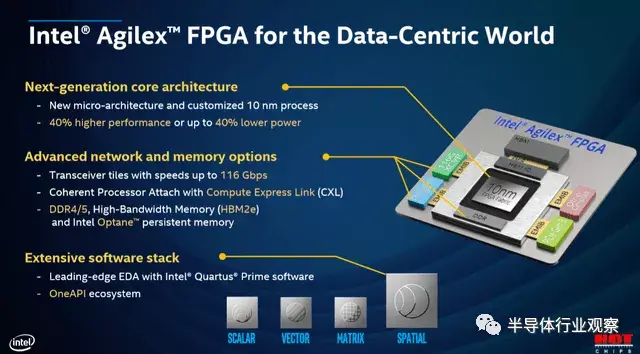

不久前回顧了英特爾的線上發佈會,雖然 Ice Lake-SP是重點,但實際上Agilex FPGA才是那次發佈會的“隱形冠軍”。英特爾強調它是 FPGA 領域無可爭議的領導者,如果英特爾能夠將其轉化為市場份額的增長(雖然目前還沒有證據表明這一點,但這可能是由於產品短缺造成的),那麼 賽靈思 以及AMD可能會陷入困境。從長遠來看,AMD和賽靈思所面臨的更大風險是英特爾的下一代 FPGA,得益於英特爾的封裝優勢,下一代FPGA將採用突破性的架構,性能會有前所未有的提升,進一步提高英特爾的領先地位。

什麼是 FPGA?

簡單地説,FPGA 是可編程邏輯設備,通過與其他類型芯片比較可以更直觀得理解:CPU 可以通過軟件完全編程,ASIC中特定的算法是在硬件中進行的,而 FPGA 可以在邏輯(布爾邏輯體系)級別就進行“編程”。這意味着邏輯將根據算法(如 ASIC)進行調整,也可以重新編程來迎合不同的算法,進而決定固定功能芯片和 CPU 之間的速度、靈活性和效率特性。性能優異的 FPGA 還可以通過 DSP 提供相當多的計算能力,甚至可以與 GPU 相媲美。隨着AI 的興起,英特爾 和 賽靈思 都進一步增加了對低精度的支持(例如 INT8),甚至在一些 FPGA 中增加了矩陣運算(類似於英偉達的張量核心—— Tensor Core)。(這也表明英偉達在 AI 方面成功的主要原因是2017年時憑藉 V100 快速上市,從而形成了先發優勢。此外,賽靈思和英特爾(以及許多初創公司)都已經表明可以添加 Tensor Core到 GPU 以外的其他芯片,並能夠提供具有競爭力甚至卓越的性能。)

收購賽靈思

關於AMD收購賽靈思,我在傳聞剛出現時就進行了分析。

回顧CPU 和 FPGA 的協同效應,從英特爾五年前的收購中,我們就可以知道:FPGA 可以用作數據中心加速器、AI 加速器、SmartNIC(智能網卡) 以及網絡基礎設施中的加速器。但我也指出過,迄今為止,這些協同效應並沒有給英特爾的 FPGA業務帶來太大的增長。在這方面,儘管(獨立的)賽靈思的表現可能稍好一些,但其財務狀況也喜憂參半。

作為這次討論的補充,當時在電話會議上提出了以下問題,可能值得完整引用,因為我看到許多看好 AMD 的人認為, AMD的收購與英特爾不同,但我卻不這麼認為。

**Stacy Rasgon:**我關於賽靈思的問題是,對於一家購買 FPGA 的 CPU 公司,顯然有人在你的競爭對手嘗試之前已經嘗試過,就這一點而言,它並不是非常成功。您認為您對 賽靈思 的看法與 英特爾 對 Altera 的看法有何不同?您從英特爾 收購Altera中遇到的問題中學到了什麼?

**Lisa Su:**經過一段時間的考慮,我認為不同之處在於賽靈思是市場領導者。從過去幾年裏業務增長情況來看,他們的市場份額一直在增長。我也認為兩家企業的執行情況都非常好。

你可能會問,為什麼現在我們對我們的基礎業務感覺很好。別人可能覺得我們的業務是互補的,確實從產品和市場的角度來看,它們十分互補。但其實在數據中心焦點、技術戰略等方面,我們是存在一些重要的交叉點。

我們都是技術領先者,都與台積電合作,也都喜歡這種模塊化設計環境,而賽靈思在2.5D、3D集成等方面處於領先地位。此外,我們都致力於軟件和開源,所以可以明顯看到很多隱藏在幕後的協同效應。未來,你可能看到我們的路線圖規劃。

最後,我想説的是,我認為我們的文化非常一致,Victor和我都是工程師。我們熱愛所擁有的共同願景的技術,我真的非常高興他能加入我們。對於此次收購將會對行業和我們的合資公司帶來什麼,我們也有一個大膽的願景。我認為這就是我們所看到的不同之處,正如你所知道的, Stacy。

我的意思是我們不是為了併購而進行併購,而是因為這對於我們而言,都是一個難得的機會,沒有比 賽靈思 更好的行業匹配者了。Victor,你來補充一些你的看法。

**Victor Peng:**我認為這次收購與英特爾那次完全不同。我認同Lisa所説,不僅僅是在數據中心,我們對其他正在發生的轉型都有着共同的願景,比如在邊緣甚至端側應用中。我非常高興能再次加入AMD和賽靈思團隊。

並且我認為我們確實有非常相似的文化,都注重創新、執行和團隊合作文化,既適用於公司內部,也適用於客户。我認為這就是全部。我們將給客户創造巨大的價值,隨着時間的推移,我們將會把 Lisa 談到的那些基礎技術展現給大家。很明顯,我個人覺得我們將很好地整合。

確切的説,將Altera收購認為是不成功的案例其實是一種誤導。與 AMD 和 賽靈思 管理層希望投資者相信的相反,英特爾 收購Altera與 AMD 收購 賽靈思 其實完全相同,都是在CPU裏添加一個 FPGA。然後將其作為加速器或 SmartNIC 放入數據中心以進行卸載,或用於綜合網絡基礎設施組合,又或用於尋求其他邊緣機會。

這是英特爾執行其收購時的策略,我看不出AMD收購賽靈思有什麼不同,都是在擴大機會。還有兩個論點:

就技術而言,Altera-英特爾 的協同效應實際上要廣泛得多。有些人可能還記得,早在英特爾代工服務之前,Altera 是英特爾第一個具有里程碑意義的代工客户,不僅採用英特爾的代工,同時也是英特爾業界領先的先進chiplet封裝(帶EMIB)的主要用户。此外,英特爾的 oneAPI 軟件計劃還包含 FPGA,創建一個統一的開放式編程模型,涵蓋 CPU、GPU、FPGA 和 NPU。上市協同效應以及整體產品組合也有利於英特爾。英特爾在 (5G) 網絡基礎設施整體上處於領先地位,而 AMD 則在這個市場上仍然缺席。(儘管看好 AMD 的人認為這次收購讓 AMD 能夠擴展到新市場。)英特爾不僅擁有 ASIC 業務,還收購了 Easic 以獲得更廣泛的產品組合:英特爾稱之為從可編程芯片到非可編程芯片的“邏輯連續體”。

儘管一些協同效應仍有待觀察,就像我在 2020 年 10 月之前的分析中所説的那樣,鑑於AMD近 2000 億美元的市場估值,此次收購表明並符合 AMD追求進一步增長的目標,這與英偉達想要收購Arm沒什麼不同。因此,與上述管理層引述相反,可以認為此次收購與英特爾在 2015-2016 年的收購相同,這意味着 AMD 在追求 CPU + FPGA 協同戰略方面至少落後英特爾五年。

CPU+FPGA 集成有意義嗎?

關於賽靈思的收購,還有一個話題可以討論:一些投資者或許有這樣的印象,AMD未來會推出類似超級APU的東西,除了CPU(也許還有GPU)也會集成FPGA。

那我們分別來討論下AMD 主要服務的兩個市場。首先,在 PC 市場上,AMD 推出 FPGA 的機會很小。正如我所説的,CPU(尤其是 英特爾 的)已經包含了許多加速器,而FPGA 似乎沒有價值主張。當然,AMD也許會進行嘗試,從而創造一個新的市場,但這種可能性很小,因為FPGA 只會增加 CPU 的成本。

其次,如上文所説的,FPGA 更有前景的市場是數據中心,但事實證明,這裏也不需要將 FPGA 集成到 CPU 中。

與數據中心未集成 GPU 以及 英偉達 僅基於 GPU 就積累了約 8000億美元市值的原因完全相同:GPU 或 FPGA 等加速器可以作為PCIe互連通過一個標準的鏈接被附加到CPU。

當然,有些人可能會爭辯説,集成或許會帶來一些好處,例如緩存一致性。然而,正是出於這個原因,業界即將採用一種稱為 CXL的新互連標準(由英特爾於 2019 年提出,並得到包括 AMD、賽靈思 和 Arm 在內的整個行業的支持)。

總而言之,收購 賽靈思 的主要理由不是硬件集成,而是(如 2020 年所述)AMD 試圖通過進入 FPGA 市場來擴展其 TAM。任何協同效應都將是在更高層次上,如提供 AMD CPU + 賽靈思 FPGA 作為英特爾 CPU + Altera FPGA 組合的競爭產品,以及軟件集成,例如英特爾如何通過一個API創建統一的編程模型。

FPGA 發展:之前發生了什麼

本節將總結過去幾年 FPGA 的主要市場趨勢。特別是英特爾的財務數據雖然沒有顯示,但實際上誰將在未來擁有 FPGA 領導地位,這已經有了明顯的演變。

總結 Altera-英特爾 的發展:

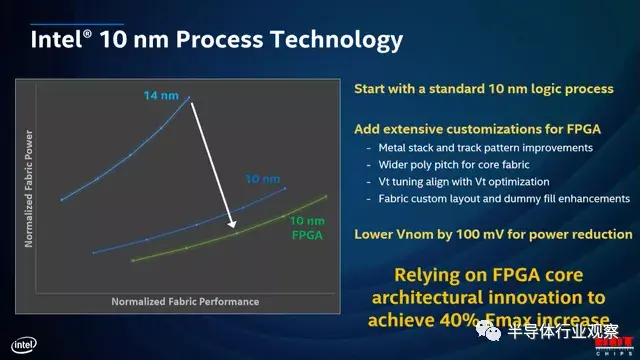

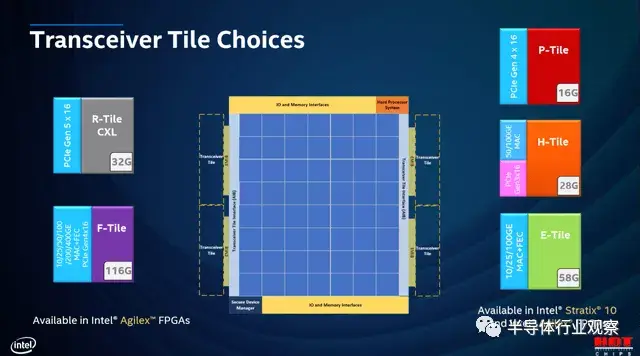

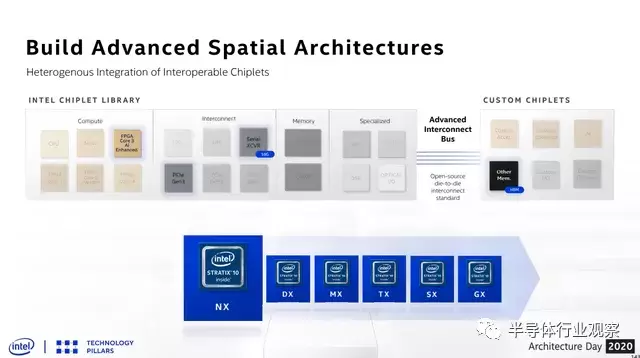

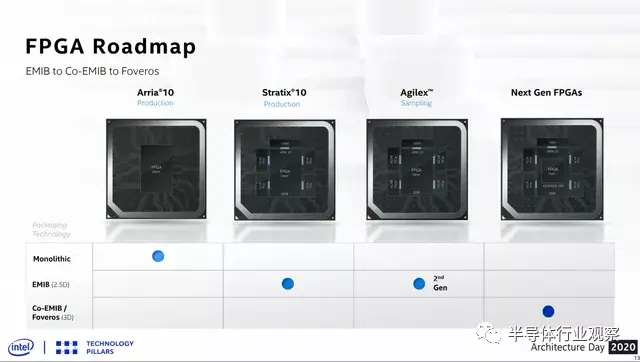

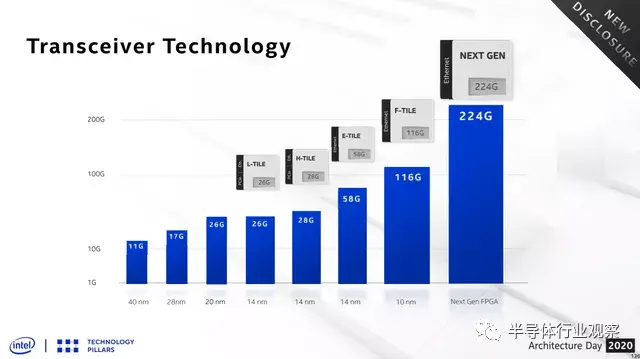

由於收購前的延遲,Altera 在轉向 14/16nm 節點方面比 賽靈思 晚了一年。然而,英特爾迅速採取行動並立即投資了一個並行開發團隊,在 14nm Stratix 10 開始出樣前,就開始研究10nm Agilex。因此,Agilex 和 Versal 大約在 2019 年年中同時開始採樣,這意味着英特爾在短短一代內就追平了工藝技術。Altera 一直是英特爾非常成功的代工廠客户,利用英特爾領先的工藝以及2.5D 和 3D 小芯片封裝技術,形成了豐富的小芯片生態系統。值得注意的是,這甚至早於AMD 將其第一個 MCP(多芯片封裝)(“Naples”,2017 年)推向市場,更不用説 AMD 的第一個半芯片設計(“Rome”,2019 年)。因此,與 AMD 粉絲經常所説的相反,業界第一個採用小芯片的實際上是 Altera。此後,Stratix 10 和 Agilex 成為越來越大的第一方和第三方小芯片生態系統的一部分。實際上,這仍然是業界唯一真正的跨供應商和跨代工廠的小芯片生態系統。我稱 AMD 的方法為半芯片,因為它仍然基於傳統的 MCP 方法。收購讓英特爾實現了什麼:儘管收購前有延遲,英特爾仍然能夠提供業界首款具有 集成 HBM、58G 收發器和PCIe 4.0 的 16/14nm FPGA。英特爾還在 2019 年收購了 eASIC,從而創建了 eASICs。它們提供了介於 ASICs 和 FPGAs 之間的功能集(在成本、上市時間、功耗、性能等方面)。這些 eASICs 也可以作為小芯片添加到 Agilex FPGA 中。英特爾還於 2019 年創建了網絡和自定義邏輯,以實現上述網絡協同效應。雖然由於FPGA在網絡領域的銷售額下降,英特爾的收入實際上有所下降,但英特爾表示,這些銷售額已從英特爾FPGA轉移到英特爾ASIC。最近,英特爾表示,由於供應短缺,無法完成所有訂單:“由於嚴重的供應限制,DSG 收入為 4.86 億美元,同比下降 3%。但FPGA市場繼續仍然供不應求。”英特爾 FPGA 也是英特爾異構 XPU 戰略的關鍵部分,它在軟件方面轉化為對英特爾 oneAPI 計劃的支持。英特爾 FPGA 與AI無處不在的戰略保持一致,幾年前英特爾還推出了帶有 Tensor Blocks 的 14nm Stratix 10 NX。在某些工作負載中,FPGA 的效率可能比 GPU 高一個數量級。

在賽靈思方面:

賽靈思 將其 Versal 產品稱為 APACs(自適應計算加速平台),而不是 FPGA,為的是強調它包含了更多的IP和加速器(例如用於5G和AI),從而擴展並增強了傳統 FPGA以外的用途。這些APACs可以被視為英特爾通過小芯片為其 FPGA 增加更多功能的方法的單片等效:賽靈思的 7nm Versal 路線圖由不少於 6 個產品線(單片芯片)組成。賽靈思 的 oneAPI 相當於其 Vitis 軟件,顯然這仍是一個僅限 FPGA 的解決方案,而 oneAPI 則針對英特爾的完整芯片產品組合。

總的來説,Altera(英特爾)和 賽靈思(AMD)都採用了一種策略,即通過包含專用加速引擎來擴展 FPGA 的用途,但兩家公司採用的是不同方式:Altera已經能夠採用英特爾行業領先的先進封裝來創建小芯片生態系統,允許根據客户的要求對每個單獨的FPGA進行定製,而賽靈思則仍然遵循傳統的單片芯片方法。

Altera 的小芯片方法取得了成功,因為它率先將 58G/112G 收發器、Arm 內核和 HBM 集成到 FPGA 中。小芯片的好處是一旦創建,就可以添加到 FPGA 中,而無需重新流片,從而大大縮短上市時間。

最後,由於 Versal 和 Agilex FPGA 基本上是在同一時間推出的,應該可以看到 英特爾 的投資讓 Altera 在這方面迎頭趕上。

FPGA的對決繼續

由於兩家公司的路線圖都非常明確,所以可以進行比較。英特爾和賽靈思同時向 10nm/7nm 邁進。

如前面所説的,在 10nm/7nm這一代,兩家公司都採取了一種有些相似但又有所不同的方法,儘管兩家公司都在多個 SKU擴充產品線,但賽靈思似乎正在通過廣泛的Versal acap,對其瞄準的幾個領域(如邊緣、5G和機器學習)採取更具體的方法。為此,賽靈思更加專注於圍繞 FPGA 平台集成多個加速器,因此得名 ACAP。請注意,這些都是單片芯片。

視頻 IP 性能提高 50%;每瓦性能提高 2 倍(結構);(結構)性能提高 30%。

第二個主要區別是英特爾繼續其小芯片戰略:與基礎10nm FPGA 相同,但可以附加小芯片生態系統來定製 FPGA。這種方法在開發成本、特性集和上市時間方面具有實質性優勢。例如,上面提到的116G 收發器、PCIe 5.0/CXL 和 HBM等一些功能,只有未來在這些技術可用時才能出現。

這實質上表明瞭除了性能之外,英特爾在連接性和 I/O 支持方面進一步獲勝,因為 Versal 沒有 116G 收發器、DDR5、PCIe 5.0 或 CXL 1.1 支持。

這也説明,原則上沒有什麼可以阻止客户為 賽靈思 Versal ACAP 中的加速器添加小芯片,這確實是英特爾通過從ASIC到 eASIC 再到 FPGA 的自定義邏輯連續體的戰略。例如,隨着 2020 年 5G ASIC 的興起,英特爾的數據中心鄰接收入開始顯著增加(增加了數億美元),“交付英特爾領先的 5G ASIC,產生可觀的年收入增量”。這意味着真正潛在財務狀況可能比僅比較英特爾 FPGA 與賽靈思更微妙,因為英特爾 ASIC 的收入未知。

從英特爾看FPGA的創新

除了在 FPGA 功率和性能方面處表現優越之外,英特爾還有一些創新正在進行中,這可能會進一步鞏固其實力:

Stratix 10 NX:業界首款針對 AI 優化的 FPGA,性能提升 15 倍。PCIe 6.0 和 CXL 2.0將在以後階段(通過新的小芯片)出現在 Agilex 上。業界首款224G 收發器,針對下一代(英特爾 4)FPGA。英特爾 4 FPGA:使用 EMIB 和 Foveros 3D 封裝(以 Foveros 為特色),可能會讓效率和密度提高一個數量級以上。

尤其是下一代 FPGA 清楚地表明,英特爾除了進一步擴展其 FPGA 領先地位外,還可以做任何事情,因為其3D堆疊的使用將是賽靈思無法比擬。

Stratix 10 NX

我在2020年6月發佈時與 Cooper Lake Xeon Scalable 一起討論了 Stratix 10 NX)。它是英特爾首款針對 AI 優化的 FPGA,具有 AI Tensor Blocks:將傳統的 DSP 單元換成 AI Tensor Blocks,而AI Tensor Blocks 擁有 15 倍多(支持 INT8 的)計算單元,相應的性能提升了 15 倍,這使它們能夠與 英偉達 GPU 競爭:

針對 英偉達的產品 ,英特爾表示,其 Stratix 10 NX 設備在 BERT 批處理中比 英偉達 V100 GPU 快 2.3 倍,在 LSTM 批處理中快 9.5 倍,在 ResNet50 批處理中快 3.8 倍。

另一篇論文描述了與 英偉達 的 V100 相比,Stratix 10如何在現實世界最先進的文本轉語音工作負載上實現 8 倍的性能和 10 倍的每瓦性能。考慮到這些數據,這使得它能與 英偉達 的 7nm Ampere 競爭。(之所以沒有與最新的A100進行比較,是因為當時這些工作負載還不適用於A100或者還未針對A100進行優化)。

以下幻燈片顯示了它如何利用其小芯片方法從小芯片庫“構建”Stratix 10 NX。

FPGA 的其餘部分類似於 Stratix 10 MX:

互連小芯片採用 58G 收發器 (SerDes) 技術和 PCIe 3.0。沒有內存或“專用”小芯片。對於其他“自定義小芯片”,支持 HBM(通過英特爾的開源 AIB 協議)。

通過這種方法,NX是第六個Stratix 10版本(每個版本都有多個SKU,以進一步區分性能和功能)。如果沒有小芯片,這種擴展是不可能的:例如,Stratix 10 DX引入了PCIe 4.0和UPI支持。

總體而言,這種設計方法降低了成本(因為驗證是在小芯片級別進行的)和加快了上市時間(因為每個新變體都可以在組成小芯片後立即上市)。

PCIe 6.0 和 CXL 2.0

通用 PCIe 互連已經在加速路線圖上。經過多年的 PCIe 3.0,行業在 2019 年左右轉向 PCIe 4.0,並在 2021 年轉向 PCIe 5.0。Agilex 也支持 CXL,因為它基於 PCIe 5.0。PCIe 6.0(大約 2023/2024 年)將進一步跟上這種類似摩爾定律的節奏。

英特爾的 Agilex 路線圖顯示,未來這些 FPGA 將支持 PCIe 6.0 和下一代 CXL 2.0,這也將為超 400G 以太網帶來支持。

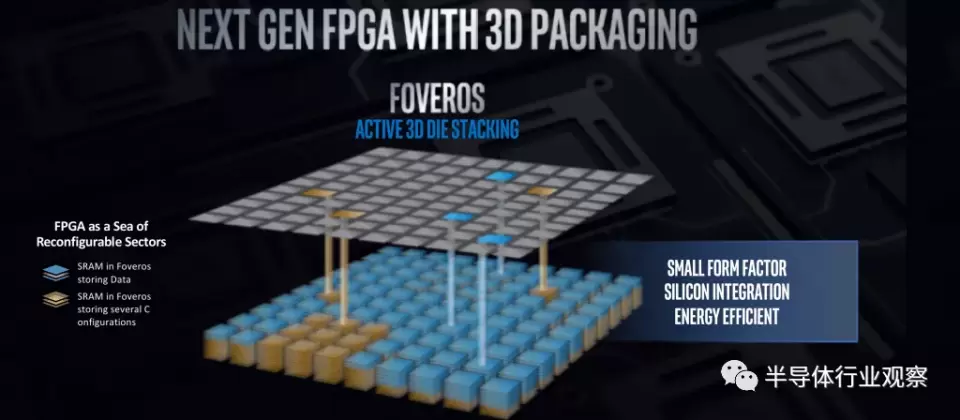

然而,上面的 2020 年幻燈片並未表明 FPGA 轉向 3D 封裝的重要性。相比之下,在之前 2018 架構日,英特爾曾暗示它可以使用 Foveros 堆疊不僅僅是兩層(就像在 Lakefield 和 Ponte Vecchio 中所做的那樣),這將把FPGA 轉變為“可配置扇區的海洋”。英特爾表示,這將帶來高達 1-2 個數量級的能效提升。換句話説,這可能是 FPGA 的範式轉變。

展望未來,英特爾還計劃將 Foveros 用於 FPGA。英特爾的下一代 FPGA 將大量使用芯片堆疊,預計 Foveros 能在性能、能源效率或密度壓縮方面實現 1 甚至 2 個數量級的提升,而這種提升來自一種完全不同的 FPGA 配置方式。為了滿足當今的高端 FPGA,業界使用高帶寬存儲器,該存儲器通過導線連接到所有可配置模塊。英特爾可編程解決方案工程集團副總裁兼總經理Ravi Kuppuswamy表示:“有了Foveros和3D堆疊,突然之間,您就擁有了大量可重新配置的內核。”主要的簡化來自於它們將傳統的長電線轉換為短垂直電線的能力。

最後,SerDes(收發器)可能是一個鮮為人知的技術組件,但它卻是 FPGA一個非常重要的部分,因為 FPGA 有多種用途,從存儲到移動再到處理數據,這正是 SerDes 在互連方面發揮作用的地方。

它可以與 PCIe 互連進行比較,因為兩者具有相似的每通道吞吐量。為了不斷提升互連速度,該領域正在使用先進的技術,同樣,擴展SerDes也有其自身的挑戰。

英特爾 以 58G FPGA 擊敗 賽靈思 推向市場,開始為 Agilex 提供 116G FPGA,並且在 2020 年 8 月,英特爾 是第一家宣佈在實驗室中運行的 224G PAM-4(每個信號兩位)收發器 IP的公司(似乎在 英特爾 4 上)。

英特爾在 2017 年推出了 Stratix 10 FPGA,雖然比賽靈思晚了一年,但 Versal 和 Agilex 大約在 2019 年年中同時開始提供樣品。Agilex 還展示了優異的領導能力和效率。需要注意的是,鑑於FPGA客户設計週期較長,FPGA 的出貨量通常需要 3-4 年才能達到峯值。展望未來,鑑於英特爾提到的“1-2 個數量級”的改進,英特爾正在開發可能是革命性的FPGA。

英特爾的 FPGA 引人注目,因為它們是其最新封裝和小芯片技術的運載工具,從而產生了廣泛的小芯片庫。最值得注意的是,英特爾在收發器方面的持續領先地位 (58G-116G-224G) 強化了這一觀點。最後,FPGA 在英特爾的 AI 戰略中也發揮着關鍵作用,英特爾的 oneAPI 軟件為此提供了支持。

雖然兩家公司的上市戰略有很大不同(英特爾:小芯片;賽靈思:ACAP),但通過使FPGA更容易獲得來擴大市場的目標對兩者來説是相似的。而這是一般是通過諸如OneAPI和Vitis等高級工具(而不是傳統的FPGA低級編程工具)實現的。

儘管 FPGA 的整體增長相當疲軟,但從Altera被收購以來的五年左右的時間裏,FPGA 最有前途的市場可以説仍然是數據中心,在那裏它們可以用作 IPU/DPU/SmartNIC 或作為 AI 或其他加速器工作負載(因為已經證明 FPGA 的性能遠遠優於 英偉達 GPU)。FPGA 不太可能像 GPU 那樣成為主流,但如果這些較新的編程範例至少取得一些成功(例如通過OneAPI),那麼對於英特爾和賽靈思而言,那麼這可能會極大地增加其可尋的目標市場。