後FinFET時代,它們將擔當重任_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2021-12-15 10:27

來源:內容由半導體行業觀察(ID:icbank)編譯自IBM,謝謝。早在 1965 年,計算機科學家戈登·摩爾 (Gordon Moore) 就提出假設,芯片中集成的晶體管和其他組件的數量將大約每兩年翻一番,與此同時,計算機的速度和容量也將翻一番。但在 55 年後,在單個芯片中能塞進去的晶體管數量幾乎達到了極限。

然而,計算系統的前路並沒有放緩。動態 AI 系統已準備好為我們生活的方方面面——從道路安全到藥物發現和先進製造——提供動力,這在未來將需要更強大的芯片。為了讓芯片產業繼續以摩爾假設的速度和計算能力前進,我們需要製造具有多達 1000 億個晶體管的芯片。

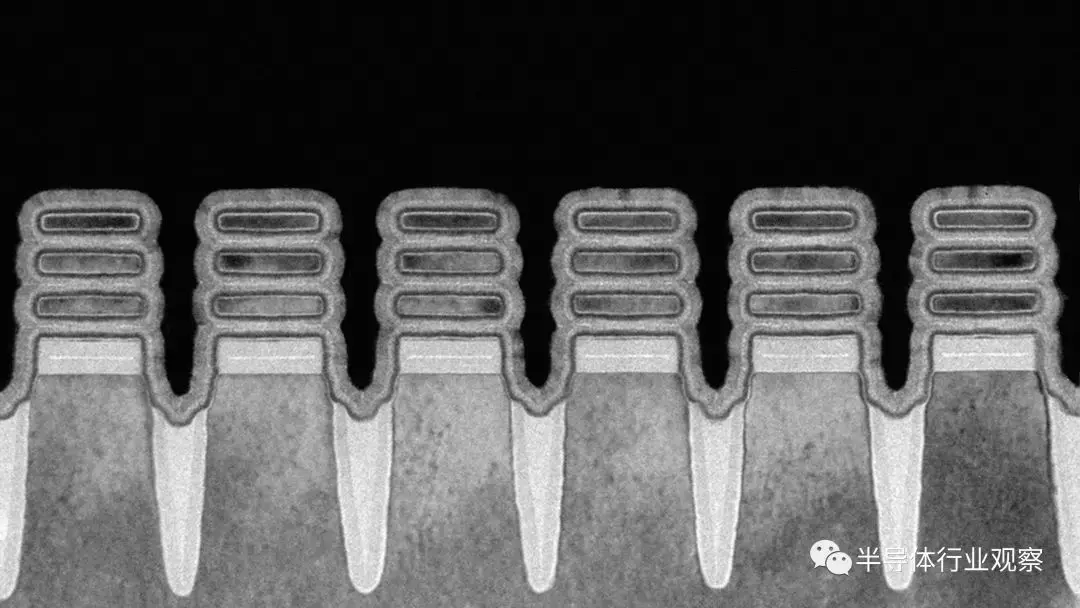

為了實現這個目標,行業內的廠商都在探索多樣的方案。IBM Research 也深度參與其中,日前他們宣佈,公司與三星在半導體設計方面的合作取得了突破。藉助一種稱為垂直傳輸納米片場效應晶體管 (Vertical-Transport Nanosheet Field Effect Transistor:VTFET),可以讓摩爾定律在未來幾年持續有效。

VTFET(垂直傳輸納米片場效應晶體管)晶圓

VTFET:讓1nm成為可能

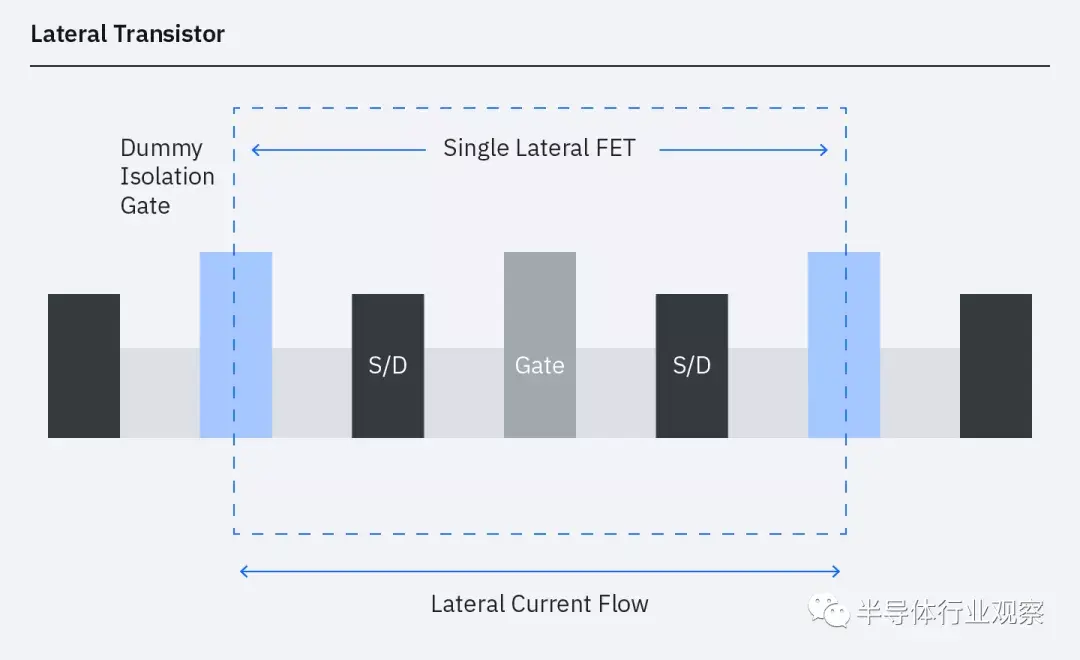

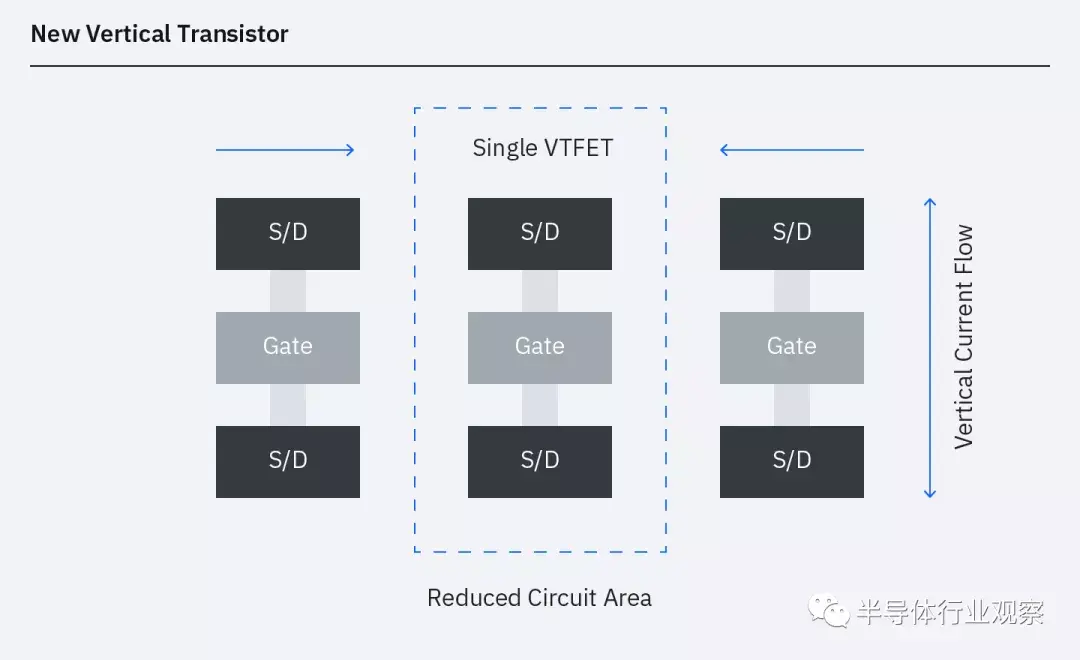

據IBMji介紹,當今的主要芯片架構是橫向傳輸場效應晶體管 (FET),例如鰭式場效應晶體管或 FinFET(因硅體類似於魚的背鰭而得名),它沿硅片表面將晶體管分層。VTFET 則是將晶體管垂直於硅警員,並引導電流垂直於硅片表面。這種新方法通過打破對晶體管柵極長度、間隔厚度(spacer thickness)和觸點尺寸的物理限制來解決縮放障礙,以便優化包括性能和功耗在內的各種參數。

通過 VTFET,IBM成功地證明了在 CMOS 半導體設計中探索超越納米片技術的縮放是可能的。在這些先進的節點上,與按比例縮放的 FinFET 替代方案相比,VTFET 可帶來兩倍的性能提升或高達 85% 的功耗節約。1

新的 VTFET 架構展示了一種在納米片之外延續摩爾定律的方法。在今年5 月,谷歌宣佈了一種 2 納米節點芯片設計,該設計將使芯片能夠在指甲大小的空間中安裝多達 500 億個晶體管。而VTFET 繼續創新之旅,打開通往新可能性的大門。

過去,設計人員通過縮小柵極間距和佈線間距,以將更多晶體管封裝到芯片上。這適合所有組件的物理空間被稱為接觸式柵極間距 (Contacted Gate Pitch :CGP)。縮小柵極和佈線間距的能力使集成電路設計人員能夠在我們的設備中將晶體管從數千個增加到數百萬個,再到數十億個。但是,對於最先進的 FinFET 技術,間隔(space)、柵極和觸點的空間有限。那就意味着一旦達到了CGP極限,你就沒有空間繼續微縮了。

通過垂直定向電流,柵極、間隔和觸點不再受傳統方式的限制:我們有空間擴展 CGP,同時保持健康的晶體管、觸點和隔離(隔離和淺溝槽隔離,STI:spacer and shallow trench isolation)尺寸。擺脱了橫向佈局和電流流動的限制,我們能夠使用更大的源/漏觸點來增加器件上的電流。可以選擇柵極長度來優化器件驅動電流和泄漏,而隔離層厚度可以獨立優化以降低電容。我們不再被迫在柵極、spacer和觸點尺寸之間進行權衡,這可以提高開關速度並降低功耗。

另一個關鍵的 VTFET 特性是能夠將 STI 用於相鄰電路隔離,以實現零擴散中斷 (ZDB:Zero-Diffusion Break) 隔離,而不會損失有源柵極間距。相比之下,橫向傳輸 FET 電路的密度受到電路隔離所需的雙或單擴散中斷的影響,這會影響進一步縮小技術的能力。

在十年前,我們可以看到橫向架構會在激進的柵極間距下達到縮放限制:實際上,每個器件組件都接近縮放限制。我們想找到可以打破這些障礙的其他途徑,我們的動機從未改變。我們的目標一直是為未來的技術生產具有競爭力的設備。

由於柵極間距比生產中已知的任何產品都更具侵略性,並且體硅片上柵極間距低於 45 nm 的 CMOS 邏輯晶體管,我們相信 VTFET 設計代表着構建下一代晶體管的巨大飛躍,這在未來幾年內將使更小、更強大和更節能的設備成為可能。

GAA:2nm的晶體管選擇

正如前文所説,IBM在今年五月已經公佈了公司實現2nm的方式,讓我們再深入回顧一下IBM的實現方法。

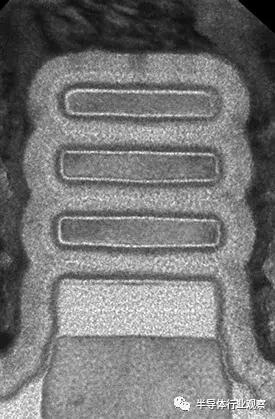

據IBM介紹,他們推出的新型環柵 (Gate-All-Around:GAA) 納米片器件架構使其能夠在大約指甲大小的空間中集成 500 億個晶體管。這讓他們為 2 納米 (nm) 節點的實現鋪平了道路。

不過IBM也強調,他們對 2 納米芯片節點的納米片晶體管的演示也是對幾個較小裏里程碑式的驗證,這些里程碑向我們證明這種方案是可行的,以及 IBM 跨學科專家團隊在材料、光刻、集成、項目中的設備、表徵和建模方面的合作是相得益彰的。

IBM進一步指出,自他們在2012 年夏天首次提出用“Nanosheet”這個名字來描述其當時正在研究的新設備架構後,公司一貫的想法就是開發一種片狀結構,而不是我們一直使用的納米線結構。在他們看來,這個新命名的納米片架構將能夠提供納米線所不具備的靜電優勢,同時還具備提高性能所需的密度。IBM強調,只有通過這些特性的組合,IBM Research 才能提供優於FinFET 的晶體管架構。

IBM還講到,公司納米片晶體管架構的第二次迭代涉及一種新型的水平堆疊 GAA 芯片設計。晶體管上的四個“gate”使優秀的電信號能夠通過芯片上的其他晶體管並在它們之間傳遞。

IBM進一步強調,公司2nm的另一個里程碑是2017 年。因為在當年他們正式推出了納米片晶體管,同時他們也意識到晶體管架構中的內部間隔模塊(inner spacer module )將成為納米片性能的關鍵推動因素,而這可以通過降低柵極到源極/漏極的電容來實現。IBM表示,Inner spacers是關鍵的結構元件,因為它們定義了 GAA 器件的有效柵極長度。2019 年,該團隊與合作伙伴公司合作,使用幹壓痕技術(dry indent technique)開發了一種新的inner spacer工藝。這允許實現低於 1 nm 的工藝控制以及改進的inner spacer profile。

通過將這種新的乾式內部(dry inner spacer)隔離工藝與業界首個底部電介質隔離( bottom dielectric isolation)相結合,IBM能夠創建一個 12 納米的柵極長度,它只有兩打原子長。全底電介質隔離(full bottom dielectric isolation)方案的好處是它可以減少子通道泄漏(sub-channel leakage),提供對工藝變化的免疫力(immunity),並提供功率性能改進。

值得注意的是,晶體管尺寸的最新進展——例如 10 nm、7 nm、5 nm 和現在的 2 nm 節點——指的是使用特定類型的半導體制造工藝製造的特定一代芯片,很像 5G指最新的無線標準。在這種情況下,例如,2 nm 並不對應於傳統定義的接觸金屬線的一半間距。一般來説,較小的技術節點會產生較小的晶體管,其中更多的晶體管可以封裝到芯片上,使其更快、更節能。

在今年五月,IBM 研究人員還首次使用極紫外 (EUV) 光刻圖案化技術在前端 (FEOL) 處開發出寬度為 15 至 70 nm 的納米片器件,這證明該技術可產生比可見光更小的線條。FEOL 是集成電路製造的第一部分,其中晶體管和其他組件在半導體中形成圖案。IBM表示,公司是第一個討論將 EUV 引入 FEOL 的研究機構。IBM Research 的奧爾巴尼實驗室擁有業內最先進的 EUV 光刻工具之一。能更精確地控制納米片寬度,並極大地簡化了將低功耗和高性能設計放在同一芯片上的過程。

據IBMjIE橫掃,公司第一款 2 nm 晶體管中另一個值得強調的關鍵進步是我們開發了一種新的多閾值電壓 (Multi-Vt) 器件,其泄漏水平跨越三個數量級。這使設備製造商能夠更好地選擇底層芯片架構所需的性能水平。

IBM表示,較之使用7 納米處理器技術的手機(如 iPhone 11、三星 Galaxy S10 和谷歌 Pixel 5),使用2 納米處理器的手機可以將電池壽命提高四倍。基於平均使用情況,這意味着手機只能需要每四天充電一次。

使用相同的功率,擴展到 2 nm 芯片節點晶體管相當於比今天的 7 nm 芯片提高大約 45% 的性能。在相同的性能水平下,這大約可以節省 75% 的電量。這種功率/性能組合對於加速通過混合雲環境交付的高級認知、邊緣和其他計算平台以及為與量子計算機一起運行而構建的加密加速器的開發和交付至關重要。

IBM Research 在當時表示,公司將繼續探索繼續擴展到 1 nm (開頭提到的VTFET)及更先進工藝的方法。突破這些障礙對於使 IBM 能夠繼續提供企業採用最新、最先進的人工智能和混合雲技術所依賴的硬件至關重要。

在IBM看來,儘管我們距離製造 2 nm 節點芯片還有幾年的時間,但 IBM Research 的創新直接融入了我們的商業產品路線圖。例如,業界首款商用 7 nm 處理器是基於 IBM Research 在2015 年的突破。

展望未來,IBM希望能憑藉其在半導體創新方面的領先地位,讓雲提供商或其他大型數據中心運營商可以使用更少的服務器來完成相同數量的工作,進而降低能源成本和碳足跡。