先進封裝,越來越模糊_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2022-11-02 18:07

**編者按:**在semianalysis之前的文章《先進封裝最強科普》、《巨頭們的先進封裝技術解讀》以及《巨頭們發力先進封裝》等文章裏,作者對先進封裝的現狀和未來進行了深入的解讀。在本文中,作者將深入探討 2.1D、2.3D 和 2.5D 高級封裝的模糊界限。他表示,在 IMAPS 2022 上,展示了該領域的許多進步,先進封裝行業的未來充滿活力。

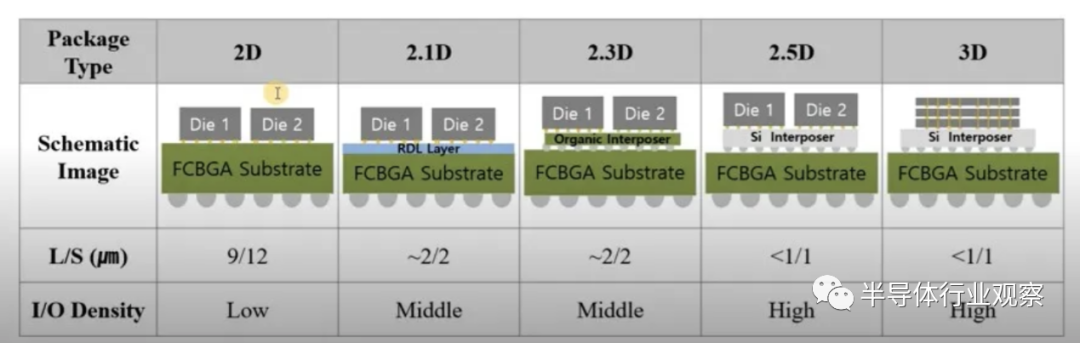

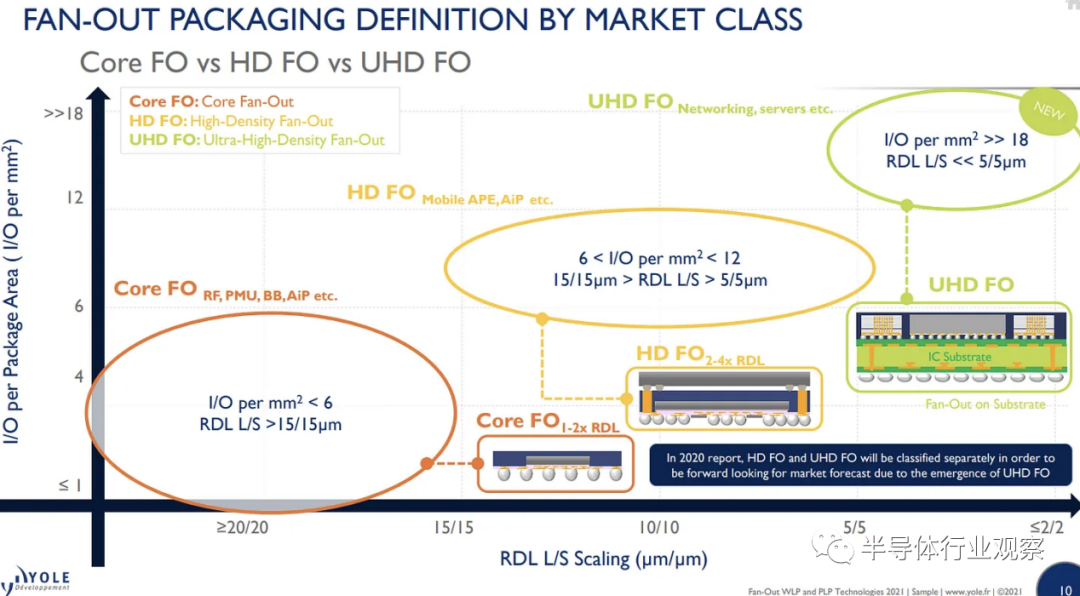

如他所説,目前有四個主要的高級封裝:

3D——堆疊在有源硅上的有源硅——最著名的是利用 TSMC 的 SoIC CoW 的 AMD 3D V-Cache和利用 TSMC 的 SoIC WoW 的 Graphcore 的 IPU BOW 。

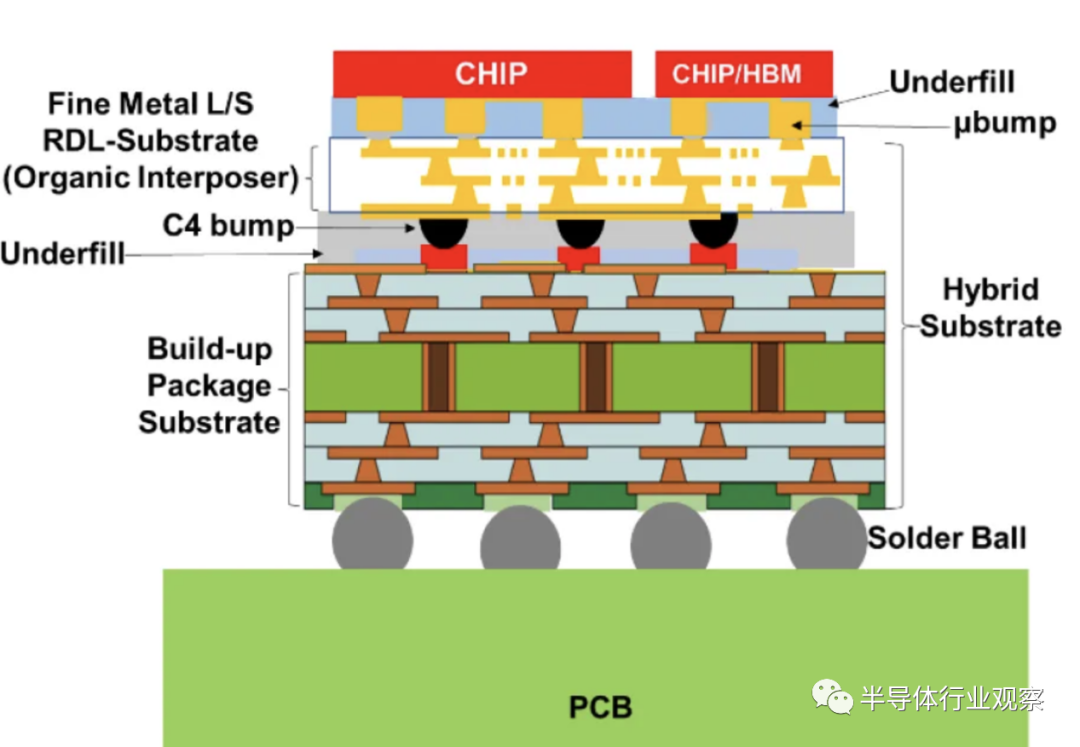

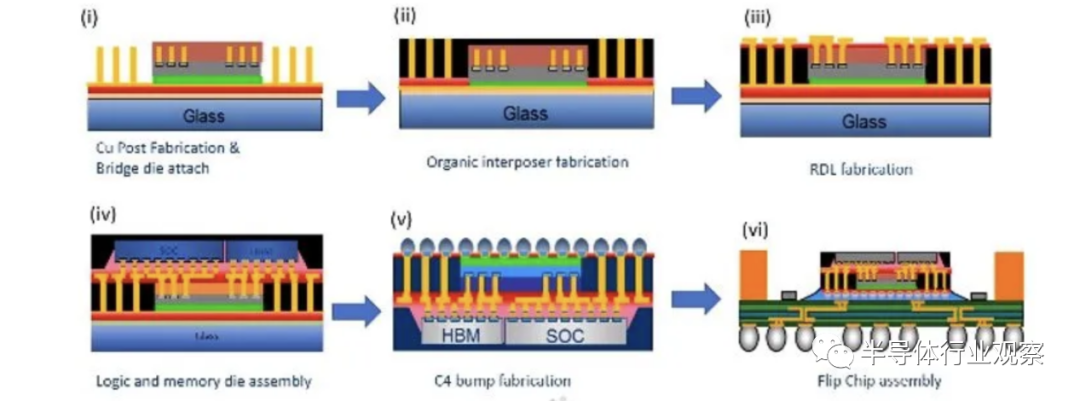

2.5D ——堆疊在無源硅上的有源硅——最著名的是採用 TSMC 的 CoWoS-S 的帶有 HBM 內存的 Nvidia AI GPU和採用英特爾 Foveros 的英特爾 Meteor Lake CPU 。

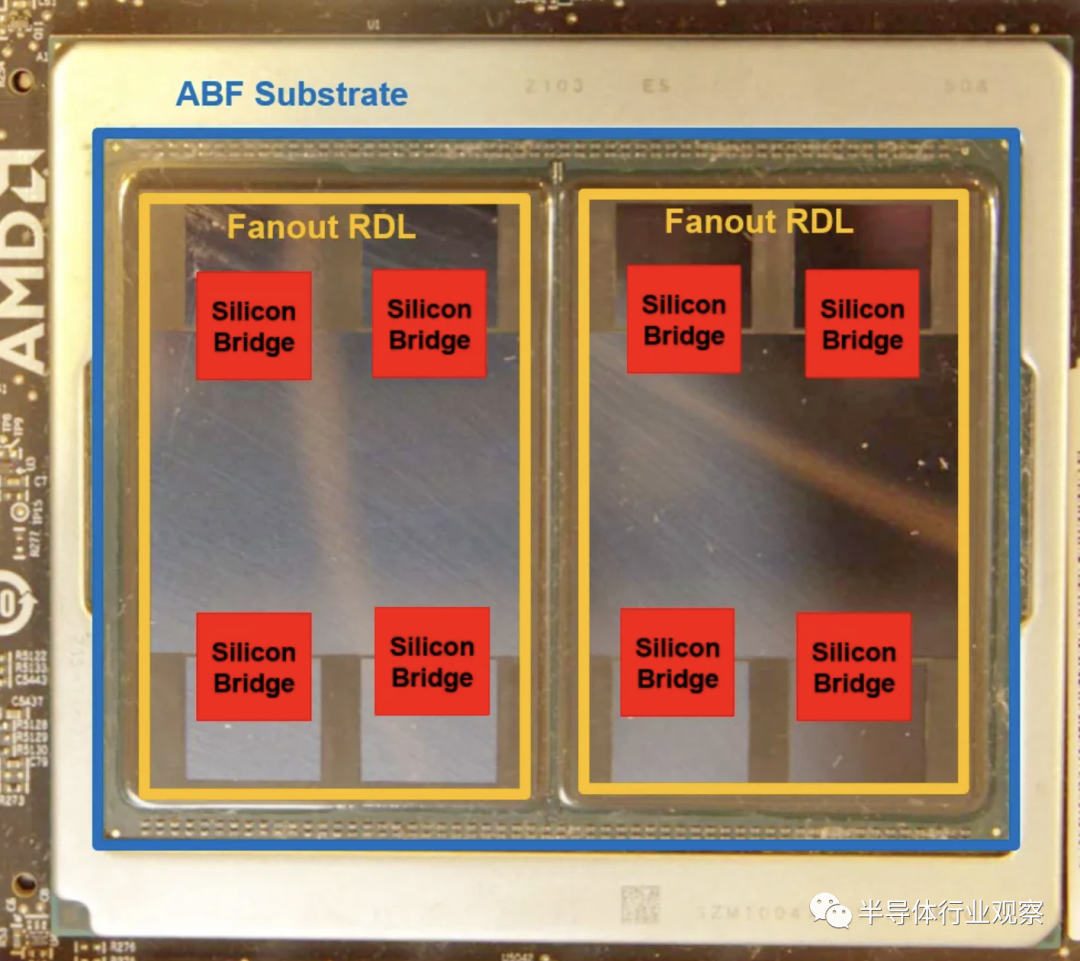

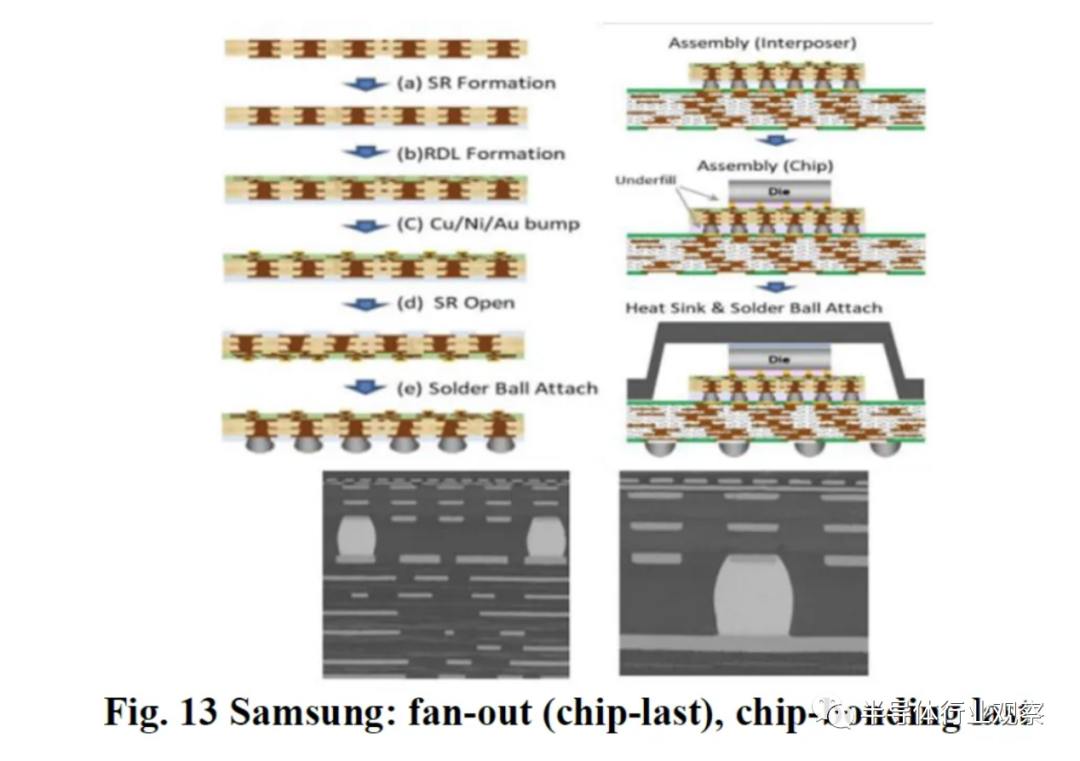

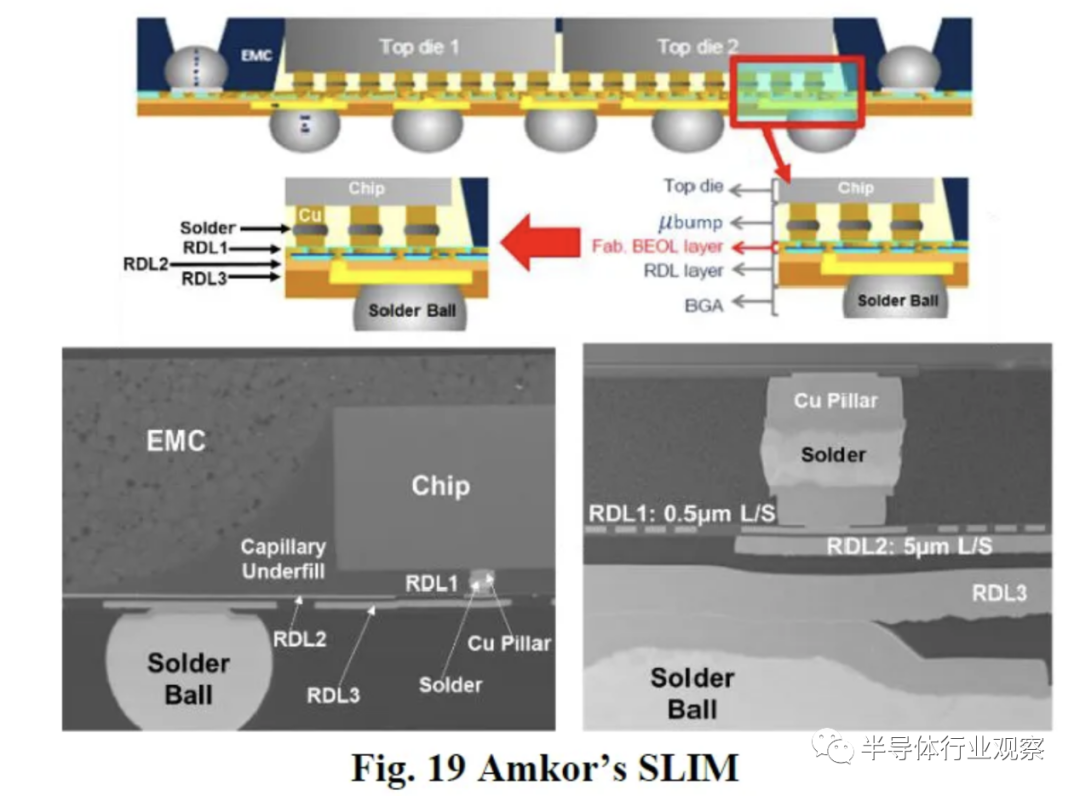

Fanout RDL(帶有環氧模塑料的層壓板)——最著名的是用於 Apple 的 A 系列、S 系列和 M 系列芯片的台積電 InFO 、ASE FoCoS 和 Amkor WLFO。

build-up ABF 基板(銅芯包覆味之素增層膜層和 RDL 層)——最著名的形式是Intel 和 AMD PC 和 Datacenter 芯片。

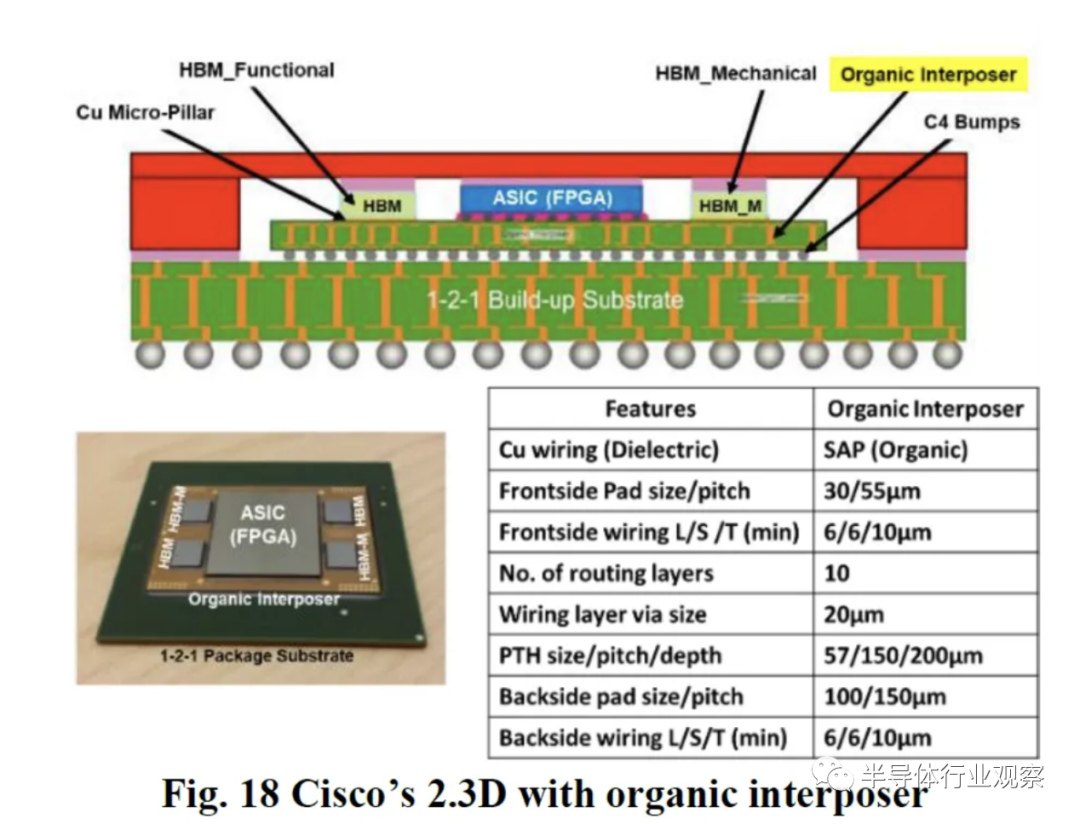

高級封裝的另一個歧義來源是工程師經常使用有機基板這個詞。ABF 和核心扇出都包含有機環氧樹脂化學物質。

雖然由於最大限度地減少了昂貴的硅中介層的使用,這種方法的成本在理論上較低,但與傳統的 2.5D 硅中介層相比,成品率損失的可能性更高。

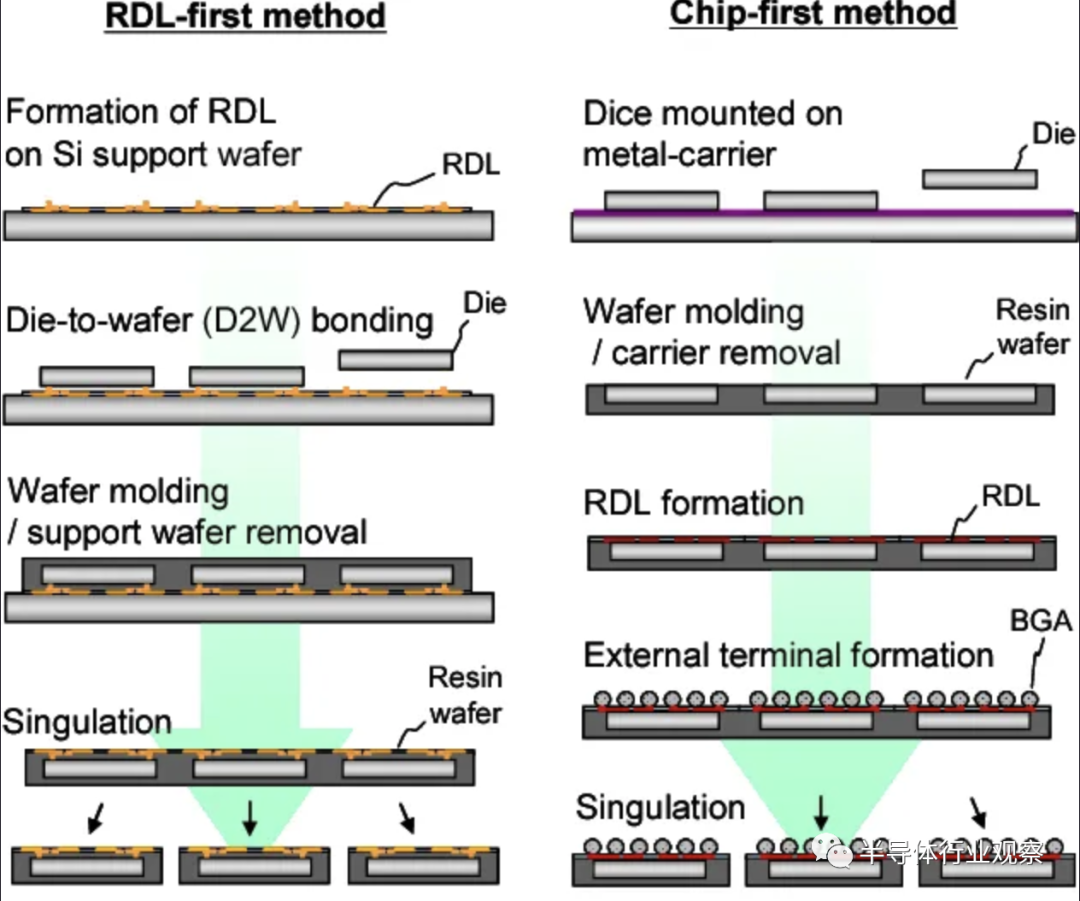

Fanout RDL 不是一個單一的進程。它可以用幾種不同的材料類型建造。此外,它可以是 RDL 優先或芯片優先流程。

傳統上,數據中心和 PC 行業的供應鏈將已知良好的基板與已知良好的芯片相匹配。RDL-First/Chip Last,Chip Bonding Last 是首選的封裝方法,如果它可以經濟高效地完成的話。

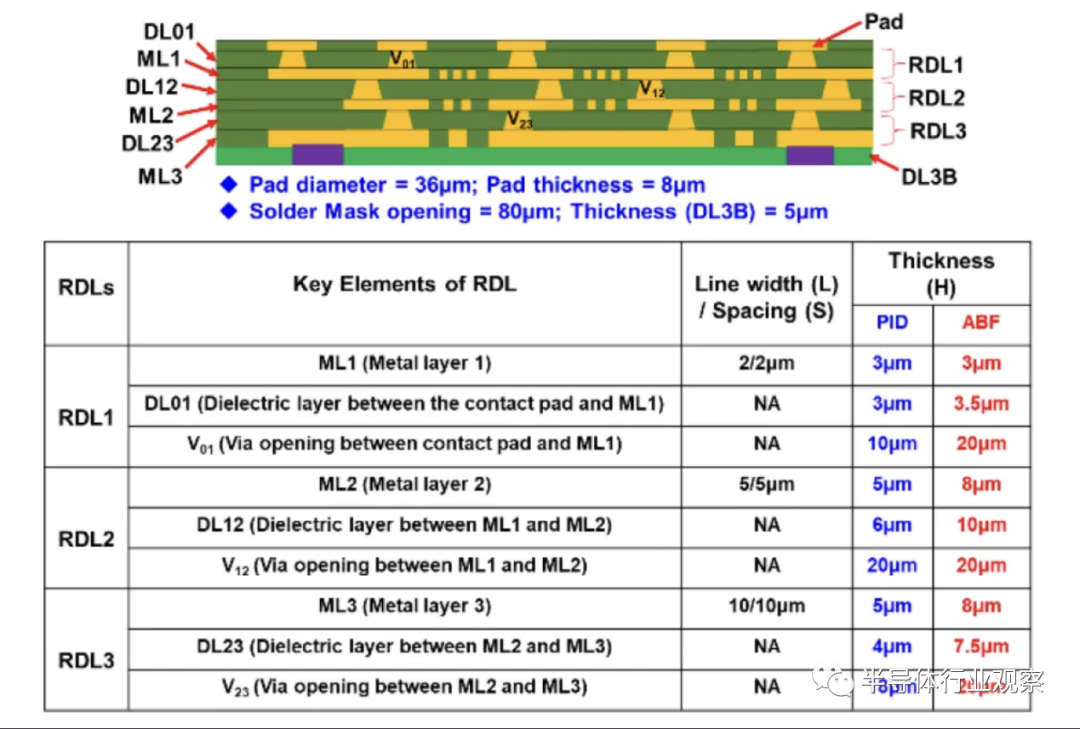

與扇出(chip-first 或 RDL-first)工藝相比,採用扇出(chip-first)工藝的 IC 集成更簡單,成本更低。問題是芯片優先意味着更多已知的好芯片將失去封裝良率。隨着行業轉向更昂貴的工藝技術,這種封裝良率損失繼續主導着封裝工藝成本的大部分增長。此外,扇出(chip-last)集成還有其他優勢,例如更大的芯片尺寸、更大的封裝尺寸、更少的芯片移位問題以及用於 RDL 的更精細的金屬 L/S。L/S是線間距,指的是金屬互連的寬度和它們之間的空間。

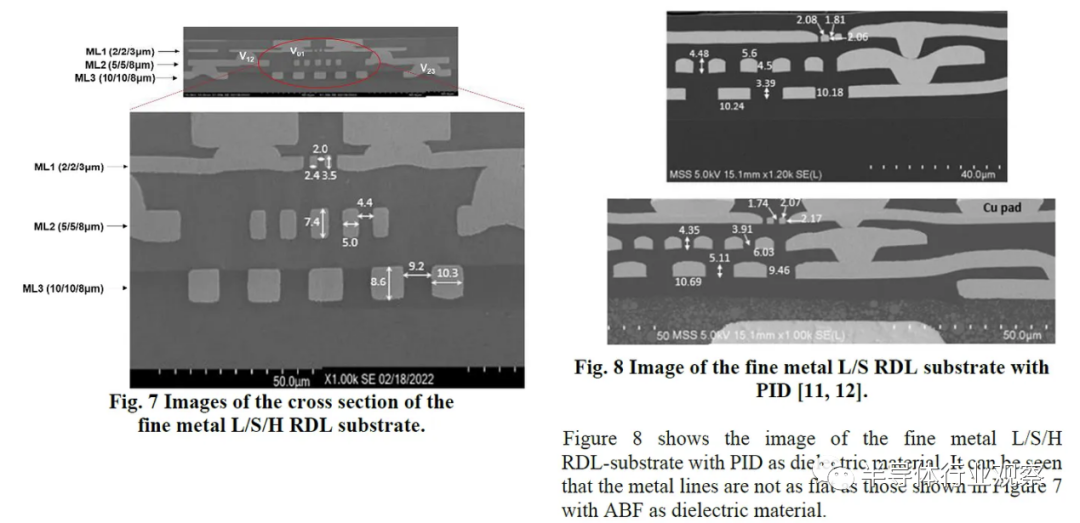

隨着 build-up ABF 基板的改進,核心扇出和 HD 扇出市場在移動應用之外受到一定程度的蠶食。關於電介質材料,光成像電介質 (PID) 目前能夠達到更精細的間距。儘管如此,如 Unimicron 所示,ABF 在表面變化方面具有許多優勢。

在追L/S的時候,Amkor SLIM和ASE SPIL NTI可以做到0.4微米和0.5微米。兩者都僅限於第一層上的這些細間距。

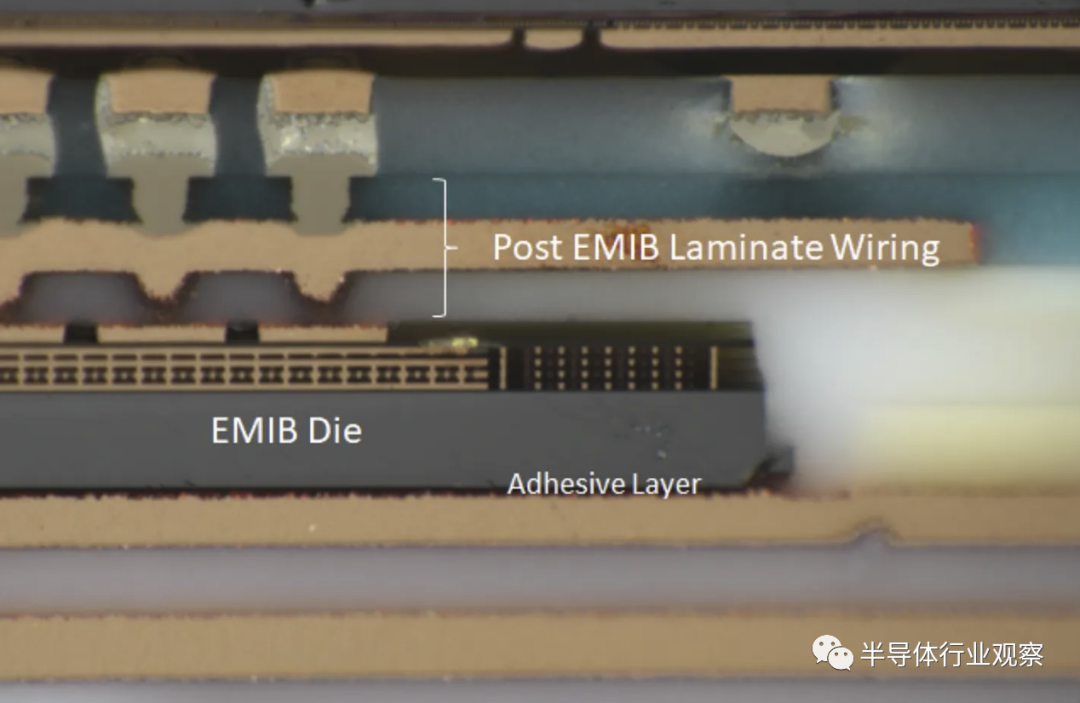

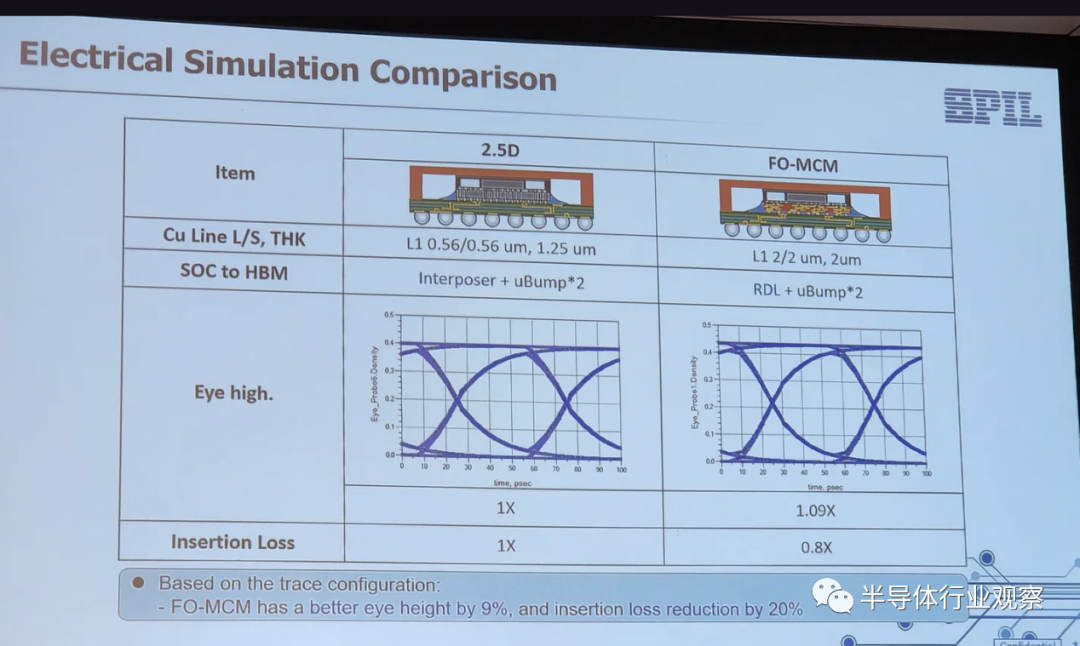

隨着 RDL 扇出進入以前僅由 2.5D 中介層佔用的應用,成本和產量也是必不可少的因素。帶有硅橋的扇出工藝開始興起,但不使用硅橋將 ASIC 與 HBM 集成的新工藝也越來越接近生產。扇出和 ABF 基板的這些進步正在迅速模糊高級封裝之間的界限。

在評估 2.1D 到 2.5D 領域的高級 IC 封裝時,需要考慮多個變量。焊盤間距、L/S 和層數是必不可少的因素,但可靠性、翹曲問題、封裝成本、產量和封裝尺寸也在考慮之中。

未來,在標準 build-up ABF 基板上封裝無芯 ABF 基板的混合基板可能是某些用例的最佳選擇。在其他情況下,封裝在標準 build-up ABF 基板之上的芯片優先扇出 RDL 可能是另一個用例的最佳選擇。隨着裸片數量和類型的異構集成多樣性,評估與封裝有關的權衡變得更具挑戰性。

來源:內容由半導體行業觀察(ID:icbank)綜合自semianalysis,謝謝。