NIL光刻的現在和未來_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。2022-11-15 18:45

1.介紹

壓印光刻技術是一種眾所周知的複製納米尺度特徵的有效技術。納米壓印光刻(NIL)製造設備採用了一種模版技術,該技術涉及通過噴射技術在基底上沉積的低粘度抗蝕劑的逐場沉積和曝光。將有圖案的掩模放入液體中,然後液體通過毛細作用(capillary action)迅速流入掩模中的浮雕圖案。在這一填充步驟之後,在紫外線輻射下交聯抗蝕劑,然後去除掩模,在基底上留下有圖案的抗蝕劑。與光刻設備所產生的圖案相比,該技術逼真地再現了更高的分辨率和更大的均勻性。此外,由於這種技術不需要寬直徑透鏡陣列和高級光刻設備所需的昂貴光源,NIL設備實現了更簡單、更緊湊的設計,允許多個單元聚集在一起以提高生產率。

先前的研究表明,空值分辨率優於10nm,使得該技術適用於用一個掩模打印幾代關鍵內存電平。此外,只有在必要的地方才使用電阻,從而消除材料浪費。考慮到在壓印系統中沒有複雜的光學器件,當結合簡單的單級加工和零浪費時,工具成本的降低導致了一個成本模型,對半導體存儲應用非常有吸引力。

任何要引入製造業的新光刻技術都必須具有性能優勢或成本優勢。關鍵技術屬性包括對齊、覆蓋和吞吐量。在以前的論文中,已經報道了測試晶圓的覆蓋和吞吐量結果。2018年,Hiura等人使用FPA-1200 NZ2C四站集羣工具報告了3.4 nm的混合匹配覆蓋層(MMO)和2.5nm的單機覆蓋層(SMO)。這些結果是通過將放大執行器系統與高階失真校正(HODC)系統相結合實現的,從而實現了高達K30的高階失真項校正。

在這篇綜述論文中,我們觸及了可以用零數據處理的市場,並描述了進一步提高零數據處理性能的努力。此外,我們還描述了最近開發用於解決邊緣放置錯誤的模式轉移過程的努力。

最後,我們將介紹佳能在發展可持續未來方面所做的努力,以及如何應用新方法來減少浪費,實現對環境友好的解決方案。

**2.**納米壓印光刻(NIL)的應用及市場

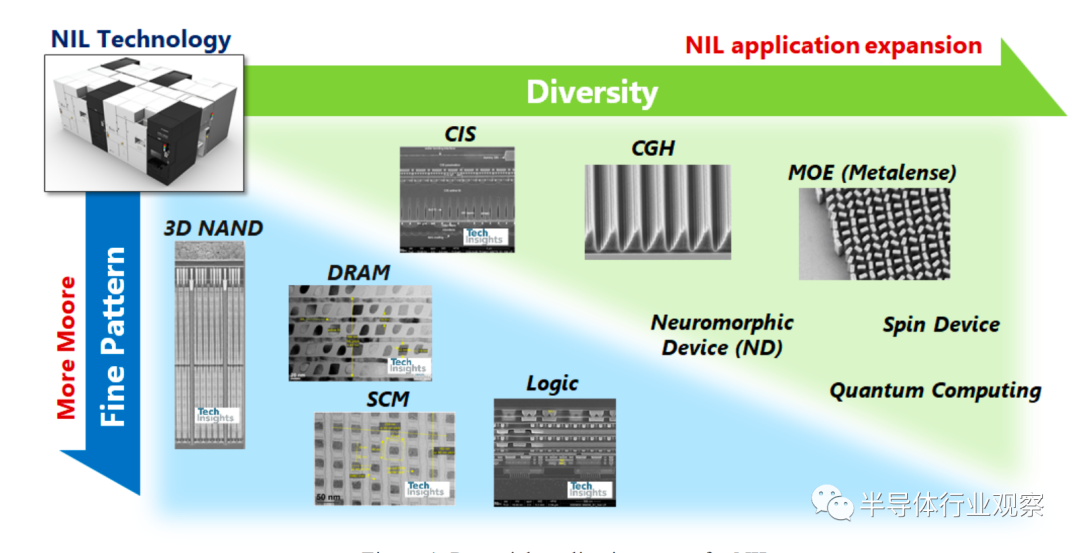

與半導體器件的其他制模方法不同,NIL有可能影響其他市場,如圖1所示。除了存儲和邏輯之外,覆蓋的器件空間還包括CMOS圖像傳感器、衍射光學元件和元光學元件(MOEs)。本文討論了動態隨機存儲器(DRAM)、邏輯(logic)和元光學元件(MOEs)。本文的這一部分還包括了關於如何解決缺陷以及機器學習如何推動NIL性能的更新。

a.DRAM

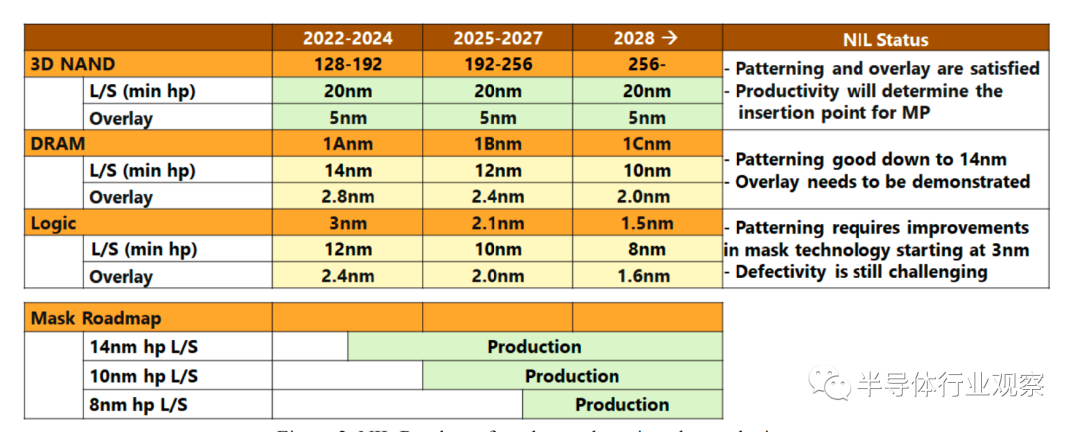

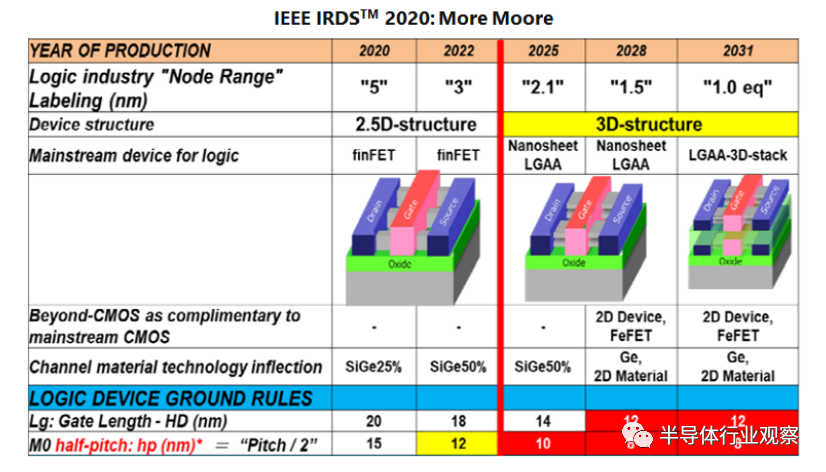

最近的工作集中在開發NIL的高級內存應用程序,如DRAM和存儲類內存。DRAM存儲器具有挑戰性,因為DRAM的發展路線圖要求持續擴展,最終達到14nm甚至更高的半節距(pitches)。對於DRAM,在某些關鍵層上的覆蓋比NAND Flash緊密得多,誤差預算為最小半間距的15-20%。對於14nm,這意味着2.1-2.8nm。設備路線圖,其中包括DRAM覆蓋要求如圖2所示。DRAM設備的設計也具有挑戰性,layout並不總是有利於像SADP和SAQP這樣的節距劃分方法。這使得直接打印過程,如NIL是一個有吸引力的解決方案。

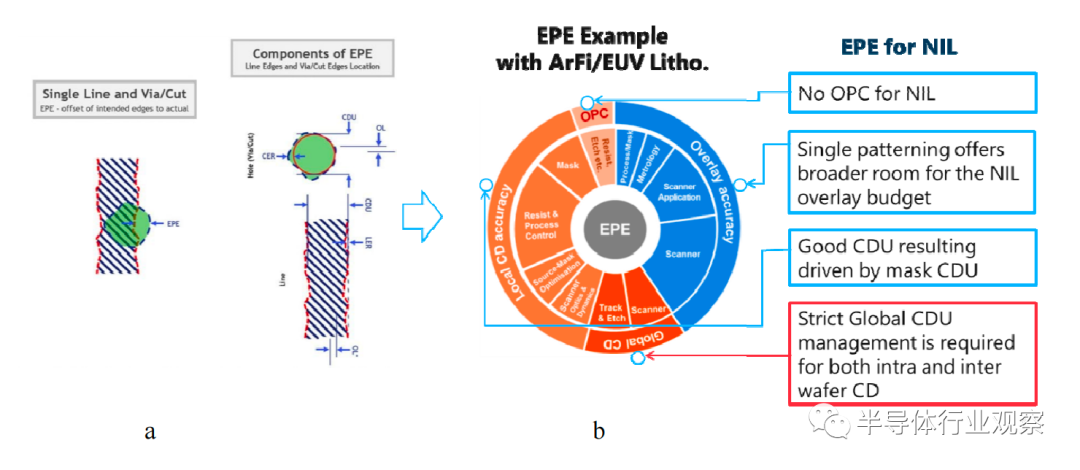

近年來,為了生產高產量的設備,設備製造商需要考慮的不僅僅是覆蓋誤差,幾年前,邊緣放置誤差的概念被引入。邊緣放置誤差(EPE)是指電路佈局的預期特徵與印刷特徵之間的差異。例如,考慮設備中的一條線,它必須精確放置,以便觸點能正確地落在這條線上。偏差或誤差導致不對中,進而影響器件的成品率。雖然概念上很簡單,但由於需要複雜的多重模式方案,EPE貢獻者的數量顯著增加。圖3a顯示了一個簡單的單線和通徑的EPE示例。Mulkens等人提出了同時需要ArF浸泡和EUV暴露的情況下的EPE預算(圖3b)[11,12]。EPE預算被分為四類:光學接近校正(OPC)、覆蓋精度、GCDU和LCDU。除了OPC之外,每個分類都有不同的預算。例如,LCDU包括源和掩模優化,掃描儀光學和動力學,以及電阻和過程控制。

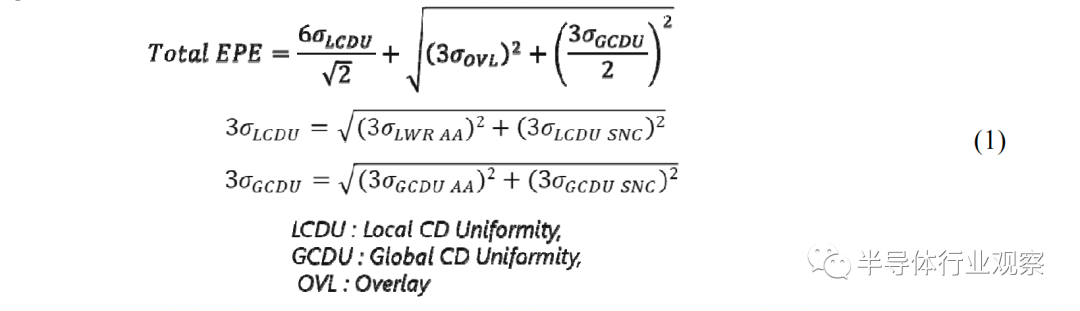

對於NIL,使用單一曝光步驟,術語變得更加簡化如下:

OPC條款:無需OPC疊加精度:單一圖案的應用為無重疊提供了更多的預算LCDU:良好的局部CDU由壓印掩模CDU和降低的線寬粗糙度驅動GCDU:嚴格的GCDU要求晶片內和晶片間的CD

基於此模型,DRAM活動層(AA)到存儲節點接觸點(SNC)情況下的總NIL EPE可表示為:

為了在納米壓印系統中解決覆蓋問題,有許多因素需要考慮,其中一些與光刻工具所要求的有很大的不同。在光刻中,高階補償是通過在曝光過程中操縱鏡頭和感光台來實現的。納米壓印需要一種不同的方法。結合兩種技術可以實現空值的高階失真校正。

一種是使用放大致動器,它通過一組壓電致動器施加力。其次是熱輸入,它由一個DMD提供,以糾正一個又一個場的失真。

HODC方法在過去已經被提出,最近附加的修正方法已經被應用,以驅動交叉匹配機覆蓋(XMMO)到ArF浸沒掃描儀到2nm。其他條款包括:

跌落模式補償印力壓印尖/傾斜控制精緻的掩膜圓片區卡盤氣動

關於這些校正方法的細節可在參考文獻14 - 16中找到。圖4圖解地説明了用於NIL的各種調優旋鈕。

圖4.要解決覆蓋問題,需要考慮許多因素。一般來説,這個過程可以分為兩類:對準和失真。

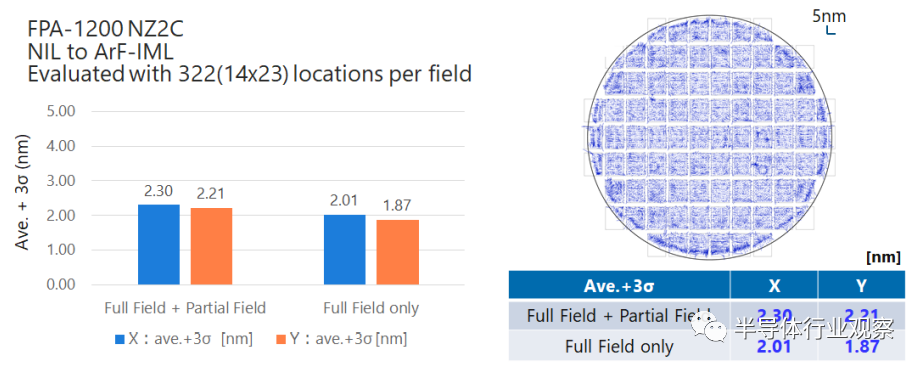

在圖5中,我們展示了最新的XMMO結果。NIL與ArF浸入式光刻機匹配,報告結果顯示了所有電場的測量結果,每個電場有322個位置。全場XMMO在2nm均值+3 σ的量級上,全電場和部分電場結果略高,x值和y值分別為2.30nm和2.21nm。最近的改進主要集中在局部電場上,包括設計用於提高覆蓋率收斂時間的方法,如圖6所示。

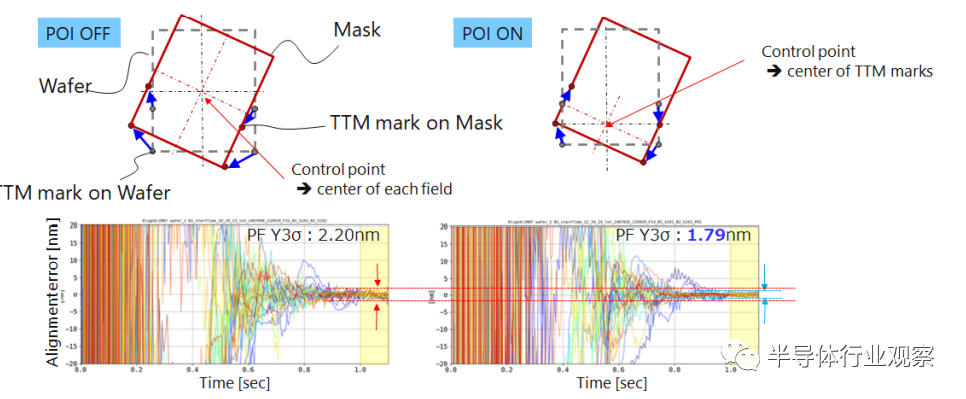

該示例中,在TTM標記中心放置用於對準的控制點或興趣點,從而加速對準收斂並減少部分電場中的重疊誤差。在本例中,Y方向上的對準誤差從2.20nm減少到1.79nm,3σ,而其他正在開發的方法包括一種新的最終壓印力和傾斜控制系統,該系統可以更精確控制壓印力和傾斜。

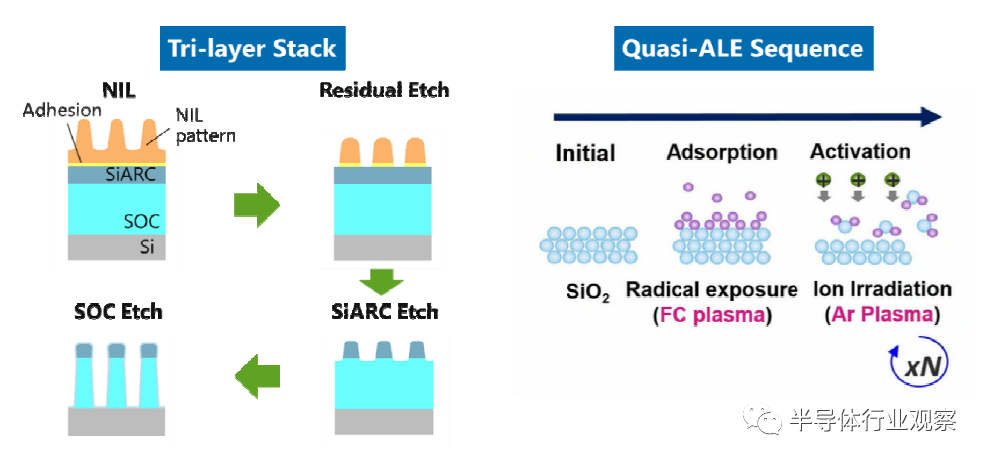

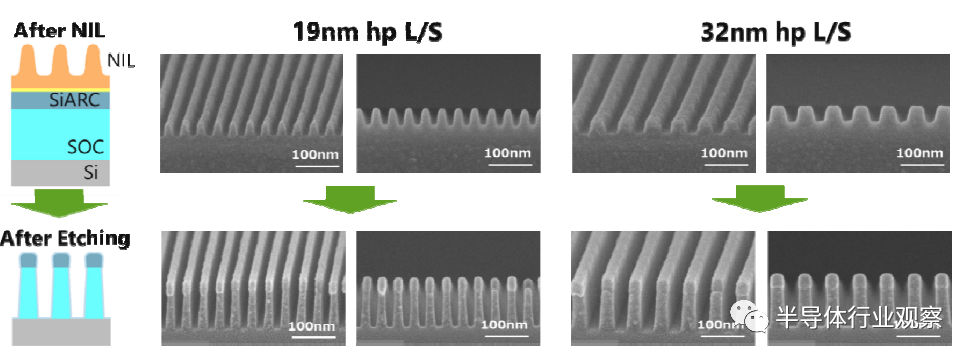

NIL圖案轉移工藝包括三個單獨的蝕刻步驟,從抗蝕劑剝離(殘餘層蝕刻)開始,然後是SiARC的蝕刻和旋塗式碳膜(圖7)。在TEL的初步研究中,將TEL開發的準原子層蝕刻工藝應用於SiARC層,q-ALE過程描述如右圖所示,通過碳氟化合物吸附和Ar離子交替轟擊的辦法來實現逐層蝕刻。

第一次蝕刻研究的結果顯示了19nm和32nm半間距線和間距(圖8)。

對於NIL,可以通過改變晶圓上的殘餘層厚度(RLT)來調整刻蝕後的CD,也可以在蝕刻後調整最終CD,因為在一個電場內以及從一個電場到另一個電場噴射的抗蝕劑體積,可以通過皮升的精度精準控制,所以可以實現上述工藝。一般來説,較薄的RLT在蝕刻後會導致較小的臨界尺寸,如圖9a所示。校正量是蝕刻工藝的函數,圖9b中顯示出了三個示例。注意隨着蝕刻條件的變化,斜率也會發生變化,因此可以進行1到3nm量級的調整。

圖案轉移過程也可用於管理線寬粗糙度(LWR),圖9顯示了一個示例。在NIL曝光和圖案轉移到19nm半間距特徵後,使用日立CG6300掃描電子顯微鏡測量LWR,特徵圖像和產生的無偏LWR,如圖10所示。請注意,在圖案轉移後LWR降低至2.6nm,這種類型的降低也可以在其他LWR研究中觀察到。最後,我們注意到,CD也可以根據NIL曝光劑量調整到較小的程度。感興趣的讀者可以參考Ogusu等人在本論文集中關於邊緣放置誤差的論文。

b.邏輯

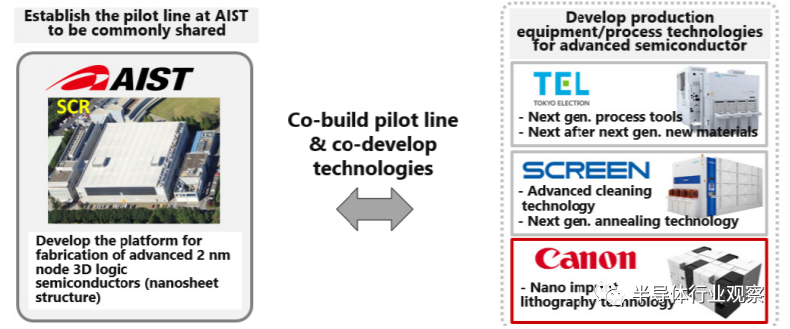

第二個令人感興趣的市場是邏輯領域。2021年,佳能與日本其他主要半導體制造設備公司一起,申請了新能源和工業技術發展組織(NEDO)發起的“Post-SG信息和通信系統增強基礎設施”研發項目,內容是邏輯設備的擴展小型化。該方案已獲得批准,主題為2nm節點後邏輯器件的擴展。該計劃包括使用美國國家先進工業科學與技術研究所(AIST)的共享試驗線,實現和驗證納米制造晶圓。NEDO項目組織的示意圖如圖11所示。

研發工作將以下圖所示的納米片器件為目標,在這個項目中,佳能將為BEOL開發12nm半間距及以下的NIL技術。

c. 光學元件(MOEs)

光學元件(MOEs)是一種有圖案的超表面,潛在用途是相機、手機,以及其他依賴聚光透鏡來形成圖像的設備中使用的光學元件。隨着超表面的引入,有望縮小透鏡並消除過去的限制。超表面通常指超材料的二維對應物,可以是結構化的,也可以是非結構化的,在水平維度上具有亞波長級別的圖案。

因為超構透鏡是平面結構,具備超薄特徵,所以不會產生色差——它們是“消色差透鏡”——因為所有波長的光幾乎同時通過。它們的優勢還包括可調色散——與具有固定色散的玻璃或其他傳統材料相比,能夠控制光的顏色如何分散。感興趣的波長包括了紅外和UV/Vis光譜。

在右圖所示的示例中,注意元素特徵大小和方向的變化。光學元件的早期工作主要依賴於電子束寫入,雖然對原型設計很有吸引力,但不適用於生產。NIL是光學元件生產圖案化的一個強有力選擇,因為與該技術相關的圖案化限制很少。

d.缺陷管理

所有設備的共同主題是缺陷和缺陷管理。每種設備類型都有自己的需求,這決定了管理各種缺陷源的策略和實踐。邏輯器件有最嚴格的要求,而DRAM相對於邏輯來説趨於寬鬆。金屬氧化物半導體更像是一種平均器件,所需的缺陷水平不像最先進的半導體電路那樣嚴格。

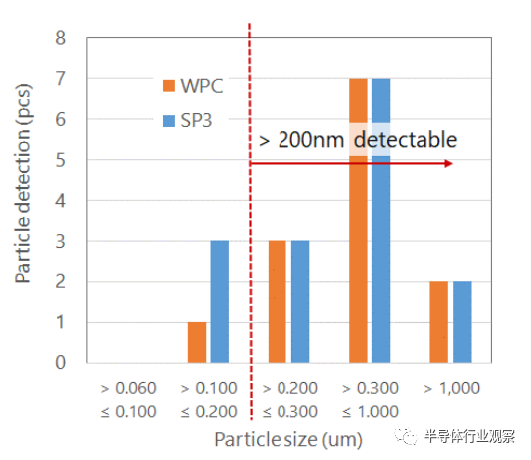

已經發表了幾篇關於減少零缺陷源的方法的論文。最近的工作着眼於原位粒子清潔和粒子檢測。晶片顆粒檢測(WPC)系統對空白晶片的靈敏度約為200納米,並通過與KLA-騰科SP3工具的比較得到了證實,如圖14所示。該工具將被用作避免在複製掩模上獲得任何重複缺陷的手段使用。

e. NIL的人工智能和機器學習

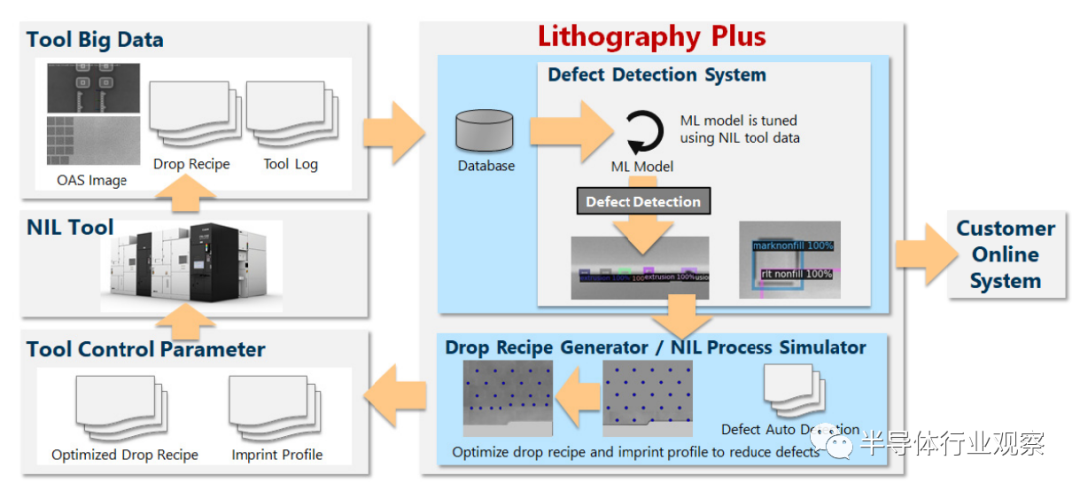

最後,佳能正在應用機器學習和AI技術進一步提高系統性能,提高生產力,並實現更自主的控制,以實現系統的快速升級。該系統軟件被稱為“光刻Plus”或Liplus。圖15顯示瞭如何將此應用於NIL的示例。在這個例子中,我們開發了機器學習模型,從自動掉落配方中檢查潛在的缺陷點,這樣掉落模式就可以快速地進行微調並反饋到工具日誌中,從而產生更有效的掉落模式。Liplus可以應用的其他領域包括對準優化、抗噴射和減振。

3.可持續發展目標

最後,我們將討論佳能在發展可持續發展和解決全球問題方面如何努力,以改善人類。這導致了“如圖16所示的目標列表”,其中包含了諸如負擔得起的清潔能源、負責任的消費和生產以及創新和工業基礎設施等主題。

這些指導原則適用於NIL技術,如圖17所示。NIL工具的開發是為了最大限度地降低功耗和防止浪費。通過將抗蝕劑直接噴射到晶片上的步進器區域上來最小化抗蝕劑的使用,該抗蝕劑的體積與填充壓印掩模上的浮雕圖像所需的體積相當,同時在形成的抗蝕劑圖案正下方有薄的殘留底層。

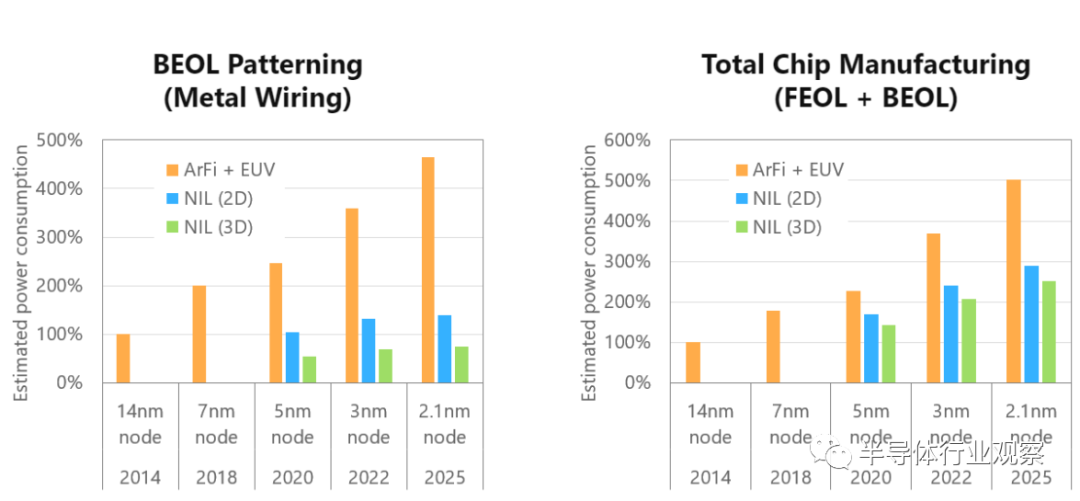

在功耗方面,NIL利用簡單的單步模式過程結合較低的功率暴露源來降低功耗,無論如圖18a和18b所示的設備節點是什麼。