微芯片時代正讓位於巨型芯片時代 - 《華爾街日報》

Christopher Mims

若將微芯片比作城市,那麼整個行業提升其性能的新策略可用一個詞概括:擴張。在某些情況下,我們最強設備內部的芯片已佔據如此大的"地盤",幾乎難以再被稱為"微"芯片。

工程師們實現這一目標的方式是將微芯片層層堆疊。這就像城市填充開發,只不過計算機中通常如薄餅般平坦的硅片正變成多層結構——用於內存、電源管理和圖形處理等功能的電路層彼此堆疊。

推動這種芯片設計趨勢的簡單現實是:持續提升芯片速度與設備性能的壓力從未消退,而芯片行業通過縮小晶體管尺寸來榨取更多性能的能力正遭遇技術壁壘。

因此,半導體工程師正通過緊密堆疊芯片來提升性能。電子世界核心處正在湧現硅材料的微型都市羣。某些情況下,這些蝕刻晶體構成的"城市羣"變得如此龐大,其物理規格已達芯片史上罕見水平。

目前多數芯片約硬幣大小,但部分芯片現已接近撲克牌尺寸,甚至出現餐盤大小的特例。

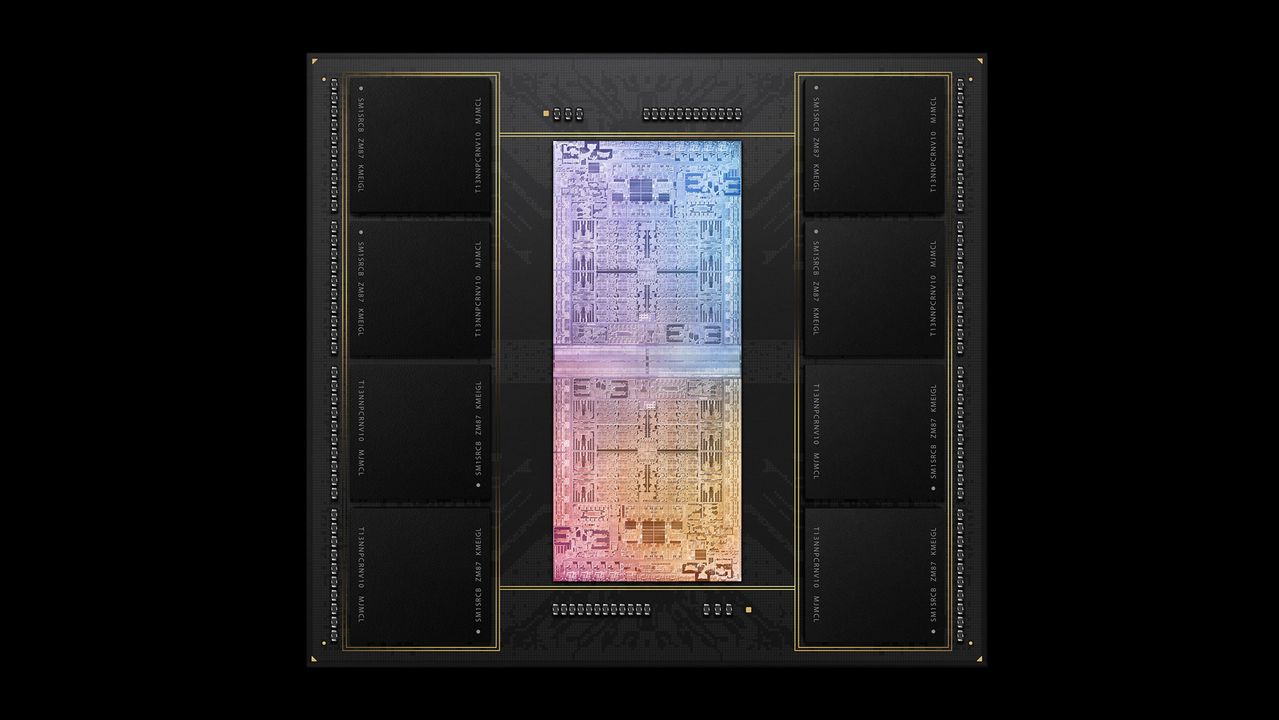

蘋果公司搭載於Mac Studio電腦的M1 Ultra芯片,內含1140億個晶體管。圖片來源:蘋果公司這類超級芯片不僅應用於全球最強大的超級計算機,也出現在家用設備中。微軟Xbox遊戲主機和索尼PlayStation 5均採用了超微半導體設計的此類芯片。蘋果在其Mac Studio的M1 Ultra芯片中採用了這一設計理念,而英特爾為超級計算機和數據中心打造的Ponte Vecchio處理器也以此為核心理念。

蘋果公司搭載於Mac Studio電腦的M1 Ultra芯片,內含1140億個晶體管。圖片來源:蘋果公司這類超級芯片不僅應用於全球最強大的超級計算機,也出現在家用設備中。微軟Xbox遊戲主機和索尼PlayStation 5均採用了超微半導體設計的此類芯片。蘋果在其Mac Studio的M1 Ultra芯片中採用了這一設計理念,而英特爾為超級計算機和數據中心打造的Ponte Vecchio處理器也以此為核心理念。

但面對密集電路執行海量運算產生的額外熱量,這些超級芯片給工程師帶來了散熱管理的挑戰。儘管能效更高,但其龐大體量也意味着它們有時會消耗大量電力。例如英特爾Ponte Vecchio芯片單次運算效率雖高,但功耗達600瓦,近乎一台吹風機的功率。若您疑惑為何移動設備尚未採用超級芯片,這便是答案。

從某些角度看,超級芯片正是延續摩爾定律趨勢的體現——英特爾創始人戈登·摩爾曾提出,消費者每兩年左右就能以同等成本獲得約翻倍的晶體管數量及算力。這一經驗法則雖屢被宣告終結,但芯片性能仍在持續提升。超級芯片正是業界為實現更高性能承諾的最新創新成果。

荷蘭公司ASML實質上壟斷了製造生產全球最先進芯片(含最小晶體管)所需的關鍵設備。但即便如此,該公司也表示要延續摩爾定律,僅靠縮小芯片上的元件尺寸已遠遠不夠。在2021年9月面向投資者的報告中,該公司提出了"系統級縮放"理念。ASML發言人證實,該理念是對現有芯片微縮技術的補充。

用城市發展作比喻:如果無法縮小住房單元面積或提升交通效率,就不得不向高空和外圍擴張——正如過去50年新加坡國土面積增長了近四分之一。

合眾為一

製造巨型芯片絕非易事,部分原因在於需要以納米級精度定位每個芯片元件,並在沒有微型焊槍輔助的情況下實現連接。

這之所以成為可能,主要得益於芯片行業長期忽視的"封裝"領域近期取得突破。封裝是芯片製造後的關鍵但常被忽視的環節,需將芯片與微細導線連接幷包裹在塑料外殼中,再安裝到佈滿連接電路的基板上。

在傳統設備中,接收和發射無線電波(例如通過Wi-Fi通信)的芯片可能需要連接到另一個執行通用計算的芯片,它們之間的連接實際上被稱為"總線"。但就像現實世界中的對應物一樣,這種總線在這些相鄰的硅城市之間傳輸任何東西都算不上快速。而新型的巨型芯片封裝技術則直接將這兩個芯片(甚至可能更多)連接起來。其結果更像是將所有芯片集中在一個屋檐下,就像一棟高層建築。

加州大學洛杉磯分校教授、前IBM封裝開發總監Subramanian Iyer表示,傳統微芯片必須將其近三分之一的面積和同樣比例的功耗用於將芯片的計算結果傳輸到設備的其他部分的電路上。堆疊芯片使它們之間的通信更快,因為這允許它們之間有更多的連接,就像在摩天大樓中乘電梯在樓層之間移動比步行穿過整棟建築到達相鄰建築要快得多。

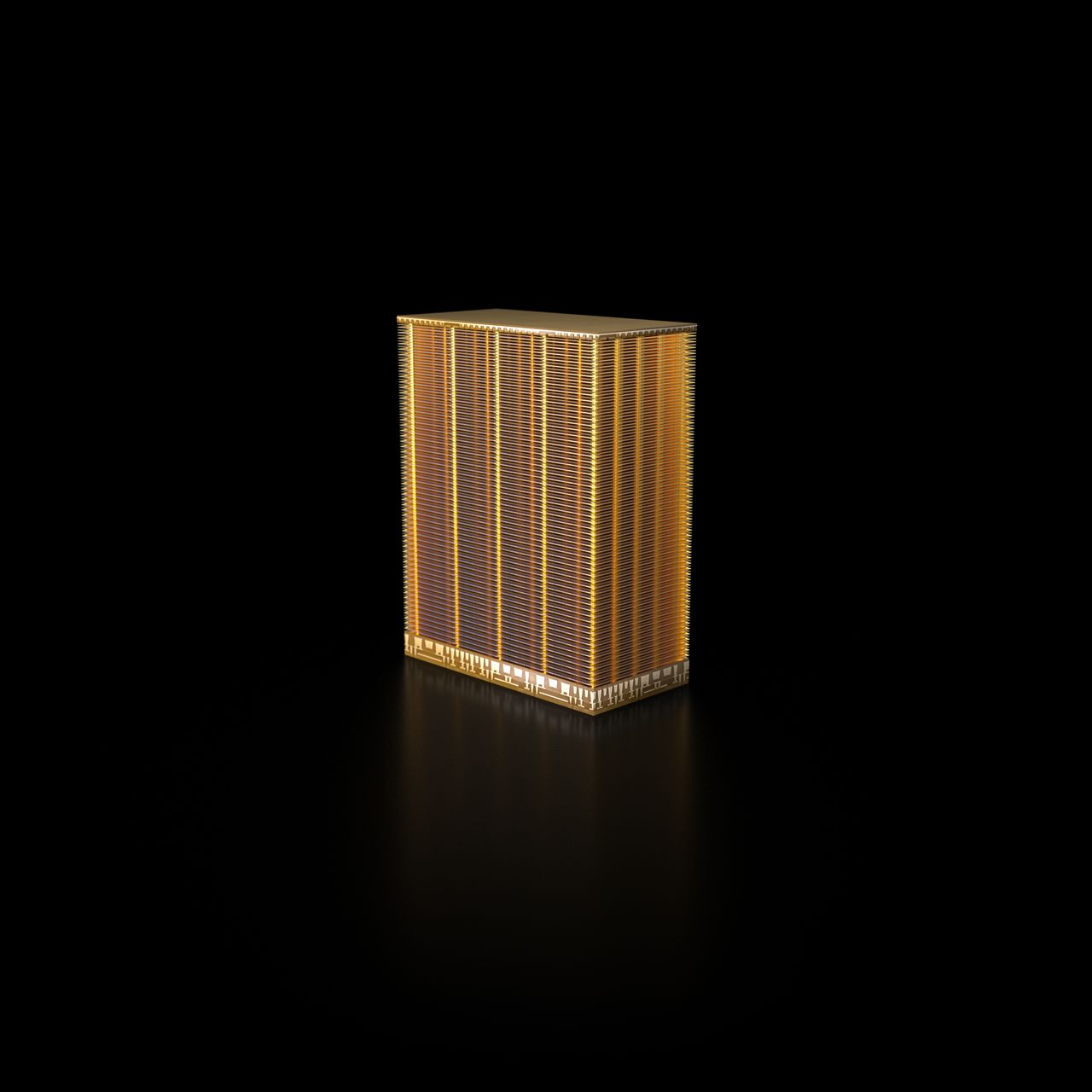

美光科技的232層閃存芯片是某些微芯片在第三維度上擴展程度的一個極端例子。圖片來源:美光科技這種情況在存儲芯片中早已成為標準——總部位於愛達荷州博伊西的美光科技剛剛發佈了一款232層存儲芯片,如果它是一棟建築,放在拉斯維加斯大道上也不會顯得格格不入——但直到最近才應用於其他類型的微芯片。

美光科技的232層閃存芯片是某些微芯片在第三維度上擴展程度的一個極端例子。圖片來源:美光科技這種情況在存儲芯片中早已成為標準——總部位於愛達荷州博伊西的美光科技剛剛發佈了一款232層存儲芯片,如果它是一棟建築,放在拉斯維加斯大道上也不會顯得格格不入——但直到最近才應用於其他類型的微芯片。

實現超級芯片和芯片堆疊的關鍵基礎是一種名為“小芯片”的新型微芯片。它摒棄了部分傳統電路設計,以更直接的方式與其他小芯片通信。通過建立眾多短距離的直接連接(這些連接通常採用與芯片相同的硅材料製成,而非銅或其他金屬),這些小芯片可以與其他小芯片融合形成超級芯片。

伊利諾伊大學厄巴納-香檳分校電氣工程教授拉凱什·庫馬爾表示,構成超級芯片的各小芯片間直接通信的能力,使它們能像單一巨型微處理器般運作。

英特爾最新發布的Ponte Vecchio圖形處理器就是極致案例。每塊處理器由63個不同小芯片組成,這些垂直堆疊與緊密排列的小芯片總面積達3100平方毫米,包含1000億個晶體管。相比之下,筆記本電腦核心芯片通常不足150平方毫米(約為前者的1/20),晶體管數量約15億個,僅佔1.5%。

採用堆疊小芯片技術顯然是英特爾處理器的未來方向——其已發佈但尚未交付的大部分服務器、台式機和筆記本處理器都採用該技術。英特爾高級研究員達斯·夏爾馬指出,這種方式"提供了全新的芯片製造方法,比傳統工藝更快速且成本效益更高"。

他特別強調,小芯片堆疊技術能讓英特爾在不增加芯片二維面積或總功耗的情況下提升新一代台式機和服務器芯片性能。這看似有違直覺,但需理解芯片功耗是設計選擇的結果,而節能正是行業最高優先級目標之一。通過優化芯片各部分通信所需的時間和能耗,堆疊小芯片可幫助工程師深度挖掘現有設計潛力。當然當性能優先時,小芯片也能用於製造體積更大、功耗更高的微芯片。

開創當前小芯片技術時代的AMD,已推出內含多枚小芯片的處理器。該公司發現,僅需將內存芯片堆疊在CPU(計算機中執行大部分非圖形計算任務的芯片)之上,就能顯著提升系統運行速度。

共舞時刻已至

雖然基於小芯片的超級芯片目前數量稀少,且僅出現在最強大的系統中,但安西斯公司產品營銷總監馬克·斯温南表示,這一製造趨勢正在加速。安西斯開發的物理仿真軟件在微芯片設計行業廣泛應用(其客户大多要求匿名,但包括三星在內)。

公司發言人透露,自2019年以來,安西斯客户涉及堆疊小芯片的項目數量增長了20倍(當時僅有個位數)。作為參照,全球範圍內此類芯片設計項目總數估計常年維持在數百個量級。

今年三月,名為"通用小芯片互連聯盟"(UCIe)的行業組織宣佈,英特爾與AMD這對宿敵共同參與了其最新標準的制定。該標準旨在讓遵循者能設計出與其他廠商生產的小芯片互聯互通的產品。聯盟成員還包括Arm、台積電、三星等微芯片設計與製造巨頭。

UCIe主席兼英特爾高級研究員德本德拉·達斯·夏爾馬錶示,建立小芯片連接標準的願景在於,未來任何公司都能從其他企業購買小芯片,並根據自身特定需求將它們組裝成所需的“科學怪人”式定製芯片。用城市來比喻的話,想象一下,如果你能選取紐約、里約和東京的精華部分,然後將它們融合成一個完全符合你個人品味的夢想之城。

當然,實現這一目標需要眾多企業的共同參與。夏爾馬博士指出,UCIe標準的本質以及加入該組織的知名企業名單,已充分證明其必將成功。

但伊利諾伊大學的庫馬爾博士持保留態度:“在這個競爭激烈的行業裏,任何標準化都是挑戰,因為必須做出妥協,而並非所有企業都有合作共贏的動力。”

全行業對此技術興趣高漲的主要推動力,源於亞馬遜、谷歌、微軟、特斯拉等越來越多的企業希望打造自有的、更強大的微芯片,以運行從雲服務、智能手機到遊戲主機和汽車等各種設備。“現在大型企業都設有專門部門,其核心業務完全依賴於芯片性能。”斯維南先生表示。

加州大學洛杉磯分校的艾耶博士補充道,人工智能和機器學習系統對現有硬件的貪婪需求也助推了人們對超級芯片的關注。雖然有些公司通過傳統方式製造巨型芯片來應對這一需求——例如初創公司Cerebras開發的芯片佔據了通常可蝕刻數十個微芯片的整個晶圓表面——但包括艾耶博士團隊在內的其他研究者,正致力於開發由小芯片組成的AI專用超級芯片。

從超級計算機到可穿戴設備

人們對巨型芯片的熱情表明,有朝一日它們可能超越當前在注重性能而非功耗或電池續航設備中的應用範疇。

庫馬爾博士表示,就像通過快速交通系統連接城市與郊區一樣,未來的小芯片可能通過新穎方式實現遠距離互聯。

表面上看這並不合理,因為增加芯片間距會延長通信耗時。但至少帶來一個意外優勢:用柔性電路連接的微型芯片可製造出可彎曲計算機,甚至可能催生全新設備類型。

庫馬爾團隊正在進行的實驗表明,例如小芯片可通過柔性電路連接成可穿戴系統,或能包裹飛機機翼等曲面的系統。艾耶博士稱其團隊正在研發柔性手機所需的所有基礎模塊。

儘管巨型芯片面臨挑戰,但將現有微芯片分解為可重組為更強大計算單元的小型芯片趨勢正加速發展。事實上,若沒有這種技術,關於微芯片持續改進的摩爾定律將難以為繼。

簡而言之:芯片擴展浪潮才剛剛開始。

欲獲取更多《華爾街日報》科技分析、評測、建議及頭條新聞,請訂閲我們的每週通訊。

致信 克里斯托弗·米姆斯,郵箱:[email protected]

刊登於2022年7月30日印刷版,標題為《巨型芯片時代即將來臨》。