先進封裝與異構集成路線圖_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。03-17 13:40

信息與通信技術(ICT)是那些需要移動、存儲、計算、通信和保護的數據呈指數級增長的來源。依賴於特徵尺寸縮減(維度縮放)的傳統半導體技術即將達到其物理極限,在提高系統性能方面仍面臨重大挑戰。新技術節點的進展已經放緩,超過了兩年更新一次的技術節奏。越來越需要“異構集成(HI)”和“More than Moore”來替代傳統晶體管擴展,以實現具有成本效益的封裝系統(SiPs)。HI將是下一代計算和通信系統的成本和功率效率實現的基礎。通過異構集成實現的先進封裝將是至關重要的,因為它“為產品密度和尺寸的創新提供了一條替代途徑”,“正如摩爾定律在過去55年中引領了全球半導體行業的進步一樣,異構集成是未來的關鍵技術方向。”

HI技術的進步對於滿足預期的半導體在ICT方面的重大變化的十年計劃是必要的,包括生成更智能的世界機器接口所需的模擬硬件(#1)、全新的存儲器和存儲解決方案(#2)以及解決高度互聯繫統和人工智能中新出現的安全挑戰的硬件(#4)。然而,HI技術作為解決方案至關重要的重大轉變是使通用計算能耗呈現指數增長(#5)。能源消耗每三年翻一番,超過了維度縮放所實現的效率提高,因此,需要新的計算範式。

通常,不同的應用需要特定領域的體系結構和適當的系統集成策略,以有效實現性能、功率、面積、成本(PPAC)權衡,同時確保信號和功率完整性、功率轉換和傳輸、可測試性和安全性。系統集成的可能解決方案策略包括將單獨製造的組件水平集成到更高級別的SiP中、單獨小芯片的三維(3D)堆疊以及在單個單片集成片上系統(SoC)中複雜的邏輯和存儲器分層製造。SiP架構和物理設計需要高保真度以及高效的建模工具和技術,包括基於機器學習的工具和技術。

邁向高密度3D系統集成將提高帶寬密度和能效,水平和垂直互連間距縮放以及下一代互連對於實現高帶寬密度和能量效率至關重要。考慮到I/O帶寬將與計算內核的規模成比例地擴展,伴隨着封裝引腳數和I/O功耗的指數增長,通常需要在光學互連中實現高帶寬密度、能效和覆蓋範圍的替代創新。

系統集成挑戰超出了芯片封裝的協同設計;它包括封裝材料選擇、互連間距縮放的工藝開發和熱解決方案設計,同時滿足可靠性和製造成品率目標。這些反過來又需要複雜的熱點以及缺陷度量、測試和仿真,以實現對封裝性能和可靠性的基本理解。最後,新型材料是互連、高密度基板、散熱和新興器件開發創新的基礎。

芯片封裝架構與協同設計

在人工智能、高性能計算、高分辨率傳感和其他新興應用中,對帶寬、延遲和能效的需求與日俱增。儘管同構設計的最新進展有助於緩解一些問題,但它們的擴展趨勢仍然滯後。在這種背景下,同構芯片之外的技術創新,尤其是宏觀和微觀層面的2.5D/3D異構集成,對於實現未來具有各種類型小芯片的ICT系統、併為微電子設計帶來顯著的性能和成本效益至關重要。這種範式轉變將推動小芯片設計IP、異構架構、片上/封裝網絡和可靠系統集成方面的創新。

一些挑戰和研究需求包括:

**為HI設計IP:**芯片及其信號接口為微電子生態系統帶來了一種新的硅模塊,具有高帶寬、高面積利用率和低成本。它們開啓了一種新的IP複用技術和商業模式,允許在沒有工藝限制的情況下靈活地生成不同的功能宏。這種變化既需要設計能力來定義物理內核和小芯片到小芯片的接口,也需要硬件軟件協同設計來對可重用IP模塊進行分類。

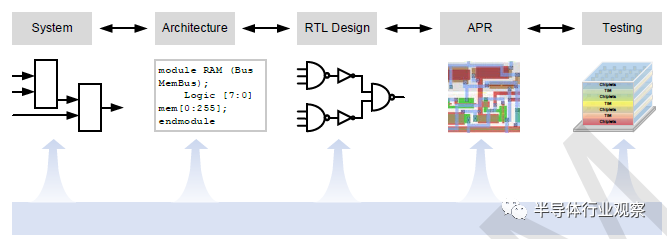

**異構架構:**小芯片和封裝設計之間的緊密協作在整個週期中至關重要,包括設計工具、模型和工作流。系統架構師在設計過程的早期就參與其中,以分析系統和軟件包,將設計劃分為各種小芯片,並評估計算和數據移動中的必要權衡。現階段的設計和驗證工具,如SystemVerilog,需要結合封裝設計和規劃知識,以支持協同設計工作流。這是對當今分離的ASIC和封裝設計過程的重大改進。此外,HI系統的早期預測分析對於最小化架構/微架構定義和設計實現之間的迭代成本至關重要。

**HI系統的合成工具:**由於封裝成為設計過程中的關鍵部分,因此有必要將封裝結合到流程的每個步驟中,包括架構定義、RTL設計、佈局和路由、驗證以及時序/功率分析。新的工具集還需要在它們之間有一個平滑的接口,並支持未來的小芯片設計套件。HI合成的獨特挑戰包括小芯片到小芯片接口的時序分析、熱/機械應力分析以及各種組件的功率傳輸和完整性。

**測試和可靠性:**異構系統包含多個具有顯著不同電氣、機械和熱性質的組件。異構系統的未來測試需要具備足夠的模塊化,以解決每個組件的特定測試方法,同時兼顧覆蓋範圍、複雜性和成本。自測試(例如內置自測試(BIST))是一種優選的解決方案,但需要對多個功能的聯合測試進行更多的研究。隨着各種組件之間的熱/機械相互作用在3D集成中不斷增加,可靠性評估需要從當前針對每個模塊的經驗/統計方法轉向構建物理可靠性模型,以描述其在產品層面的相關性。

下一代互連

使用更小的晶體管節點(低於20nm)縮小管芯的成本優勢已不再可實現。這就是一種新方法的必要之處,即將單片芯片分解為更小的單元,稱為小芯片(chiplet)。為了通過器件小芯片和無源元件的異質集成(HI)實現功能擴展,基板必須從芯片載體過渡到集成平台。此集成平台的驅動屬性需要新的高級封裝方法來實現這些基本要求:

1.性能優化:能夠為每個IP塊/小芯片選擇最佳的硅工藝節點。

2.產品定製:通過選擇可提供最佳性能的小芯片組合,實現每個產品的定製。

3.成本降低:與單片SOC相比,由於單個小芯片的產量更高,因此能夠降低成本。

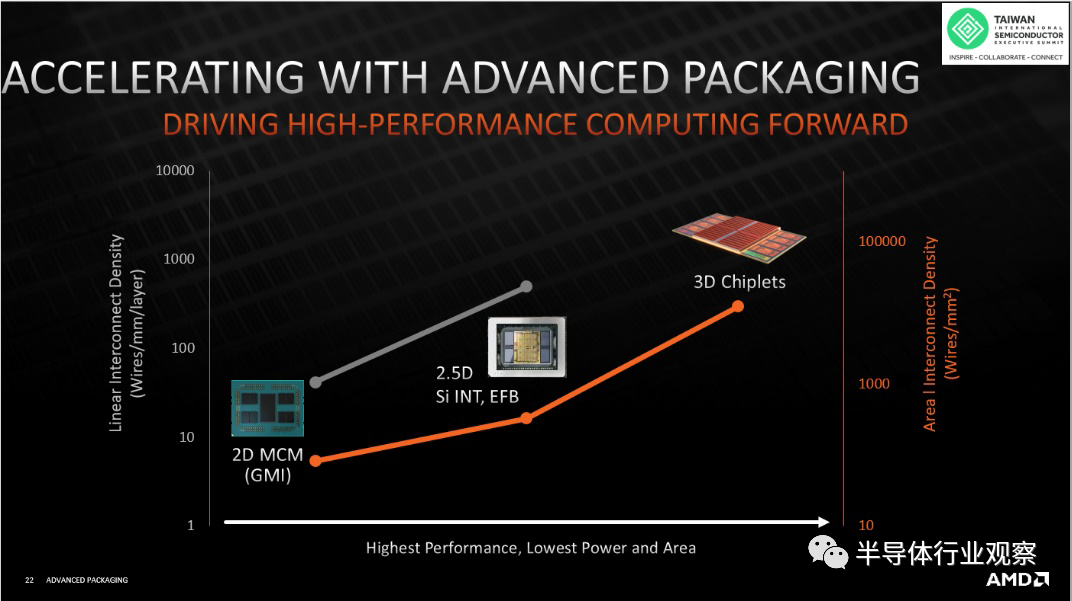

我們認為,隨着行業朝着為每個應用程序定製的高性能、低功耗解決方案發展,小芯片的數量將繼續增長。下一代封裝需要支持異構集成中的這一爆炸式增長,因為它支持容納非常小間距I/O管芯(<10μm間距)和非常小的線/空間(低於1μm L/S)電路的互連。圖1顯示了這一趨勢,只有使用3D小芯片集成才能實現以下兩個基本性能要求:

1.以IO/mm和IO/mm²衡量的更高帶寬

2.以pJ/Bit衡量的更高效率

表1:實現未來HI的技術開發路線圖。綠色-已開發並準備好製造的工藝,黃色-需要額外的開發工作,紅色-HVM所需的主要開發工作。

功率傳輸和熱管理

從20世紀70年代早期引入微處理器到今天,微處理器在複雜性和性能方面經歷了重大的發展。微處理器性能的指數級增長符合摩爾定律,即芯片中的晶體管數量每兩年將增加一倍。直到2000年代初,基於Robert Dennard歸納的傳統縮放方法在保持功率密度恆定方面非常有效,即使晶體管在每一代中逐漸變小。然而,隨着晶體管特徵尺寸接近原子尺寸,低於閾值的泄漏成為一個問題。因此,工藝工程師通過材料和晶體管結構的創新以實現必要的面積縮放,以符合摩爾定律。

雖然非傳統的縮放方法在縮放晶體管面積的同時提高性能方面相當成功,但它們在降低功率方面並沒有那麼有效。微處理器的功率密度在2000年代初隨着Dennard縮放定律的崩潰而開始增加。此外,雖然它提供了減少柵極延遲的方法,但是縮放互連尺寸並不意味着RC互連延遲的減少。當互連延遲接近時鐘週期的很大一部分時,它就成為了提高處理器頻率的另一個瓶頸。雖然體系結構的改進促使了每時鐘指令(IPC)的改進,但這不足以克服頻率縮放的不足,這導致了單核性能擴展的放緩。隨着單核性能的下降,微處理器架構師一直在使用多核架構並且並行化工作負載以最大化性能。

內核數量的增加導致了電源軌的增加,這加劇了微處理器供電問題的複雜性。另一個造成額外功率傳輸挑戰的因素是當前的趨勢,即通過擴展熱設計功率(TDP)來為不斷增加的內核供電。在不久的將來,這些高功率段中的微處理器將汲取超過1000A的電流。當談到低功耗的移動處理器時,主要的重點是降低設備的整體形狀因數和最大化電池壽命。結果,微處理器、存儲器和電壓調節器所佔的面積被迫縮小,為更大的電池騰出空間。此外,對更薄設備的推動意味着微處理器的高度以及電感器和電容器等功率傳輸部件都必須收縮。

直到最近,晶體管密度的增加使得大多數系統級功能能夠集成到單個微處理器芯片上。雖然這有助於大幅減少整個系統的面積,但這種方法並非沒有缺點。在SoC上實現的許多邏輯電路在最新的工藝節點上沒有獲得顯著的性能優勢。在較便宜、較落後的工藝節點上實現這些電路可以降低系統的總體成本,並將性能影響降至最低。通過使用先進的封裝技術,如硅插入器、嵌入式多芯片互連橋(EMIB)和3D堆疊芯片技術,推動設計實現異構集成。由於不同工藝節點的不同管芯上的電路具有各自最優的電源方案,因此朝向堆疊管芯架構的驅動帶來了顯著的功率傳輸挑戰。多個堆疊的芯片經常爭奪功率傳輸金屬資源,以支持各自芯片上的不同電源軌。由於必須通過多個硅通孔(TSV)傳輸功率,位於整個堆疊的頂部管芯上的晶體管也將看到電壓降的增加。添加更多的TSV可以幫助緩解這一問題,但對下部管芯的面積利用率有不利影響。

**1.**功率傳輸解決方案

集成電壓調節器(IVR)已成為解決前面討論的幾個功率傳輸挑戰的關鍵解決方案。IVR被廣泛定義為包含封裝或管芯上電壓調節的最後階段的解決方案。IVR選項越來越受歡迎,並已在許多商用微處理器上實現。儘管由於缺乏平台級資源,在平台上安裝數十個電壓調節器是不現實的,但通過細粒度電源管理將功耗降至最低的方式已經使得引入了大量的電源軌。更有效的解決方案是使用更少的平台級電壓調節器,它可以將功率輸送到封裝或管芯上的各種集成電壓調節器。推動IVR的另一個因素是處理器功率水平的穩步增長,尤其是數據中心CPU和GPU。隨着功率水平的提升,功率傳輸網絡中的路由損耗會對整體系統效率產生重大影響。IVR可以通過以更高的電壓為處理器供電來解決這個問題,這減少了通過功率輸送網絡的電流,並使PD網絡中的路由損耗最小化。在高功率水平下,路由損耗的減少足以抵消IVR帶來的轉換損耗。

(1)IVR分類

IVR可以根據其拓撲結構進行粗略分類。最簡單的片上電源傳輸解決方案是電源門開關。電源門用於關閉非活動電路的電源,以最小化其功耗泄露。功率門的一個常見應用是使用單個平台級電源向多個核傳輸功率。功率門的最大缺點是無法調節輸出電壓,線性或低壓降(LDO)調節器通過在其設計中控制迴路來解決這一缺點。由於沒有能量存儲元件,LDO也相對容易在管芯上實現。然而,LDO通常限於輸入電壓接近輸出電壓的應用。因此,它們不適合高功率軌道,因為使用IVR的動機是通過以顯著更高的電壓引入功率來最小化路由損耗。

開關調節器更適合於需要更高輸入電壓的IVR實現。開關電壓調節器使用能量存儲元件來實現高效率的電壓轉換。降壓調節器中的儲能元件是電感器,而開關電容器電壓調節器(SCVR)使用電容器作為其儲能元件。由於電容器通常具有比電感器更高的能量存儲密度,因此可以設計高效緊湊的SCVR。然而,簡單的SCVR存在調節差的問題,並且最適合於從輸入到輸出的固定比率轉換,並且當輸入到輸出電壓顯著偏離最佳比率時,通常效率較差。

最近,已經引入了新的基於開關電容器的混合拓撲來解決這些缺點。還實施了基於降壓調節器和線性調節器的混合方案。為了用更少的電感器生成可擴展數量的管芯上功率域,已經實現了單電感器多輸出(SIMO)穩壓器,並增加了用於瞬態管理的線性穩壓器。

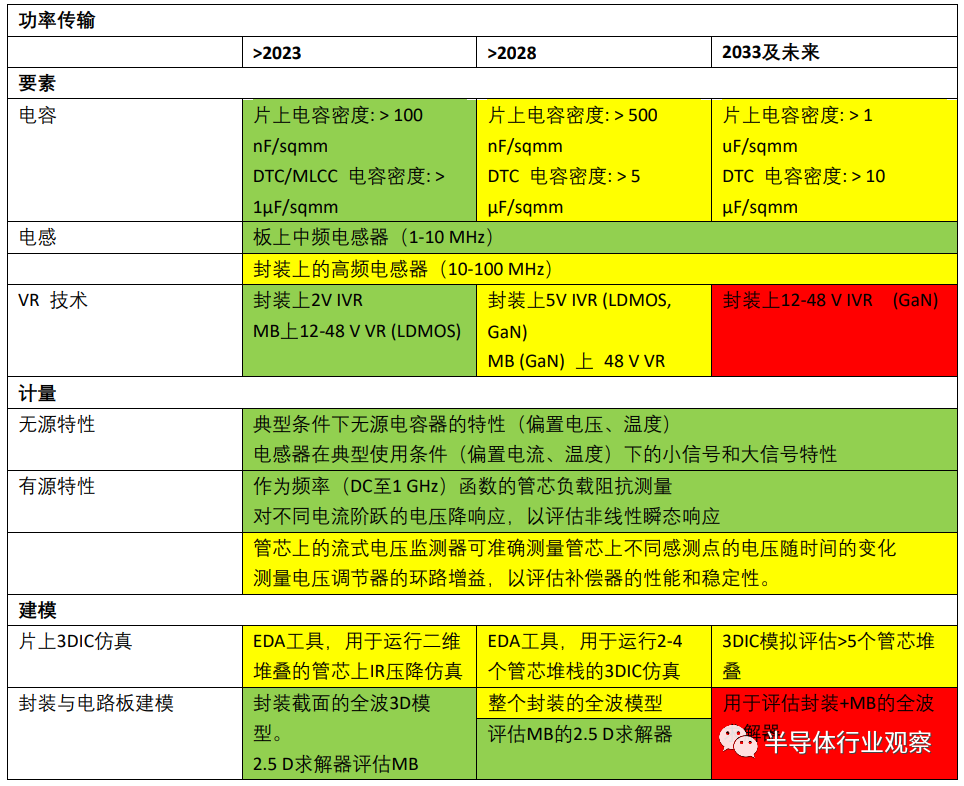

表2:功率傳輸要求(綠色:可用解決方案。黃色:需要額外的開發工作。紅色:需要大量的開發工作)

瞭解解決高級封裝和異構集成的熱挑戰的未來路線圖需要首先回顧歷史架構趨勢。在早期的高性能計算應用中,摩爾定律(晶體管縮放)和旨在提高性能的產品架構選擇導致了每個連續工藝節點的功率和功率密度大大提高。這導致熱管理的第一個重點是解決高功率密度(由於更高頻率的晶體管操作和工藝縮放)以及解決更高的總封裝功率。這一趨勢在2000年代初被打破,這要歸因於多核架構等各種改進,以及對每時鐘週期指令的關注。在這段多核時期,重點是為計算性能和並行指令提供額外的內核。這個時代還見證了IP(如內存控制器、圖形等)異構集成的第一次變革。近年來,由於先進的封裝技術,這一趨勢明顯加快,這些技術允許在封裝級別集成不同數量的小芯片、功率傳輸元件、存儲塊等,通常集成到3D異構封裝中。最近的產品包括超過1000億個晶體管和47個有源計算裸片,跨越集成到單個封裝中的五個不同工藝節點。

這些趨勢預計將繼續,並且很可能會加速發展到未來的計算機產品中。因此,我們可以預見到的工藝規模和先進封裝的熱挑戰包括:

1.由於持續的工藝縮放以及性能/頻率隨時間增加,小芯片級別的功率密度增加。在3D堆棧將產生額外的有效功率密度的架構中,這一變化將加劇,需要仔細的堆棧間佈局優化,以將功率密度降低到架構能夠支持的程度。

2.異構體系結構有利於多點熱優化點,因為該部件可能會承受大量工作負載,並且內核/執行單元數量會持續增加。這一問題變得越發尖鋭,因為先進的封裝熱結構通常需要權衡,以犧牲另一部分來改善封裝的一部分的熱性能。

3.高速I/O的功率密度繼續增加(例如,高速SERDES)。在一些情況下,期望將這些IP塊放置在3D堆疊的基底管芯中,這將增加耗散IP塊功率的難度,因為基底管芯和3D堆疊的頂部之間的較高熱阻是由硅金屬堆疊中的互連和介電層(面對面和麪對背3D堆疊中)引起的。

4.封裝規模和系統規模的熱優化:隨着系統冷卻向封裝靠攏,封裝的尺寸和複雜性不斷增加。這導致需要將系統熱沉與封裝熱設計進行協同設計。這是在移動空間中首次發現的,筆記本電腦熱解決方案中熱管的位置、大小和方向需要考慮到封裝內核平面圖。隨着3D集成和先進封裝的不斷增長,同時系統級的熱解決方案也有望得到改善,這一需求預計會增長。

5.隨着3D封裝中每層硅厚度的減小,熱點的橫向擴展水平顯著降低。當熱量離開封裝時,這增加了有效功率(熱)密度,但也增加了對封裝內熱缺陷的敏感性。例如,當硅厚度從700μm減小到100μm時,與封裝接觸的熱界面中的臨界缺陷尺寸相應減小。這需要對3D堆棧內的熱特性(特別是電導率)的高分辨率(x、y和z)理解。

上述挑戰推動了對新要素、計量和建模技術的需求,如表3所示。

表3:熱管理要求。(綠色:可用於製造的解決方案。黃色:需要額外的開發工作。紅色:HVM需要大量開發工作。白色:僅供參考)

材料

高級封裝中使用的材料被定義為在處理後留在半導體封裝中的成分(例如,直接材料)。這些材料包括載體(基板、引線框、插入件、構建材料、再分佈層)、管芯連接、底部填充物、封裝材料和焊料材料,以及熱溶液(例如,熱界面材料等)。雖然有“輔助”材料用作工藝耗材(如膠帶、抗蝕劑、化學品、泥漿),但這些不在本節範圍內。

特定應用的驅動因素,包括高性能計算、電源包/電氣化和超太赫茲無線基礎設施,將用於指定在先進封裝環境下提供系統級性能增強所需的新材料能力。重點領域包括所需的材料改進,以實現更高的封裝佈線密度/小型化、更優的電氣性能,以及機械和熱性能增強,以提高可加工性和可靠性。需要先進的熱解決方案,以在最大器件結温、尺寸和成本的限制下實現系統級性能。所需的封裝平台從傳統的層壓和引線框架封裝到高密度倒裝芯片/扇出晶片級和大尺寸面板級封裝,以實現下一代產品成本和性能目標。

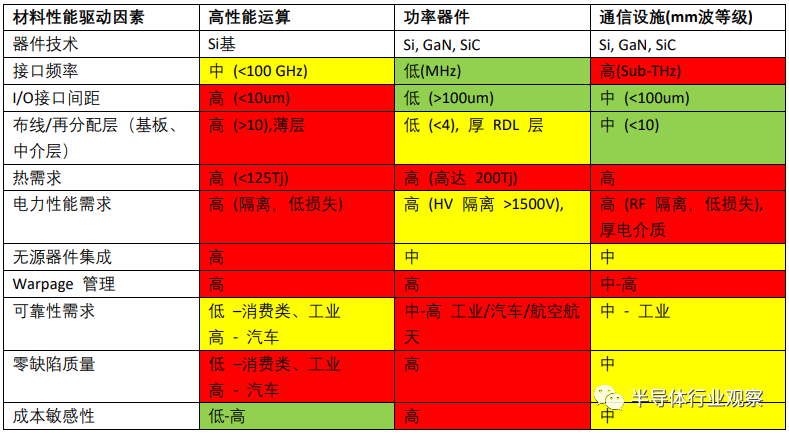

下表中列出的特定應用性能驅動因素驅動加工特性和性能的改進。第3章概述了具體的材料要求和路線圖需求。

表4:封裝材料能力評估。綠色:可用於製造的解決方案。黃色:需要額外的開發工作。紅色:HVM需要大量開發工作。

為了通過器件小芯片和無源組件的異構集成(HI)實現功能擴展,基板必須從芯片載體過渡到集成平台。該基板平台的驅動屬性或元素需要轉換到新的縮放目標。基板平台的這種驅動屬性或元件是通過嵌入分立組件用於芯片互連的凸塊間距和I/O縮放以及功率傳輸。

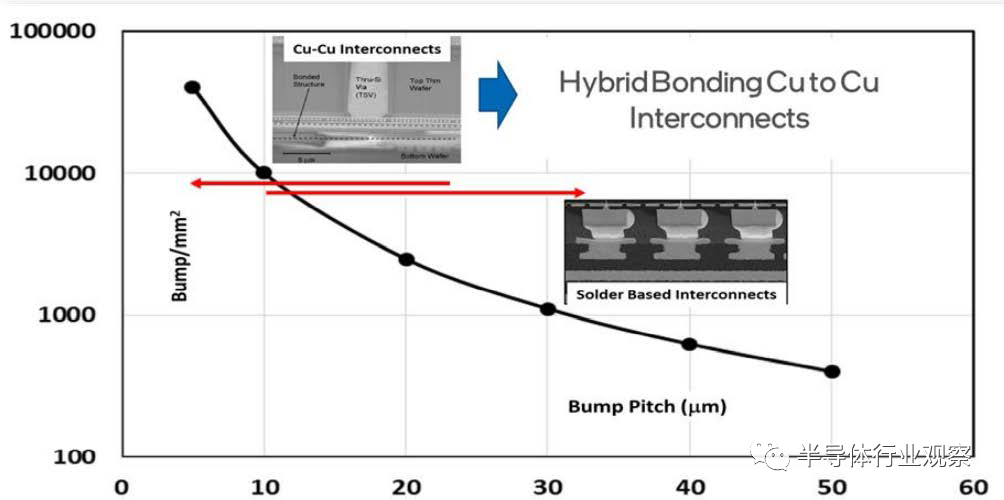

對於高性能計算(HPC)應用,行業領導者提出了一個可擴展到10000 IO/平方毫米的平台:

互連面密度=每平方毫米10000個凸塊或焊盤,需要10微米的凸塊或墊間距。如下圖(來源Intel)所示,這種密度將互連要求置於焊料和銅對銅互連之間的過渡區域。這一轉變將在組裝和基板技術方面帶來巨大挑戰。

對於基板技術,跡線寬度、銅厚度、相關的間距要求以及電介質材料和形成的盲孔焊盤直徑將影響面密度。

總之,未來高密度基板縮放有幾種選擇。在一條路徑中,通常在小芯片上的細間距凸點管芯將連接到具有≤2μm線和空間特徵的高密度有機基板上。雖然有人擔心目前的材料和工藝集可能不支持低於5μm線和空間的特性,但相關研究正在進行,開發新材料和工藝,以實現預期目標。另一種途徑是使用有機/無機再分配層(RDL)來路由所附接的細間距凸塊。模製或組裝的RDL結構將附着到密度較低的層壓基底上。還有可能使用的新材料替代品。

在任何一種方法上,都有必要關注製造科學和工程,以提高經濟性和先進的基板製造實踐。需要制定具體的運營目標,包括產量、良率和利用率,並與工業4.0(智能製造)計劃保持一致,以使美國在這一領域具有競爭力。

表****5:高密度基板技術評估。綠色:可用於製造的解決方案。黃色:需要額外的開發工作。紅色:HVM需要大量開發工作。

未來的系統,尤其是那些工作在100 GHz以上的系統[(1-3年)、110GHz-170GHz(D波段)、(3-5年)220-350GHz(G波段)]是支持實現能夠處理和傳輸更多數據的若干芯片的領先產品。用於製造RF封裝和模塊的先進基板技術比以往任何時候都更受小型化的驅動。

在不久的將來,將需要能夠嵌入多個無源元件和至少一個有源元件的技術。因此,下一代RF器件不僅需要具有小型化結構的先進IC基板技術,例如L/S小於15/15μm、節距尺寸小於20μm和焊盤尺寸小於30μm,而且還需要具有提高對準精度的組裝技術。

除此之外,導電跡線以及天線貼片將以超低的表面粗糙度製造。結合低Dk/Df材料的實施,這些痕跡可能會發生分層。因此,這些典型的層壓基片可能需要增粘劑以避免分層,同時仍然確保優異的性能。最後,在面板級別上製造此類系統(超過500 mm面板的數量級)需要基於模擬的工藝優化,以避免翹曲和可靠性問題。

封裝測試

先進的封裝和異構集成產生了多種封裝系統(SIP)/多芯片模塊(MCM)設計和應用的馬賽克。這種馬賽克的製造測試開發在許多方面都具有挑戰性:

在設計中使用現有芯片導致在SIP上作為整個系統的測試設計(DFT)集成並非做優化DFT測試插入通常是在單芯片設計的基礎上進行的SIP DFT整體非優化的缺陷導致自動化測試設備(ATE)中的儀器更昂貴、成本更高、測試時間更長(順序比與併發測試可能性)大量掃描測試模式卷,向SIP-ATE測試儀傳輸更大的數據量要求ATE測試儀具有更高的數字和非數字信道計數,以及模擬、RF、mmWave和光子學的特定選項。小間距插入器/芯片帶來挑戰和機遇。應對預期挑戰需要創新。以下方面需要行業範圍的標準和強有力的市場採納:

用於SIP的DFT和測試架構,具有製造快速測試時間,如啓用強大的併發測試架構和具有電源感知的診斷測試功能通過SIP配置自動掃描和算法測試模式生成、流式傳輸和採樣,將SIP本身視為未來的超級SIP內置自測試(BIST)具有功率感知節流功能的超級SIP-BIST引擎更強的DFT,針對SIP中的非數字內容(如模擬、RF、毫米波、光子學)的SIP視角進行了優化,或開發靈活的包裝器技術,以實現光/非DFT技術,或在經濟上不合理的技術。(帶有通用任意波形發生器(AWG)集羣、數字轉換器、射頻源/LO/捕獲/耦合器/混頻器、功率計、光子源/捕獲引擎、數據發生器/捕獲解調DSP、開關、開關矩陣、射頻開關等)標準化並重新使用某些ATE工業測試處理器,並將其集成到SIP作為測試引擎,以補充現有的BIST和DFT,從而減少對外部ATE測試儀的依賴開發緊湊型數字/模擬/射頻/光子源/捕獲和分析引擎IP核超級BIST系列作為微型ATE,用於SIP/有源插入器中的DFT基於標準化的新測試自動化端口技術,超級BIST引擎集羣內核集成具有強大的併發測試視角探索在主動插入器中實現上述包裝器技術減少引腳數DFT,實現更高的引腳數插入器可擴展性更精細的螺距探測技術子組件驗證/測試經濟性建模和仿真探索基於光子TAP(測試訪問端口)的新技術、DFT的有效協議和DFT的測試儀器體系結構的優點/缺點EDA行業領導者在SIP封裝設計和芯片設計市場採用這些標準的同時,也將模塊化、高通用性、重用率和較低的成本考量加入到ATE測試儀儀器和軟件產品中。

性能和工藝建模及模型驗證

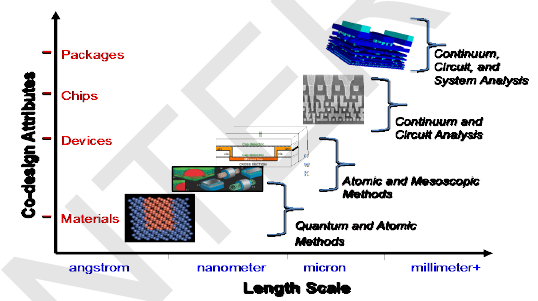

經過驗證的性能和工藝建模是加速微電子和先進封裝技術發展的關鍵。對複雜異構集成(HI)系統建模的一個重大挑戰是需要從埃到釐米跨越八個數量級的尺度,跨越材料/結構、器件、芯片和封裝等挑戰,如圖2所示,並且需要綜合考慮材料、電、光子、電磁、熱和機械行為。建模有幾個作用:(1)開發新材料和界面(2)在設計探索過程中進行粗略的性能評估(3)通過詳細評估對設計進行精確的行為評估(4)通過模擬輔助製造過程進行開發(5)通過缺陷預測提高製造過程產量。為了使模型發揮其預期作用,必須對其進行嚴格驗證。

通常,模型中的數據表示包括每個長度尺度中的物理和幾何屬性。比例之間的信息交換將包括材質、幾何屬性和模擬屬性。考慮到維度尺度由其自身的控制方程組成,尺度之間的接口對於提供獨立於基礎模型的模塊化平台是必要的。因此,模型抽象需要模塊化、靈活、材料和幾何獨立。機器學習(ML)模型可能是此類抽象的合適選擇。

建模中必須處理的特定元素的詳細信息如下:

**快速多物理、協同設計的多分辨率建模。**從原子到系統級的快速、大規模、耦合的多物理建模和分析是實現HI協同設計所必需的。不同長度尺度的多物理模型需要以不同的精度水平耦合,以支持不同的協同設計需求。需要融合機器智能和領域專業知識,以顯著加快設備、電路和系統級別的建模、分析和優化。

**跨設計層的分層不確定性量化(UQ)。**需要對過程變化下的複雜非均質系統的不確定性進行量化。由於許多相關的設計塊、高維不確定性源以及對不確定性統計行為的瞭解不足,此類模型非常具有挑戰性。

**芯片和封裝結構的高保真失效模型。**精準的多尺度行為模型對於準確估計處理條件的失效時間或存在能力是必要的。隨着硅通孔(TSV)和互連線被縮小到亞微米長度尺度,並且焊料凸塊被縮小到幾十微米,微結構將影響電遷移驅動的空隙以及疲勞斷裂。目前,這些失效機制的高保真模型尚不可用。

**材料和界面模型。**半導體技術的規模化導致了材料和結構之間的尺寸趨同,這反過來又導致了新的特性的出現。例如,電子、電氣、熱、機械和化學特性之間的複雜卷積。此外,縮放導致界面對材料至關重要。一般來説,需要建立材料和界面的模型,將尺度從量子尺度過渡到連續尺度。

**材料特性數據庫。**從器件級(FEOL、BEOL金屬和低k材料)、芯片級(3D互連和鍵合接口)到封裝級(焊料/底充料、模具化合物、再分佈層(RDL)、凸點、熱界面材料(TIM)和冷卻解決方案)的建模結構,需要開發一個準確的材料數據庫。還需要使用計算流體動力學(CFD)模型建立有效傳熱係數預測的經驗關聯。

表6列出了上述建模需求的當前狀態。

表6:建模需求

產品的可靠性是其在預期壽命內執行核心功能的能力。核心功能性能的降低以及輔助功能的損失將被視為可靠性的降低,而不是可靠性的損失。可靠性的損失和降低是由過度應力和/或磨損機制導致的設備、組件、子系統和系統故障造成的。當施加的載荷超過材料的臨界載荷/強度時,會發生過應力失效,而在重複或循環施加亞臨界載荷時,會出現磨損失效。過度應力失效機制通常是災難性的和突然的,如脆性開裂、脱粘、熔化和介電擊穿。磨損失效機制是通過累積損傷逐漸形成的,例如互連開裂、脱粘和電遷移。熱、機械、電氣、化學、輻射、磁性和濕度荷載既可以單獨作用,也可以相互聯合作用,從而導致過度應力和磨損失效機制。這些負載可能來自產品的內部工作、外部環境或操作條件。

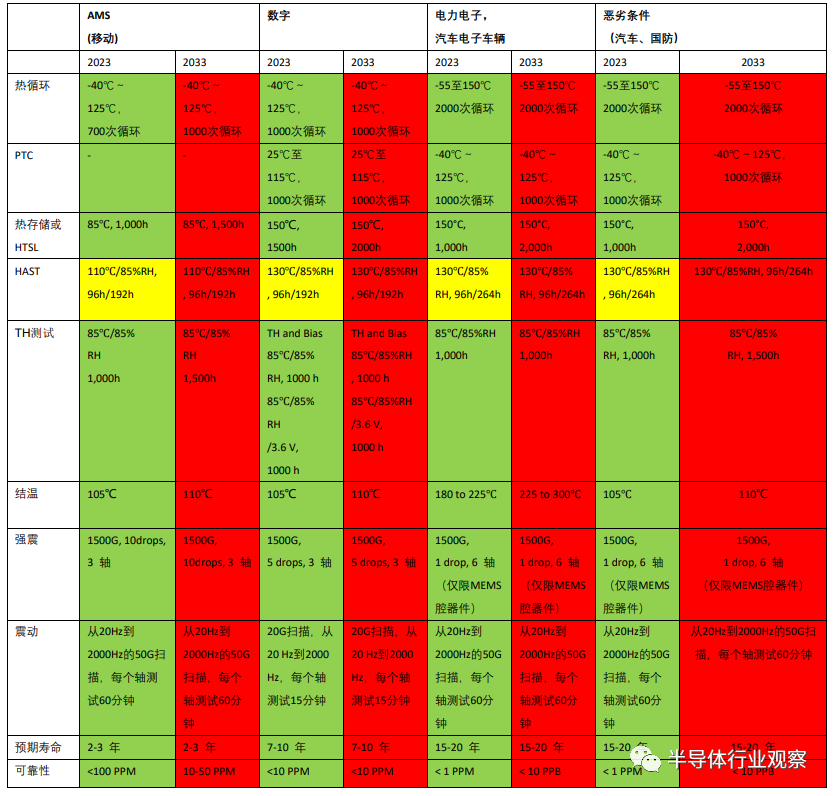

此類內部和外部條件的應用特定大小和持續時間對於評估可靠性至關重要。這種評估可以通過物理原型和測試或通過虛擬(模擬)原型和測試來執行。表7提供了特定於應用的可靠性鑑定指標。

可靠性鑑定指標應能夠創建類似的故障模式,如在不同應用的延長運行條件下發生的故障模式。儘管目前的許多標準都是基於過去的實踐和傳統,但隨着對潛在故障物理的理解以及基於真實現場性能的改進和智能數據分析,這些標準仍在不斷發展。因此,表7中的大多數標準在未來10年中似乎不會發生重大變化。然而,隨着新材料和工藝以及對功率、性能、成本和尺寸更嚴格要求,如果新材料、工藝和尺寸在設計過程中不考慮可靠性,則可能難以滿足相同的可靠性指標。因此,可靠性指標的未來列以紅色顯示。

表7:特定應用可靠性標準