EUV光刻,如何發展?_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。6小时前

編者按:

最近,IRDS陸陸續續發佈了最新的路線圖。所謂IRDS 成立於 2016 年,是半導體國際技術路線圖的繼承者。這些預測旨在協調學術界、製造商、設備供應商和國家研究實驗室之間的努力。

我們將光刻相關部分編譯如下,以饗讀者。

摘要

光刻和圖案化在未來將繼續發展,但面臨許多挑戰。預計2024年將推出High NA(數值孔徑)工具,但需要在光源、工具、掩模、材料、計算光刻和隨機控制方面進行改進,以實現這些工具的生產使用。工藝窗口預計會很小,需要使用更薄的抗蝕劑,並且還可能需要經過進一步改進的工藝集成方案。High NA工具的較小字段尺寸對於一些產品設計來説是困難的。這可能會刺激許多相對較小芯片的高性能封裝的增長。也在考慮採用更大的掩模尺寸來實現更大的曝光場的方法。抗蝕劑和相關材料需要改進,但即使有了改進,劑量也將繼續增加,以便能夠充分控制隨機效應。從長遠來看,可以開發出更高的NA EUV(“Hyper NA”),但這面臨着許多技術挑戰,可能不如0.33或0.55 NA EUV的多重圖案化有效。化學放大抗蝕劑至少在1納米邏輯節點之前仍將是主力抗蝕劑,但基於金屬的新品種抗蝕劑(濕沉積和幹沉積)也有着廣闊前景。隨着世界對環境問題日益關注,能源效率和化學品安全問題也日漸受到關注。

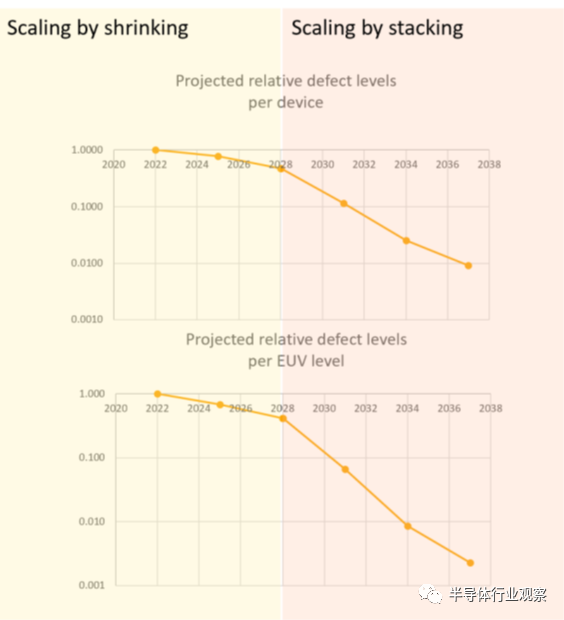

IRDS的總體路線圖預測,每個器件的芯片面積將比關鍵尺寸收縮得更快。這導致新的圖案化集成方案的使用增加,該方案可以減少邊緣放置誤差(EPE)並實現更緊湊的電路特徵。完全自對準的過孔和有源柵極上的自對準過孔是兩種可用的集成方案,它們將在未來的先進芯片產品中得到更多的使用。自對準材料在未來必須具備改進的介電常數,並且將需要使用諸如區域選擇性沉積之類的新技術。從長遠來看,從縮小器件尺寸到堆疊器件規模的預期轉變將導致關鍵級別數量的更快增長。它還需要將每個暴露水平的EUV缺陷率降低約一個數量級,這比每個節點的當前缺陷改進快很多倍。

概述

從歷史上看,光刻技術的改進一直是改進芯片技術的關鍵因素。國際器件和系統路線圖(IRDS)光刻路線圖預測了當前的圖案化能力如何支持未來的芯片,以及哪裏需要挑戰和改進。它給出了預期的關鍵光刻需求的路線圖,旨在供半導體行業參與者、行業分析師以及希望或需要了解該行業未來將如何發展以及需要解決哪些挑戰的研究人員使用。

本文件是對去年發佈的2022年光刻路線圖的2023年更新。基本表格與2022年相同。本次更新討論了2022年路線圖中提到的趨勢和挑戰在過去幾年中是如何演變的。此外,今年的光刻路線圖將其範圍擴大到包含圖案化技術,現在是光刻和圖案化路線圖。我們增加了一節討論模式的預計變化。該路線圖將在未來將繼續涵蓋光刻和圖案化。

路線圖的發展

該路線圖是通過與國際光刻和圖案化專家團隊協商並查閲公開文獻和其他可用文件而制定的。致謝中顯示了當前的貢獻成員。貢獻成員來自亞洲、歐洲和美國,代表半導體、設備和材料製造商以及研究機構。IRDS總體路線圖和More Moore團隊提供了從中得出光刻要求的器件路線圖。通過對IRDS光刻團隊成員的調查,制定了關鍵選項、時機和關鍵挑戰。表格和本文件在發佈前經過團隊和整體IRDS的內部審查。

光刻驅動器

該路線圖預測了未來的圖案化需求以及關鍵挑戰所在。在過去,邏輯器件和存儲器件都推動了圖案化技術的改進。目前,高性能邏輯器件正在引領更小的臨界尺寸,並推動新型圖案化技術的引入。新的DRAM器件繼續被引入,具有更小的臨界尺寸(CD),但需要以最小的分辨率跟蹤邏輯。閃存使用具有相對較大CD的3D結構進行縮放,並且不需要更高分辨率的圖案化來取得進展。

2022年以來光刻路線圖的趨勢

使用13.5nm波長的光進行成像的EUV光刻技術已被簡歷。先進的邏輯產品依賴於它,DRAM製造商已經開始大批量生產。已經清楚的是,EUV將不會取代多重圖案化。這兩種技術都將被使用,是否使用多重圖案化將取決於特定級別的細節、產量和成本。隨着邏輯尺寸的不斷縮小,可能會使用EUV雙圖案化。

正如我們下面所描述的,芯片尺寸和產量之間的權衡以及前沿邏輯的高成本意味着使用較小的芯片和高性能封裝可能會成為大芯片尺寸的替代方案。但是中介層和高性能封裝可能需要直接寫入光刻。這種需求刺激了大視場光學曝光工具和直接寫入工具的發展,包括光學和電子束。

EUV的挑戰

增強EUV是滿足路線圖需求的一個關鍵挑戰。EUV抗蝕劑將在下面關於圖案化材料的部分中進行討論。其他挑戰如下:

EUV光源與偏振控制

光源長期以來一直是EUV光刻的一個挑戰。用於光學光刻的波長是在窄帶寬上存在高強度光源的情況下選擇的。相反,實施EUV光刻的波長是基於具有高反射率的多層反射器的可用性。因此,開發具有足夠功率的可靠EUV光源以實現具有成本效益的掃描儀吞吐量,同時提供足夠高的劑量以避免由於光子發射噪聲引起的產量損失,一直是一個巨大挑戰。

然而,電漿光源(LPP)目前主要用於大批量生產(HVM)中的EUV光刻。在劑量控制的條件下,已經實現了600瓦的中等聚焦光功率,並努力將其提高到1千瓦。可靠性也在不斷提高。隨着輸出功率的增加,產生光所需的電量也會增加。減少用電量有幾種選擇,波長比目前在LPP光源中使用的CO2激光器產生的波長短的紅外激光器可以在將電轉換為紅外光和將紅外光轉換為EUV光方面提供更好的效率。

或者,在可預見的未來,自由電子激光器(FEL)將提供根據光刻的要求縮放功率和波長的能力。適合在大批量製造中使用的FEL光刻光源必須通過同時為多個工具供電或縮放加速器尺寸來滿足“每光子成本”(包括操作費用和環境影響)的要求。FEL可以提供偏振光,這可能是實現Hyper NA光刻所需要的。需要解決方案來降低由自由電子激光產生的光的高相干性,其中偏振和相干性對於單獨的曝光工具是可自由調節的。對於單個FEL為多個曝光工具供電的實施方式,需要處理高總光束功率的方法。此外,光源的可用性必須接近100%,並且任何中斷都必須能夠快速恢復。

High NA EUV的關鍵挑戰

長期以來,隨着數值孔徑的增加,光刻技術得到了擴展,ASML目前正在製造High NA EUV光刻工具原型(卡爾蔡司製造的0.55 NA光學器件),並將於2024年供芯片製造商早期使用。由於掩模上的多層具有高反射率的角度範圍有限,掃描方向上的透鏡縮小量增加到8倍,同時在垂直方向上保持4倍的縮小量。這導致晶片上的最大曝光場尺寸為26mm×16.5mm,是當前掃描儀場尺寸的一半,只要保持當前掩模尺寸即可。這對製造大面積芯片以及掃描儀吞吐量都有影響。製作大型裸片的一種解決方案是接合兩個單獨的曝光,儘管這種方法帶來了許多技術挑戰,其中一些是EUV光刻獨有的。此外,還提出了可以在晶片上支持26 mm×33 mm的更大掩模,掃描方向上的長度必須增加兩倍。目前正在考慮12英寸x 6英寸的掩模。製造這種掩模需要進行工作量相當大的開發與重組,但不需要對掩模製作技術進行根本性的改變。

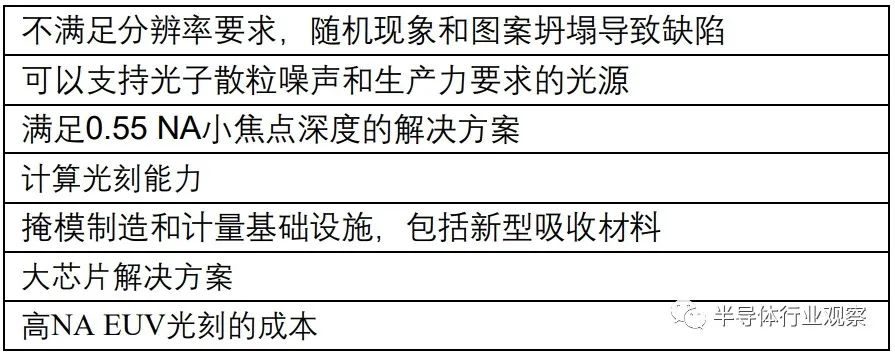

下表總結了High NA EUV光刻的其他挑戰(不包括與構建複雜光學器件和曝光工具相關的挑戰)。其中一些挑戰已經在NA=0.33的EUV光刻中得到解決,但需要擴展以在更高的NA下使用。現有的問題仍然是挑戰,部分原因是對邊緣放置誤差的更嚴格要求。許多關鍵挑戰是相互關聯的。例如,計算光刻由於聚焦深度的減少、需要包括抗蝕劑隨機性作為工藝變化的一部分以及(潛在的)多個掩模吸收體來解決掩模3D效應而變得複雜。隨機性的關鍵挑戰將在下一節中討論。

表-1 High NA(0.55)EUV光刻的主要挑戰

改變到更短的波長將是比增加的NA更大的變化,並且更具挑戰性,較短波長的光刻將比=13.5nm的Hyper NA具有更大的聚焦深度。短波長光刻需要新的光源、多層塗層和光刻膠。在較短波長下保持相同水平的光子散粒噪聲將需要輸送到晶片的光能加倍,這將大大增加投影光學器件中掩模和反射鏡的加熱。

隨機性

隨機性是指隨機因素導致印刷特徵隨實例隨機變化。例如,即使掩模特徵具有相同的尺寸,成像劑量的隨機變化也會導致打印不同尺寸的接觸孔。隨機性源於成像和圖案化過程中的隨機變化。它們可能導致較差的圖案質量,例如線寬粗糙度或較差的CD均勻性,並且它們可能導致實際的圖案缺陷。隨機效應隨着特徵尺寸的縮小而變得更糟,管理隨機效應是EUV光刻的挑戰之一。在2022年的路線圖中,我們預計打印劑量必須在四個節點中增加約3倍,以解決隨機問題,並使打印的EUV特徵能夠滿足關鍵的尺寸一致性要求。隨機效應隨着抗蝕劑膜變薄而變得更顯著,並且如果抗蝕劑薄膜吸收更少的光則更糟。由於抗蝕劑膜必須變得更薄以適應EUV High NA投影的小聚焦深度,這將迫使抗蝕劑吸收率增加。

EUV計算光刻能力

考慮到先進EUV能力(High [email protected]和Hyper [email protected]),掩模、投影光學器件和照明的協同優化比以往任何時候都更加重要和具有挑戰性。如下所述,不僅將使用先進的光學鄰近校正(OPC),而且需要曲線掩模。正常的趨勢是,由於更小的特徵尺寸和更復雜的輔助特徵,每次生成掩模都需要更多的數據,但曲線特徵的出現和反向光刻技術(ILT)的使用有可能將掩模數據量增加十倍以上。這將給計算光刻路徑和掩模數據處理和製作流程的每個元素帶來壓力。它將刺激人工智能等新方法,或更多地使用圖形協處理器等專用芯片來加快計算速度,並採用新的掩碼數據格式,如multigon,作為傳統P39 oasis標準的擴展。

EUV 掩模

對更復雜和曲線圖案的需求導致了掩模製造中的長寫入時間。多波束掩模寫入器已經投入使用多年,有助於解決這個問題。另一方面,用於評估圖案化掩模的轉移特性的測量技術仍然存在許多問題,包括其成本效率,並且還存在對亮場掩模、亞分辨率輔助特徵和缺陷控制的擔憂。此外,EUVL具有足夠透射率和長壽命的薄膜的實際應用也是一個問題。對於EUVL的High NA時代,由於將使用變形光學系統,掩模縮小在一個方向上變化,並且圖案有效面積有限,因此有必要考慮增加掩模尺寸和/或縫合多個掩模以打印大的裸片尺寸。此外,還需要開發新的掩模吸收材料和工藝,以減少掩模3D效應,並在晶片上獲得更高的圖案分辨率和保真度。

能源效率

能源使用和其他資源消耗越來越受到世界各國的關注。半導體制造消耗大量能源,在某些情況下是一個國家總功耗的可測量部分。IRDS ESH&S團隊正在評估晶圓廠的能源和水消耗以及對環境的影響,並推斷未來的使用情況,以確定哪裏可以減少消耗。現在的另一個問題是,器件密度和芯片性能的提高是否超過了晶圓廠使用的能源、水和其他資源。

光刻是僅次於設施要求的第二大耗電來源。EUV光刻的使用正在增長,並且可能是能源的主要消耗者。光刻和圖案化團隊正在與ESH團隊合作,以瞭解EUV使用量增加對功耗的總體影響。評估是複雜的,因為即使增加EUV的使用也會增加能耗,用EUV單次曝光代替多次圖案化往往會降低圖案化水平,這可以降低能耗。

光刻能源小組正在努力開發一種方法,該方法考慮了使用這些工具的吞吐量和能耗的完整光刻過程中使用的設備的各種功率要求,以及基於各種節點的工藝流程產生的成品器件。

目前的情況是,能源子集團有較簡單節點的工藝流程,並已根據已確定的工藝流程和典型設備功率要求制定了計算每個節點的Litho功耗的方法。整個過程的下一步包括獲得詳細的設備型號(以獲得特定的能耗)以及產量。

團隊正在努力研究多級光學曝光工藝流程以與單掩模EUV工藝流程進行比較。由於光學掩模和EUV掩模之間的製造工藝差異,這增加了複雜性。

計劃在2024年路線圖的完整更新中報告模型的狀態和這些調查的結果。

封裝與光刻

高級封裝在以下幾個方面與圖案化相關:

圖案直接用於封裝過程使用先進的封裝可以減少光刻對系統成本的總體影響先進的封裝可以潛在地用於解決由High NA EUV系統的現場尺寸引起的問題先進的封裝還提供了器件堆疊的替代方案以及由此產生的嚴格缺陷密度要求

先進的封裝已經通過分解來減少光刻對系統成本的影響。在這種方法中,可以使用非常先進的光刻技術來收縮電路的部件,例如邏輯單元和存儲器,與電路的其他部件(例如輸入/輸出)分開製造,這些部件可以使用便宜得多的圖案化技術來生產。然後,通過先進的封裝將電路的單獨製造部分(有時稱為芯粒)集成在一起。使用這種方法,可以凸顯使用先進光刻技術進行縮放的好處。先進封裝的成本與製造芯粒而不是更大芯片所節省的成本之間存在權衡。High NA EUV的使用,其中由於較小的曝光場而更難製造大芯片,可能會將這種折衷更多地推向將較小芯片與高性能封裝一起使用的方向。

高級封裝需要基板,可以並排放置幾個芯片,並且包含互連線和芯片連接位置。使用圖案化技術可以創建連接模式。封裝基板可能具有相當大的翹曲,達到100微米或更大,帶來對夾持和聚焦的光刻挑戰。可能涉及大型封裝和襯底,需要大型場曝光工具或直接寫入系統。例如,LGA 6096封裝的側面面積大於70mm。用於封裝的常見基板尺寸為510 x 515 mm,甚至可以支持大型封裝。無論是大型曝光工具還是直接寫入系統,都存在巨大的工程挑戰,特別是當高級封裝中的功能遠遠縮小到一微米以下時,就需要能夠產生非常高縱橫比結構的蝕刻工藝,例如硅過孔。

圖案化材料與集成

圖案化集成路線圖是由減少可變性並仍然支持電氣性能的需求驅動的。可變性的一個主要優點是邊緣放置誤差(EPE)。EPE定義為考慮局部變異性(LER/LWR、LCDU)和全局變異性(疊加)的術語總和。本節分為兩個主要部分:

圖案化材料:專門定義的抗蝕平台和輔助材料,以減輕EPE的局部可變性成分模式集成:定義集成方案和所需材料,以減輕EPE的全局可變性成分

圖案化材料

圖案化材料仍然是擴展縮放的一個關鍵挑戰。隨着抗蝕劑的連續顯影,底層和圖案化堆疊的共同優化對於提高圖案化性能是必要的。化學放大抗蝕劑(CAR)仍將是1-nm節點的主力,關鍵器件和金屬級別都有單一和雙重圖案化選項。CAR在材料隨機性方面有了顯著的改進。它們是用較小的構建塊設計的,具有減少其多個組件分佈可變性的策略。對它們的化學性質進行了詳細研究,以通過最大限度地增加與吸收光子的有用化學相互作用的數量來提高量子產率。旋塗和沉積的下層都被調整以優化抗蝕劑下層相對於隨機缺陷和圖案轉移的相互作用。CAR向底層硬掩模的圖案轉移是另一個活躍的發展領域。新的descum化學、化學選擇性沉積策略、基於原子層的蝕刻技術在減輕光刻中形成的隨機缺陷方面被證明是有效的。

高級硬掩模(HM)材料也被提出,其固有特性被設計用於減輕圖案保真度損失(即,蝕刻後LER和尺寸損失)。特別重要的是用於低k ILD蝕刻的HM材料,其中器件中的最小節距被圖案化。隨着間距接近20nm分辨率,等離子體氣相沉積(PVD)TiN似乎正在接近其能力極限,人們正在探索一種新的概念,即無Ti選項或等離子體增強原子層沉積(PEALD)TiN,它使膜性能具有更大的可調性,從而通過應力和結晶度控制來減輕LER。

儘管這些材料的進步加上成像的改進,CAR仍將面臨2-1.5 nm節點的挑戰。一些報告顯示,CAR抗蝕劑沒有跟上用於線和空間的金屬氧化物抗蝕劑(MOR)的進展,儘管它們保持了接觸孔性能,並且在MOR工藝開發方面取得了實質性進展。NXE:3400掃描儀上最近的單次曝光極限數據表明,CAR在亞28 nm間距分辨率下可能具有更高的缺陷和低靈敏度。亞28nm節距尺度的縱橫比將需要減薄抗蝕劑厚度,這將對粗糙度和斷線缺陷產生負面影響。抗蝕劑供應商已經在通過新興的抗蝕劑設計來應對這些挑戰。簡化抗蝕劑化學以限制隨機性、結合的光化學成分和替代顯影劑可能是使CAR在更高分辨率下具有競爭力的方法。儘管CAR顯影工藝的主流是使用TMAH顯影劑的正色調濕式顯影(PTD),但使用新引入的疏水顯影劑——負色調濕式顯影劑在分辨率和粗糙度方面都有所改善。

金屬氧化物抗蝕劑具有可以轉化為更高靈敏度的高光子吸收,是CAR的最大競爭對手。這些新材料預計在1.5nm及以上的節點中使用。雖然可以預見0.33 NA雙圖案化的一些潛在應用,但MOR的微分器將具有High NA 0.55 EUV插入。憑藉更高的分辨率能力,MOR有望解析二維結構,這將實現單次曝光並減少所需的EUV掩模數量。MOR平台有望不斷改進,量子產率不斷提高,以在不影響劑量的情況下改善粗糙度和缺陷率。基於軌道的邊緣焊道去除和背面/斜面清潔選項已成為解決金屬污染的標準流程,並將繼續發展。作為一類新的抗蝕劑,瞭解環境和工藝延遲對其穩定性的影響仍然是MOR的一個重要關注點。對於High NA光刻,需要縫合以適應後續曝光中打印的單個裸片,CD穩定性控制至關重要。MOR正在考慮採用抗蝕劑塗層、曝光和顯影步驟的新型工藝流程。描述這些新方法的效果及其對抗蝕劑性能的影響是近期行業關注的焦點。

MOR同時考慮濕法和幹法開發。雖然濕法開發利用了CAR現有的生態系統,但需要新的硬件改進來優化MOR的性能。乾式沉積和乾式顯影的抗蝕劑都是該行業的新候選者。最近,一種新的基於塗布機/顯影劑的顯影方法被引入MOR顯影,以改善分辨率、粗糙度、靈敏度、圖案塌陷和缺陷率。乾式顯影的優點在於能夠實現更高的縱橫比而不發生圖案塌陷。MOR底層和圖案轉移技術的調整也是一個重要的發展領域,可以提高其性能。

定向自組裝技術正在被評估或用於邏輯、存儲器和CMOS傳感器的器件製造。DSA成本合理,用於從粗略的初始圖案製作重複的平滑細間距圖案。

圖案重塑技術已經宣佈,未來可能用於針對特定類型或佈局上的小型亞分辨率特徵;儘管有益並且支持降低光刻成本之類的重要需求,但是就材料和顯影技術能力而言,它們仍無法改善現狀。

另一個迫在眉睫的挑戰是可能對含氟化學品進行更嚴格的監管,包括可能禁止其使用。一些光刻材料含有氟,並且沒有可用的替代品。請參閲IRDS ESH&S路線圖瞭解更多詳細信息。

圖案化集成

隨着器件中的最小間距逐漸保持縮放,EPE的裕度變得更小,導致圖案化空間中的額外複雜性增加。

每個EPE組件都有自己的路線圖,以確保每個技術節點都有足夠的EPE預算。已經發表的數值模擬估計了EPE最敏感的工藝參數,覆蓋佔預算的40%,LER佔預算的25%。

為了增強覆蓋的過程窗口,從而減輕EPE,已經提出了幾種自對準技術,利用特定的新過程集成方案。關鍵原理是利用多色蝕刻對比度以及先進的蝕刻系統來提高選擇性,以降低最終尺寸和放置對實際錯位的敏感性。這些技術被稱為設計技術協同優化(DTCO)或縮放助推器。有史以來採用的第一種DTCO技術是利用ABACA彩色方案的自對準塊(SAB)。

DTCO is also important for enabling the correct node-to-node die area scaling, as minimumDTCO對於實現正確的節點到節點管芯面積縮放也很重要,因為最小間距接近20nm及以下。具體而言,採用DTCO和自對準技術來實現新的佈局策略,旨在提供更緊湊的器件設計,從而實現比臨界尺寸縮放更快的管芯面積縮放,並避免不可接受的RC延遲增加。

我們將圖案化集成定義為專門為實現先進DTCO技術而開發的圖案化技術和材料路線圖的分支。在目前正在醖釀的許多選項中(超級過孔、半暗面、完全自對準接觸…),下面討論了與即將到來的節點中的圖案化集成最相關的兩個選項,以及材料特性的路線圖:

1.完全自對準過孔(FSAV)

2.有源門上的自對準觸點(SAC用於COAG)

完全自對準過孔

FSAV技術包括創建ABAB多色圖案化方案,其中“A”是底層金屬,“B”是用於自對準蝕刻的額外電介質永久材料;這使得能夠在光刻級別打印更大的過孔,具有增強的覆蓋預算,並且還將在過孔和相鄰的未連接金屬線之間創建更長的泄漏路徑,從而提高器件可靠性。

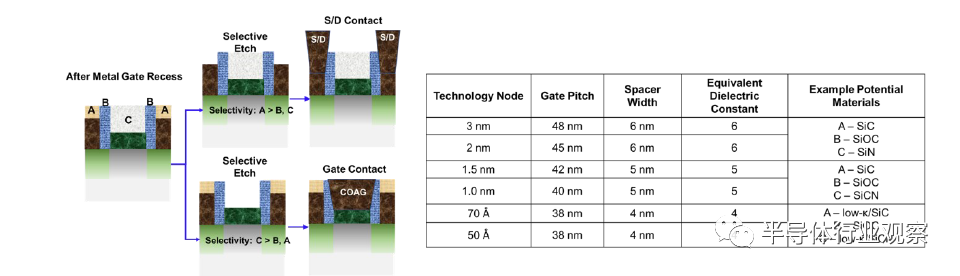

圖1報告了傳統流程(控制流程)與FSAV流程的工藝流程圖,自對準材料報告為深藍色;它還報告了在恆定節點間RC延遲的假設下估計的所選間距的自對準材料的估計特性。

已經證明,FSAV方案與控制流相比可以顯著增加覆蓋預算,這將是實現2 nm節點以外路線圖的關鍵技術。

自對準材料介電常數必須與間距一起縮放,以避免與FSAV方案相關的過高RC影響。用於高蝕刻選擇性的最佳材料通常具有高介電常數。

自對準材料是通過區域選擇性原子層沉積(ASD)沉積的,這是一種新興技術,利用相鄰材料之間的表面能差在一個材料上沉積,而不是在另一個上沉積。在特定情況下,需要介質上電介質(DoD)ASD。FSAV預計需要從間距20nm開始。

有源柵極上的自對準接觸(用於COAG的SAC)

COAG使單元能夠實現更有效的接觸和設計佈局,柵極接觸不需要虛設柵極,以最大限度地降低與源極和漏極接觸短路的風險。該概念基於多色選擇性方案,如圖2所示。

必須創建ABCBA圖案,其中“A”是覆蓋源極/漏極(S/D)接觸的材料,“B”是低k間隔物,“C”是電介質柵極帽。間隔物寬度(B)定義了採用自對準方案的需要,閾值暫定為6nm。為了形成兩個不同的接觸族(在柵極和源極/漏極上,在通用術語中分別為VCG和VCT),需要兩個專用掩模和曝光步驟,每個步驟之後都是選擇性地打開A或B的蝕刻步驟。

自對準A和C材料在器件中是永久性的,因為它們只在必須建立接觸的地方被去除,所以它們必須像CPP一樣縮放其介電常數,以最大限度地減少它們對RC延遲的影響。圖2中的表格報告了在節點間恆定RC係數假設下定義的路線圖,以及滿足要求的一些材料示例。

多色圖案化方案可以通過凹陷S/D和柵極材料,然後在間隙中沉積並平坦化,或者通過金屬上電介質(DoM)ASD來生成。雖然Recession+Gapfill方法利用了傳統技術,但它會導致在幾個工藝步驟中需要處理的縱橫比增加。區域選擇性沉積有望成為未來COAG SAC以及將開發和實施的所有其他DTCO技術的有力推動者。

長期挑戰(2028及以後)

從長遠來看,IRDS路線圖預計,邏輯設備將轉向通過堆疊進行擴展,而不是通過收縮進行擴展。這將大大增加EUV級別的數量。由於EUV水平是關鍵水平,因此可以預測,在工藝升温後,它們將產生大部分光刻缺陷。取每個節點所需的缺陷密度,並計算每個關鍵級別所需的故障密度以滿足該目標,可以逐級別投影所需故障密度。如圖3所示,使用多層器件時,缺陷密度需要降低幾個數量級才能保持良率。該圖表假設2022年的缺陷密度剛好滿足要求,並且2022年缺陷密度被歸一化為1。如果不能實現缺陷密度的快速降低,那麼轉移到更小的管芯尺寸並使用先進的封裝來集成更小的芯片可能是提高產量的途徑。

結論

0.33 NA的EUV現在已經確立。EUV的擴展正在開發中,更高的NA工具預計將於2024年開始提供。採用High NA EUV存在許多挑戰,包括小工藝窗口、掩模製作、隨機效應和缺陷。High NA將帶來更小的曝光場尺寸。這可能會刺激先進封裝和/或更大掩模尺寸的增長。與電路面積縮放相比,CD縮放的放緩需要實現先進的DTCO,以比CD收縮更大地減小電路尺寸。必須改進材料以支持新的工藝節點。不僅抗蝕劑必須改進,而且底層、圖案質量改進工藝(如基於DSA的工藝)和圖案轉移工藝也需要改進。前沿抗蝕劑技術主要基於化學放大材料,但基於金屬的抗蝕劑和一些幹沉積抗蝕劑在能夠在低膜厚度下工作和工藝集成方案方面都顯示出前景。諸如完全自對準過孔和有源柵極上的自對準接觸的技術將是實現這一點的關鍵。從長遠來看,從尺寸縮放轉換為堆疊縮放需要更快地改善EUV缺陷率。每個EUV水平的缺陷率將需要每個節點大約降低一個數量級,而不是每個節點降低20%或更少。