圖像傳感器的堆疊與互聯_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。3小时前

摘要:過去二十年來,圖像傳感器的發展取得了許多技術突破。圖像傳感器已發展成為支持許多應用的技術平台。它們在移動設備中的成功實施加速了市場需求,並建立了一個業務平台,以推動持續創新和性能改進,並將其擴展到監控、醫療和汽車行業。

在本文中,我們簡要介紹了通用相機模塊以及芯片堆疊架構和先進互連技術的關鍵技術要素。這項研究還將研究像素電子器件在確定芯片堆疊架構和互連技術選擇方面的作用。它通過檢查一些用於不同功能的 CMOS 圖像傳感器 (CIS) 示例來進行,例如可見光檢測、用於低光檢測的單光子雪崩光電二極管 (SPAD)、捲簾快門(rolling shutter)和全局快門(global shutter)以及深度感測和光檢測以及測距(激光雷達)。

文章還介紹了不同芯片堆疊架構的性能屬性。直接鍵合、後通孔硅通孔(Via-last TSV)和混合鍵合(HB)技術被認為是圖像傳感器芯片堆疊中較新且有利的芯片間互連技術。最先進的超高密度互連可製造性也得到了強調。

以下為文章正文:

自2000年初以來,CMOS 圖像傳感器已被許多行業廣泛採用。其多功能應用擴展到數碼相機、移動設備、監控系統、機器人、醫療器械和自動駕駛汽車等許多行業。通過使用像素陣列中的光電二極管捕獲圖像並將信號實時轉換為數字文件的能力可以實現高級數據管理和分析,從而實現其硬件與計算系統的兼容性。最近的進步使分析功能更接近像素陣列。機器學習 (ML)、人工智能 (AI) 算法和圖像傳感器內的圖像重建技術的實施已被廣泛報道 。因此,圖像傳感器技術平台是許多應用的關鍵部分。

雷達和圖像傳感器的傳感器融合、用於高級駕駛員輔助系統的光檢測和測距 (LiDAR)、神經形態和高光譜成像、熱成像和生物醫學應用等先進應用正在不斷發展。2018-2019年,圖像傳感器的市場規模已達到約200億美元。預計從 2019 年到 2025 年,僅三維 (3D) 成像和傳感市場的擴張將達到50億至150億美元,這幾年的CGAR 為 20%。主要行業是消費移動產品和汽車行業。

技術平台和業務平台之間的協同效應已經顯現。為了滿足移動設備的外形尺寸限制,我們為具有巨大消費者需求的移動設備應用開發了先進的技術平台。移動設備建立的規模經濟進一步鼓勵先進的像素電子設計和使用芯片堆疊方法的像素並行處理在其他行業的應用。圖像傳感器將繼續成為與業務平台協同的產品開發的強大技術平台。

像素電子產品的創新實現了多種先進功能。2000 年初,已有許多複雜圖像傳感器的設計被報道。只有當芯片堆疊和先進互連技術變得可製造時,這些創新的商業化才有可能實現。3D集成圖像傳感器的示範性設計始於1999年的四層堆疊,以及2004年多芯片堆疊架構中的多功能傳感器。新實施的支持技術和特徵尺寸的減小改變了擬議的 3D 集成。一些重大突破,如2009年的背照式(BSI) CIS、2012年的芯片堆疊、2015年的“pixel-DRAM-logic ”三芯片堆疊、2016年的銅-銅混合鍵合(Cu-Cu hybrid bonding),這些技術都帶來了最先進的技術平台。

圖像傳感器和攝像頭模塊

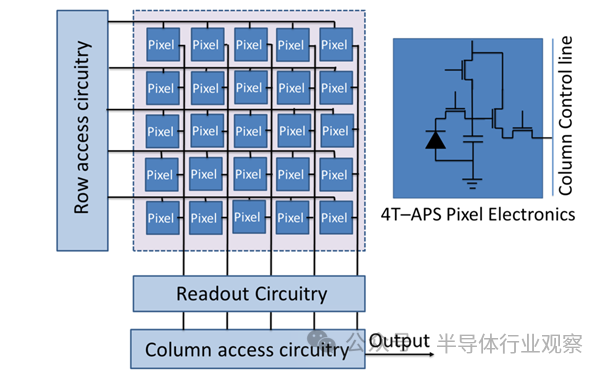

圖像傳感器是一種光電器件,通過光電二極管收集光源發出的光子,並將光電二極管產生的電流轉換成數字信號。四晶體管有源光電二極管傳感器 (4T-APS) 像素的典型像素電子器件由光電二極管和像素級電子器件組成,如圖1右側所示。圖像由像素陣列形成,其原理圖如圖1中的方框區域所示。然後通過讀出電路逐行評估像素陣列中的信號以進行進一步處理。行和列訪問電路可以是用於掃描模式訪問的開關陣列或用於隨機像素訪問的解碼器。

如今,圖像傳感器包含更多功能,用於讀出功能後的信號處理和分析。通用操作電路可以包括用於高級應用的讀出功能、模數轉換、圖像重馬賽克處理或人工智能分析的電路。通過使用不同的感光材料,在不同的環境下,光檢測的波長也可以從可見光到近紅外或紅外。對不同應用的巨大需求引發了這些領域的重大進展,不僅是研究和開發,而是將其商業化。

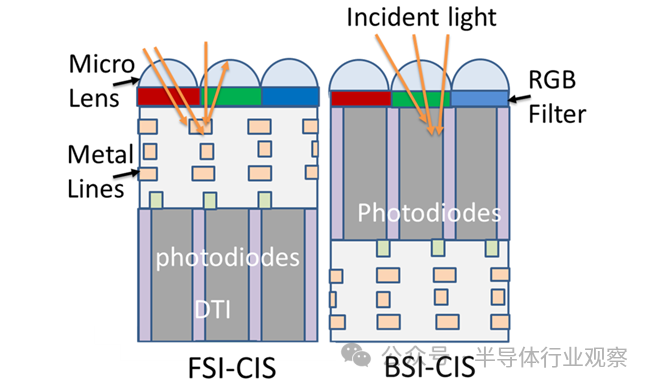

像素電子器件通常根據目標應用的光電二極管模式而變化。像素電子器件的範圍可以從三晶體管3 T-APS 到 84 晶體管。像素電子器件和操作電路是影響芯片堆疊和互連方法選擇的主要因素。基於不同照明方法的傳感器也會影響芯片堆疊和互連架構的選擇。由於金屬互連線的遮光,前側照明(FSI)CIS在像素尺寸低於1.4μm×1.4μm時大部分被BSI-CIS取代,如圖2所示。

像素設計可能會有所不同,圖2僅用於解釋金屬線屏蔽入射光的效果。例如,深溝槽隔離 (DTI:Deep trench isolation) 不需要 FSI-CIS 具有大像素尺寸。用於可見光檢測的圖像傳感器通常稱為 RGB(紅、綠、藍)圖像傳感器,具有簡單的 3 T-APS 或 4 T-APS,當解碼器就位時還帶有附加晶體管。通常需要紅外 (IR) 濾光片(有時稱為紅外截止濾光片)來屏蔽超出可見光範圍的波長,以減少穿透硅光電二極管薄層的近紅外 (NIR) 光的干擾。微透鏡層位於 RGB 濾光片的頂部,可增強投射到光電二極管區域的光。

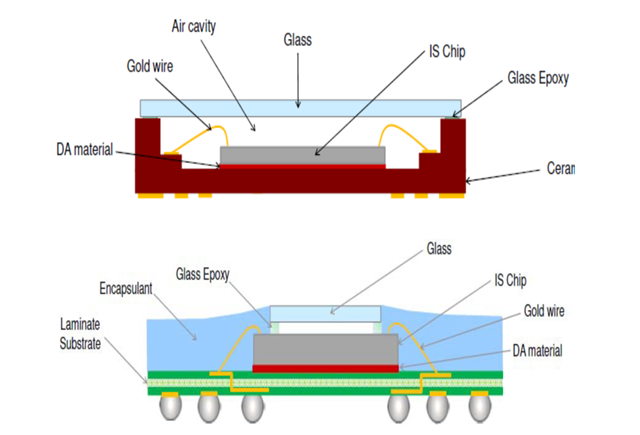

封裝圖像傳感器的方法有很多種。兩種常用的圖像傳感器封裝是陶瓷無引線芯片載體和成像球柵陣列,原理圖如圖3所示。在新的多功能應用的推動下,新的圖像傳感器封裝方法的開發仍在繼續。探索了曲面圖像傳感器封裝和超薄芯片級封裝等先進應用。

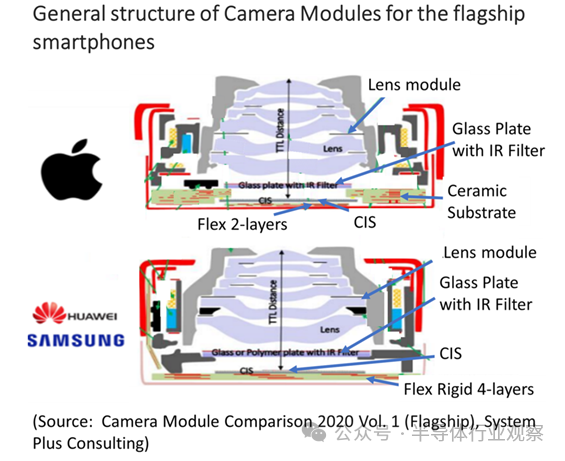

相機模塊在頂部承載鏡頭模塊,在底部承載圖像傳感器封裝。System Plus Consulting分析的智能手機攝像頭模塊如圖4所示。

頂部相機模塊顯示具有陶瓷基板的 CIS 封裝,而底部模塊則顯示具有柔性剛性(flex-rigid)基板的 CIS 封裝。精確安裝圖像傳感器封裝和相機鏡頭模塊對於確保光投射對準至關重要。鏡頭模塊的高度和圖像傳感器封裝的尺寸是相互關聯的並且被限制在相機模塊內。隨着智能手機的厚度越來越薄,相機模組的總高度受到限制。因此,相機模塊的寬度和圖像傳感器的尺寸都被限制在狹小的物理空間中。

用於移動應用的圖像傳感器

外形尺寸一直是將數碼相機集成到智能手機和平板電腦中的關鍵因素。圖像傳感器的研究和開發旨在將相機模塊安裝在這些移動設備的狹小空間中,以實現多種應用。同時,分辨率的提高需要高像素密度、小像素尺寸以及高量子效率和高填充因子的光電二極管設計。本節中,我們總結了圖像傳感器的一些案例研究,並考慮了應用、所需的像素電子器件以及與 3D 集成相關的芯片堆疊和互連技術。當前工作的目的並不是關注圖像傳感器的性能。

一、堆疊式 RGB 背面照明 CMOS 圖像傳感器。

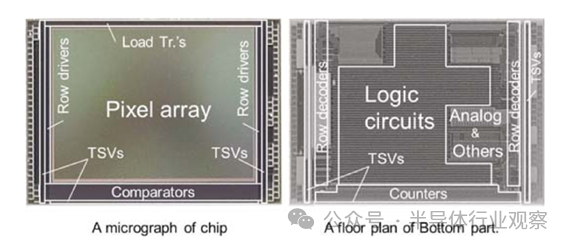

索尼公司於2012年8月20日發佈了世界上第一個商業化的堆疊式圖像傳感器。圖像傳感器的性能在很多方面都得到了改進,例如更小的像素、更高的像素密度以及通過信號處理和圖像重建來提高圖像質量。Remosaic 算法通過分配具有長和短曝光時間的像素來提高質量,以幫助增加明亮和黑暗環境下成像的動態範圍。複雜的操作電路導致芯片尺寸增加,這促使需要對芯片堆疊進行 3D 集成以保持較小的外形尺寸。像素陣列和邏輯處理電路被分成兩個單獨的芯片,如圖5所示。堆疊式圖像傳感器不是基板上的單芯片圖像傳感器,而是將像素陣列芯片堆疊在邏輯電路芯片的頂部。

操作電路與像素陣列的電連接由用於芯片到芯片互連的外圍後通孔TSV陣列形成,如圖1和2所示。這些 TSV 在行驅動器到解碼器(driver-to-decoder)和列比較器(comparator)處連接到外圍區域的計數器。TSV互連的數量與像素陣列的行和列訪問的數量密切匹配,如圖1所示。在這個 8 MP 圖像傳感器示例中,設計了數千個 TSV。芯片在電介質對電介質表面面對面粘合在一起,然後從 BSI 像素陣列芯片的背面形成最後通孔 TSV,落在兩個芯片的金屬焊盤上。重新分佈層橋接最後通孔 TSV 以形成芯片到芯片互連。芯片堆疊和外圍後通孔 TSV 的截面示意圖如圖6所示。像素尺寸為1.12μm×1.12μm。TSV 的直徑 約為2.5μm,間距為6.3μm。像素芯片減薄至約8至9μm,硅基板厚度約 3至5μm。像素陣列芯片和處理芯片分別採用90納米和65納米技術加工。這使得尺寸僅為傳統單芯片圖像傳感器的 70%,該設計的熱管理經過測試並發現是足夠的。

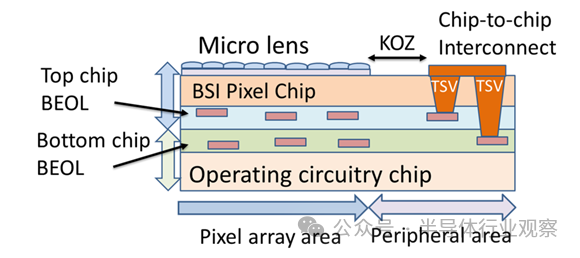

索尼通過從後通孔 TSV 轉向外圍芯片間互連的混合鍵合,進一步減小了芯片尺寸並簡化了工藝。2016年的一份研究報告指出,研究人員正在研究在像素陣列下方以4μm間距放置混合鍵合 ,以進一步減小芯片尺寸。這一變化還消除了KOZ (Keep Out Zone) 和 TSV 蝕刻的附加處理設備而導致的器件設計規範。該圖像傳感器於 2016 年在 iPhone 6S 中推出。它是1.4μm像素尺寸、12MP BSI-CIS 圖像傳感器。混合鍵和間距分別為6μm和 14 μm。估計的混合鍵密度約為5000 bonds/mm2。

二、雙光電二極管堆疊 RGB 背面照明 CMOS 圖像傳感器。

芯片堆疊可以提高性能並在兩個單獨的芯片中使用不同的處理技術。可以在不犧牲芯片尺寸的情況下將單獨的優化和附加功能特徵添加到操作電路芯片中。

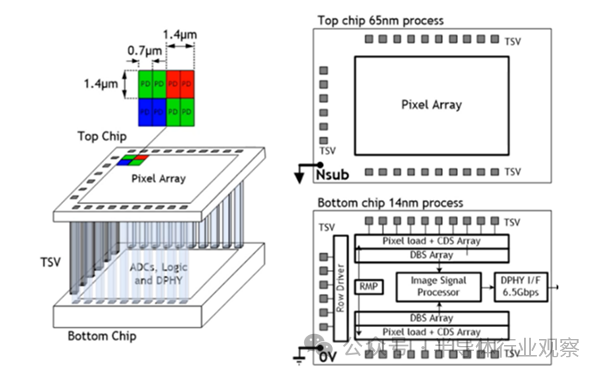

三星採用芯片堆疊技術用於超過 16 MP 的 BSI-CIS 。其 108 MP BSI-CIS 已於 2019 年在智能手機中實現,當中像素陣列芯片使用65 nm 工藝,邏輯芯片使用28 nm 的技術。三星最近已轉向採用 65 nm 技術的0.7μm像素,邏輯和信號處理器都採用 14 nm FinFET 工藝。採用 14 nm 工藝的 144 MP BSI-CIS 邏輯芯片比採用 28 nm 工藝的邏輯芯片功耗降低了 42%。在 65 nm–14 nm 處理技術中探索了 12 MP 雙光電二極管 (2PD) BSI-CIS,與 65 nm–28 nm 技術處理的功耗相比,功耗降低了 29%。雙光電二極管像素的每個光電二極管尺寸為0.7μm×1.4μm,導致像素尺寸為1.4μm×1.4μm,如圖7所示。左右光電二極管信號之間的差異用於相移檢測自動對焦數據,它們的總和用於輸出圖像數據。

通過使用 14 nm 技術,邏輯和圖像處理的複雜性增加,從而允許相同的芯片尺寸具有更多功能。它還實現了 120 fps 的幀速率。這兩種應用都使用堆疊芯片架構,直接鍵合,然後是外圍通孔最後的 TSV 芯片間互連。底層邏輯芯片的縮放可以吸收更復雜的ML/AI算法和無線通信功能。

三、RGB:近紅外背照式 CMOS 圖像傳感器。

移動設備的近紅外 (NIR) 成像通常在 850 nm 至 940 nm 的波長範圍內進行。區分可見光環境中的信號使 NIR 圖像適合虹膜認證和麪部識別。基於近紅外夜視的圖像傳感器對於監控應用也很有吸引力。硅在近紅外波長下的量子效率 (QE) 較低。傳統圖像傳感器在520 nm可見光、850 nm和940 nm紅外光下的QE分別為70%、15%和10%。硅所需的 50% 吸收厚度 在 850 nm和940 nm波長下分別為10μm和40μm。一些設計增加 BSI-CIS 的硅厚度以增加 NIR 吸收,並添加 DTI 以改善 NIR 範圍內的 QE,如 OmniVision Technologies 的 Gen-2 圖像傳感器技術中所述。NIR QE 改進方法基於先進技術,無需對像素電子器件進行重大改變。然而,在 NIR 範圍內實現更好的 QE 所需的更厚的硅給後通孔 TSV 工藝帶來了挑戰。

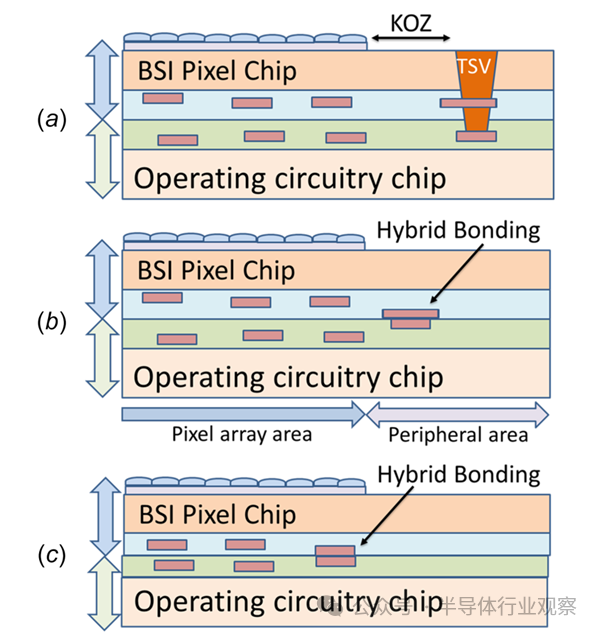

眾所周知,更深的TSV蝕刻工藝會增加高深寬比蝕刻工藝的難度、增加工藝時間並降低產量。另外,第二代圖像傳感器技術評估了不同的互連方法。如圖8所示,外圍後通孔TSV的間距可以如圖8(a)所示收緊。在沒有用於TSV的KOZ的情況下,可以通過使用外圍混合接合來減小芯片尺寸,如圖8(b)所示。如圖8(c)所示,可以通過將混合鍵放置在像素陣列下方來實現進一步的減少。

通過將像素陣列下方的 Gen-1 後通孔 TSV 改為 Gen-2 混合鍵合,16 MP 圖像傳感器的面積減少了 10%。這些混合鍵有時被稱為列混合鍵合,因為它們具有將像素陣列與列和行存取處的操作電路連接的功能。它不受位置限制,因此可以將它們放置在像素陣列下方。由於能夠分別優化像素陣列芯片和邏輯芯片的工藝流程,進一步凸顯了性能的改進,例如全井電容(full well capacitance)增加了20%,靈敏度提高了12.5%,噪聲更低。例如,它減少了組合工藝與額外熱步驟的干擾,使用鎢填充像素之間的深溝槽,並允許柵極氧化物優化。更高的靈敏度間接降低了系統功耗。2020 年最新發布的報告表明,新的表面處理方法與更厚的硅和深溝槽隔離相結合,使 850 nm 和 940 nm 的 QE 分別達到 70% 和 50%(使用 2.9微米像素的數據測量),使用Nyxel 2 技術。

索尼提出了一種不同的方法,通過處理衍射結構(PSD:Pyramidal Surface for Diffraction structures)的波長尺度金字塔表面來增加像素內深溝槽隔離限制的近紅外光傳播長度,而不增加硅厚度。

為了在同一圖像傳感器中結合 RGB 和 NIR 功能,紅外截止濾光片通常嵌入相機模塊中。在明亮的日光下,紅外截止濾光片可阻擋近紅外和紅外,以減少對底層電子設備的光學干擾。在夜光環境下,紅外截止濾光片會縮回,以允許近紅外光通過。

四、三芯片堆疊捲簾快門(rolling shutter)

圖像失真是捲簾快門 (RS:rolling shutter) 運動圖像應用的常見問題,是由串行讀取方法在第一個像素和最後一個像素讀取之間的時間滯後引起的。為了提高 RS 的性能,我們探索了在像素器件中添加電容器的選擇,以犧牲像素尺寸的增加為代價。在不增加像素尺寸或芯片尺寸的情況下,將單獨的DRAM芯片插入到像素陣列芯片和操作電路芯片堆疊中。

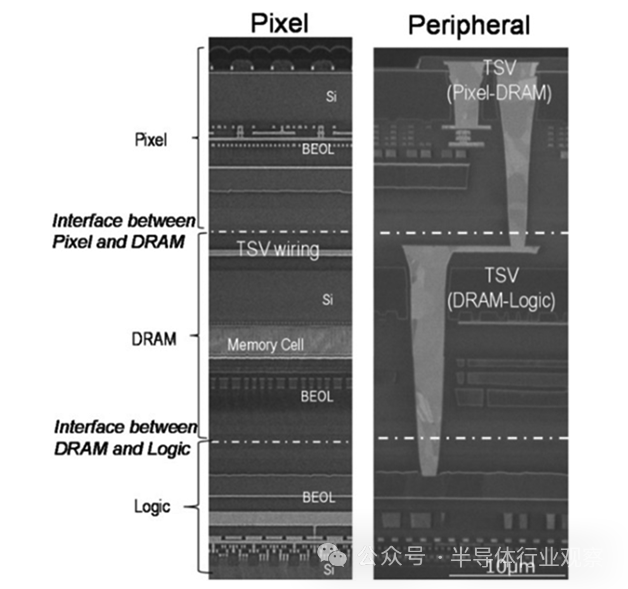

索尼在2015年發佈了像素/DRAM/邏輯三芯片堆疊RS。DRAM芯片堆疊在像素陣列芯片和邏輯芯片之間,用於臨時存儲信號。像素陣列、DRAM和邏輯芯片分別採用90 nm、30 nm和40 nm工藝技術加工。DRAM的硅被拋光至3-5μm 厚,使芯片堆疊的總厚度保持在 130μm。像素陣列和 DRAM 芯片都向下面向邏輯芯片。後通孔 TSV 和重新分佈層由面對面直接鍵合 DRAM 和邏輯芯片堆棧的背面形成,用於外圍芯片到芯片互連。然後,BSI 像素陣列芯片被面對面粘合在 DRAM 邏輯芯片堆棧的頂部。後通孔 TSV 從 BSI 像素陣列芯片的背面形成,作為外圍區域的芯片間互連。接合焊盤處的 後通孔 TSV 直徑為2μm至1.5μm,間距為6.3μm。當臨時存儲器可用時,具有最小化圖像失真的並行讀出方法成為可能。此 7.73 mm(對角線)三芯片堆疊 BSI-CIS 演示了1.22μm×1.22μm像素下 30 fps 的幀速率 和總計 19.3 MP。層疊芯片的剖面如圖9所示。

三星於 2017 年設計了三芯片堆疊 RS ,隨後於 2018 年發佈了產品。為了提高速度,在像素陣列和模擬邏輯芯片堆棧下方添加了兩個千兆位 (Gb) LPDDR4 DRAM 芯片。1.4μm像素12MP圖像傳感器可以在1/120秒內以960fps的速度捕獲圖片並傳輸全幀數據。DRAM 芯片與圖像傳感器芯片堆棧的連接是通過使用微凸塊熱壓縮工藝將邏輯芯片與 DRAM 芯片鍵閤中的 TSV 進行典型 3D 集成來實現的。虛擬芯片放置在 DRAM 芯片旁邊,以補償芯片尺寸差異。

五、全局快門

儘管RS圖像傳感器通過添加DRAM芯片來存儲像素信號並縮短信號讀出延遲已經得到了很大的改進,但進一步推進仍在繼續。全局快門 (GS:Global Shutter) 技術已被探索用於最大限度地減少圖像失真並進一步提高電影的幀速率。全局快門的最新趨勢是將電容器放入像素中以存儲圖像信號並消除串行讀取方法引起的延遲。

有兩種主要的全局快門設計將電容器添加到像素設備中。電荷域全局快門將光電二極管產生的信號存儲在電容器中以供以後轉換。電壓域全局快門將來自光電二極管的信號轉換為電壓域,然後將其存儲到電容器。存在一些與添加電容器相關的問題。當信號存儲在電荷域電容器中時,需要遮光層來降低電容器的光敏感性。電壓域中的電容器更穩定,但將信號轉換到電壓域所需的額外電路進一步降低了填充因子 (FF:fill factor)。光電二極管面積與像素總面積之比較低或 FF 較低,導致像素陣列效率低下。最好將存儲器存儲電容器和附加像素電子器件移至堆疊在 BSI 或 FSI 光電二極管陣列芯片下方的單獨芯片,以獲得更好的 GS 性能。像素級集成是像素並行圖像處理所必需的,其中兩個堆疊芯片中的分區像素電子器件通過芯片間像素級互連連接在一起。

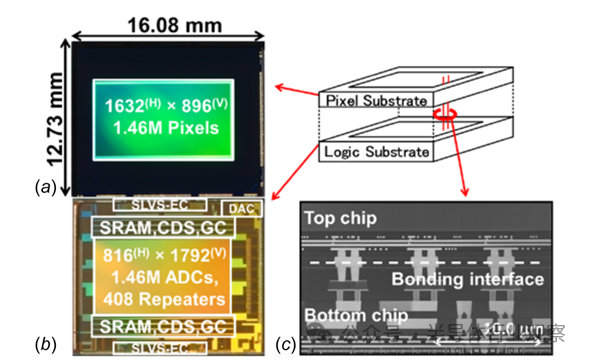

索尼公司於 2019 年使用混合鍵合芯片間互連對使用像素級集成的全局快門圖像傳感器進行了評估。每個像素中都添加了由十多個晶體管組成的模數轉換(ADC)單元。額外的像素電子器件在兩個芯片中進行分區和處理,每個芯片通過兩個混合銅-銅鍵連接,一個用於功率和電壓控制,另一個用於光電二極管信號。如圖10(a)所示,該6.9μm 像素1.46MP GS圖像傳感器具有300萬個Cu-Cu混合鍵(hybrid bonds)。圖像傳感器的尺寸為12.73毫米×16.08毫米。相當於單芯片方式芯片尺寸的70%。分區像素電子器件極大地改善了 FF。

底層芯片具有146萬個ADC轉換單元以及其他存儲器和處理器功能,如圖10(b)所示。Cu-Cu雜化鍵的截面如圖10(c)所示。為每個圖像傳感器使用數百萬個銅-銅混合鍵合來製造用於像素級集成的晶圓級混合鍵合是一個具有挑戰性的步驟。

六、高動態範圍

動態範圍是傳感器可檢測到的最大信號與最小信號的比率。人類視覺的動態範圍約為90 dB。針對工作範圍進行優化的圖像傳感器可能會過飽和,超出可檢測範圍。高動態範圍(HDR)更適合在更廣泛的外部環境中檢測圖像。前文就描述了一種對 RGB CIS 光電二極管和圖像重排馬賽克使用曝光時間微分的方法——通常需要更復雜的像素電子器件來進一步擴大動態範圍。

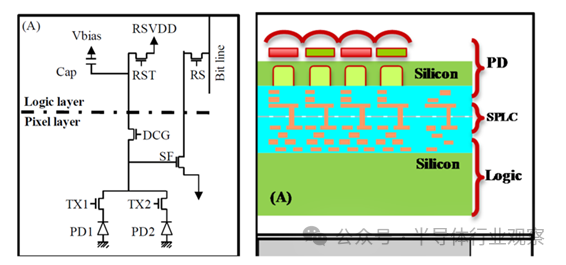

OmniVision 通過使用雙轉換增益 (DCG:dual conversion gain) 方法以及每個像素中的高增益和低增益像素電子器件來擴大動態範圍,如圖11所示。低照明下需要高轉換增益以實現低讀取噪聲,而強照明下則需要低轉換增益。需要一個大電容器來調製浮動擴散電容以及高增益和低增益電路之間的晶體管開關。這些額外的像素電子器件會增加像素尺寸並降低性能。

像素級集成的選擇是優選的,基於 1.5 μm像素 8 MP 堆疊芯片圖像傳感器評估幾個像素電子分區 。採用堆疊像素級連接(SPLC:Stacked Pixel Level Connections)技術,在像素陣列芯片屏蔽環境光的邏輯層中添加一個大電容器。該設計可產生 83.8 dB 的 HDR,高低轉換增益比為 10。這是 2018 年評估的最小間距的像素級互連。在此設計中,每個像素的芯片到芯片像素級連接通過每個像素最少1個混合鍵、最大1.5μm 節距以及因此最小密度440,000 bonds/mm²來估計。OmniVision DCG HDR 圖像傳感器在 2020 年發佈的最新產品是 48 MP 1.2 μm像素,具有出色的信噪比、像素合併(4 比 1 合併為 12 MP 2.4 μm像素)和堆疊芯片架構。

七、飛行時間和光檢測與測距

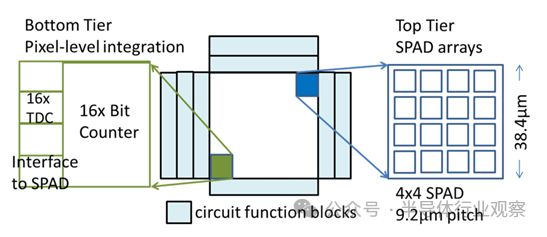

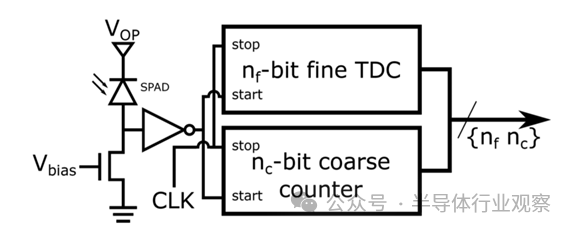

HDR 也已通過使用單光子雪崩光電二極管 (SPAD:Single Photon Avalanche Photodiodes ) 進行了探索。為了在極低光照條件下實現可接受的圖像檢測,光電二極管通常設計為在雪崩模式(avalanche mode or Geiger mode)的反向偏壓下工作,以檢測幾乎捕獲的光子。在雪崩模式下,生成的每個信號電荷都可能導致電流尖峯。位計數器電路代替電荷或電壓信號來收集信號。像素電子器件可以是簡單的 SPAD、帶有位計數器的 SPAD 以及帶有位計數器和時間數字轉換器 (TDC) 的 SPAD,如圖12所示。Quenching circuit通常設計有SPAD,以便正確重置SPAD。當TDC設計在操作電路中時,可以確定物體的距離。它被認為是飛行時間 (ToF) 檢測。支持需要 SPAD 的應用的整體電路通常相當大,複雜的電路鼓勵使用像素電子分區方法和像素級集成。

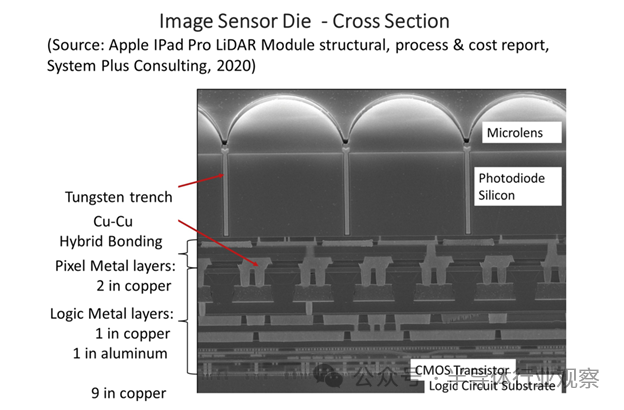

2019 年,全球首款採用混合鍵合進行像素級集成的商用 NIR SPAD ToF 傳感器在 iPad 11 Pro 中實現。移動設備中的深度感測通常使用間接 ToF 來確定距離,以雙像素傳感器的圖像處理為例。直接 ToF 需要更復雜的成像方法和光源。iPAD Pro 11和iPhone 12 Pro都添加了LiDAR功能,用於增強現實和其他識別功能的應用。根據 System Plus Consulting 的分析,這種短距離 ToF 功能是由索尼 ToF 圖像傳感器實現的,作為蘋果產品中的第一個 NIR SPAD ToF,如圖13所示。

LiDAR 使用垂直腔表面發射激光 (VCSEL:Vertical Cavity Surface Emission Laser ) 源投射 9 × 64 點陣結構光。圖像傳感器檢測反射光以確定具有距離的圖像。該 NIR 傳感器採用 10 μm像素 30 kP SPAD 設計。成像芯片與使用混合接合技術的操作電路芯片層疊,以形成像素級Cu-Cu芯片到芯片互連,如圖13所示。

超越移動應用

圖像傳感器的不同應用存在許多具有挑戰性的領域。監控攝像頭的廣泛使用依賴於日光下的功能性 RGB 成像和黑暗下的 NIR 成像。需要擴大檢測波長範圍和高 QE。自動駕駛汽車的高級駕駛輔助系統是另一個快速增長的應用領域。激光雷達是自動駕駛汽車成功的關鍵要素。短距離激光雷達已可在幾英尺內運行的智能手機中使用。具有數百米距離靈敏度的遠程激光雷達是一個活躍的領域,有許多方法正在開發中。光源掃描儀可能從大型機械系統轉移到微型片上激光系統。為了人眼安全,波長選擇正向 1550 nm 發展。能夠感應極弱光的寬動態範圍圖像傳感器非常重要。

一、長距離光探測和測距

已知 ToF SPAD 型光電二極管的填充因子(FF:fill factor)較低。在時間選通(time-gated) ToF SPAD 成像儀中像素電子器件的擬議改進中,使用 5-7 個晶體管證明了 10-25% 的光子檢測概率 。在單芯片配置中,填充因子可以低至 7%–13%。

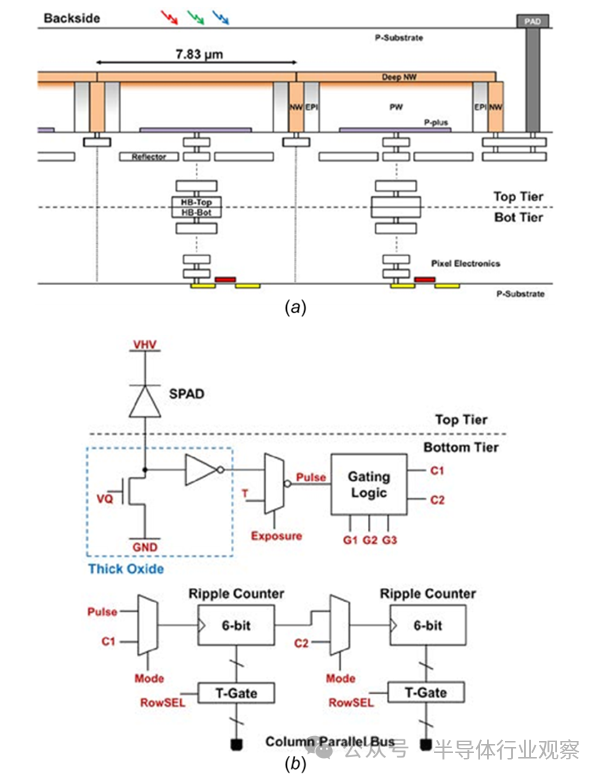

第一個 3D 堆疊式 SPAD 圖像傳感器具有單光子計數 (SPC:single-photon counting) 和時間分辨成像 (TRI:time-resolved imaging) 功能。像素尺寸縮小至7.83μm ,填充因子為45%。這是通過將複雜的像素電子器件移至底層芯片並留下由 65 nm 技術處理的像素陣列的頂層芯片來實現的,如圖14(a)所示。兩個芯片使用混合鍵合技術堆疊在一起。在此配置中,有趣的是發現一個電連接穿過TSV並從像素陣列芯片的背面引出,如圖14(a)的右角所示。包含大部分像素電子器件的底部芯片採用40 nm技術加工,電路原理圖如圖14(b)所示。

另一種用於激光雷達應用的兩層紅外 SPAD 的開發顯示了複雜的像素器件和操作電路,如圖15所示。如圖15的右側所示,在圖像傳感器的頂層中形成塊中的16個9.2μm × 9.2μm 像素SPAD陣列。相應的38.4μm×38.4μm塊中的支持電路 ,包括 像素接口、計數器陣列以及其他轉換和信號處理電路,形成在圖像傳感器的底層中,如圖15的左側所示。