CXL,兩大難題_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。59分钟前

最近,內存專家Jim Handy發表了一篇有關 Compute Express Link (CXL) 的博客,以及他認為有關該技術的兩個難題。

CXL 是一種基於開放標準的相對較新的緩存一致性內存協議,旨在使大型內存池可供大型計算機系統和數據中心中的多個處理器使用。在我看來,CXL 的中心目標是幫助數據中心架構師避免過度配置多處理器系統中的每個 CPU 或帶有 DRAM 的大型數據中心中的服務器。

當您不知道系統中的 CPU 將負責執行什麼類型的工作負載時,就會出現這種過度配置的問題,因此您需要為最壞的情況配置 DRAM。如果 CPU 能夠以某種方式逐個任務地從中央池中獲取一塊內存,那麼這些 CPU 就不需要過度配置自己的內存。他們可以根據需要請求內存。

為了實現這一壯舉,CXL 內存需要比本地內存更鬆散地與 CPU 耦合。CPU 幾年前吸收了 DRAM 控制器,以消除與本地 DRAM 外部內存控制器相關的延遲和功耗。如今,CPU 的三個關鍵品質因數是其擁有的片上 DRAM 控制器的數量、這些控制器可以命令的 DRAM 類型以及片上內存控制器與附加設備之間的 DRAM 事務處理速度。DRAM 以兆傳輸/秒 (MT/sec) 或千兆傳輸/秒 (GT/sec) 為單位。所有這些因素共同決定了您可以將多少本地內存連接到 CPU 以及該內存的執行速度。CXL 通過消除片上內存控制器,極大地擴展了 CPU 可以訪問的內存量。

CXL 1.0 於 2019 年出現,CXL 聯盟於 2022 年 8 月宣佈了 CXL 3.0 規範。CXL 協議在 PCIe 的 I/O 語義之上添加了一致性和內存語義。CXL 3.0 通過採用 PCIe 6.0,將該協議的最大傳輸速率提高了一倍,達到 64 GT/s。由於它基於 PCIe,業界發現 CXL 規範的物理部分易於理解和使用。

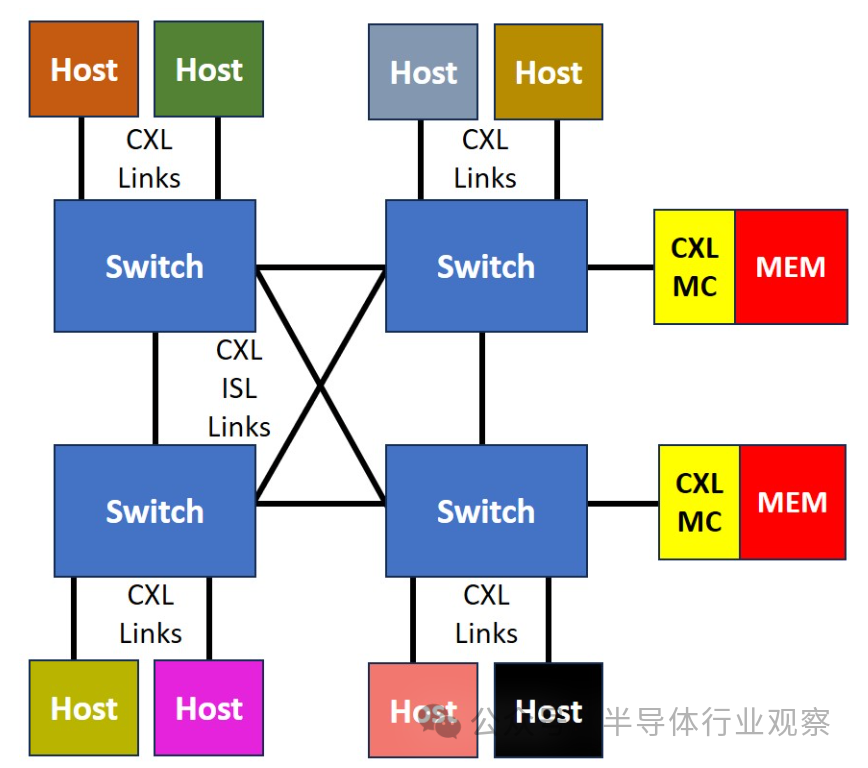

特殊的 CXL 交換機與 PCIe 交換機類似,基於 CXL 專用內存控制器將多個 CPU 與多個 CXL 內存子系統連接起來。CXL 交換機允許以編程方式設置和拆卸許多有趣的 CPU/內存系統拓撲。CXL 還使得將內存中保存的大數據塊從一個 CPU 傳輸到另一個 CPU 變得更加容易和快捷。傳輸任意大小的數據塊只需將指向該數據的地址指針從一個 CPU 傳遞到另一個 CPU。CXL 實質上將大型系統或整個數據中心中的所有可尋址內存組合成一個大型內存池,可供系統中的每個 CPU 訪問。

以下是Jim Handy 的博客原文:

CXL 的神奇之處主要在於它可以向系統添加內存,而不會因大量電容負載而使處理器陷入困境,也不會因添加內存通道而消耗大量電量。它通過允許 CPU 通過高度簡化的 PCIe 通道與由其自己的控制器管理的 DRAM 進行通信來實現這一點。

通過添加 CXL 交換機,多個處理器可以訪問相同的內存,從而允許將內存分配給一個處理器或另一個處理器,就像靈活分配其他資源(如處理器和存儲)一樣。換句話説,CXL 分解了內存。

那麼CXL面對的兩個難題是:

1) CXL 的內存銷量會增加還是減少?

這項新技術的好處之一是,CXL 連接的內存給 CPU 帶來的電容負載很小,因為它位於 CXL 通道的另一端,這是點對點連接。CXL DRAM 模塊具有一個控制器,該控制器一側與 CXL 通道通信,另一側與 DRAM 通信。如果單個 CXL 模塊包含大量 DRAM 芯片,則該控制器的任務是驅動所有這些芯片及其所有電容負載,而處理器不必擔心它。

DRAM 製造商認為這是一個潛在的福音,因為圍繞 CXL 構建的系統可以支持比直接連接到處理器更大的內存量。美光 2023 年 3 月的白皮書:美光關於 CXL 對 DRAM 位增長率影響的觀點表示:“CXL 將有助於維持比沒有它時更高的 DRAM 位增長率。” 雖然這是一個相對温和的説法,但在與美光及其競爭對手三星和 SK 海力士的對話中,他們將 CXL 描述為 DRAM 銷售的火箭助推器,可能導致行業千兆字節增長曲線拐點。

但對 CXL 最感興趣的最終用户是超大規模數據中心,他們有不同的觀點。2022 年 10 月,微軟和谷歌發表了一篇研究論文,標題為:Pond: CXL-Based Memory Pooling Systems for Cloud Platforms。該論文稱:“我們的分析表明,通過跨越 16 個插槽的 Pond 池,我們可以將 DRAM 需求減少 7%,這對於大型雲提供商來説相當於數億美元。” 更詳細的句子告訴我們:“我們的結果表明,池大小為 16 個插槽時,Pond 可以將所需 DRAM 量減少 7%,並假設 CXL 使延遲增加 222%。這意味着雲服務器成本總體降低了 3.5%。”

我們怎樣才能調和這兩種相互衝突的觀點呢?CXL 會增加還是減少 DRAM 銷量?這是第一個難題。

2) CXL 在內存/存儲層次結構中處於什麼位置?

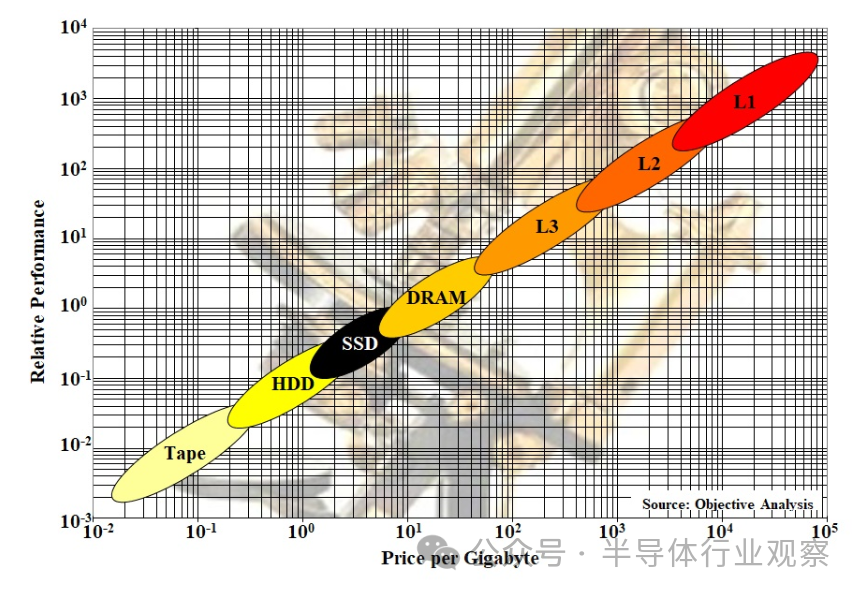

這是記憶專家的第二個難題。它與 CXL DRAM 如何適應內存/存儲層次結構有關:

它比 DRAM 慢,因為它位於控制器、最多兩個交換機以及網絡或通道後面;它比 DRAM 更貴,因為它需要控制器;CXL 模塊類似於 DIMM,只不過 DRAM 和 CXL 通道之間有一個 CXL 控制器。該控制器增加了 DRAM 訪問的延遲,同時也增加了模塊的成本;

瞭解這一點重要性的一個好方法是查看我們在許多演示中展示的 Objective Analysis 內存/存儲層次結構圖。SSD Guy 的博客文章對此進行了詳細描述,因此我僅在此展示而不解釋:

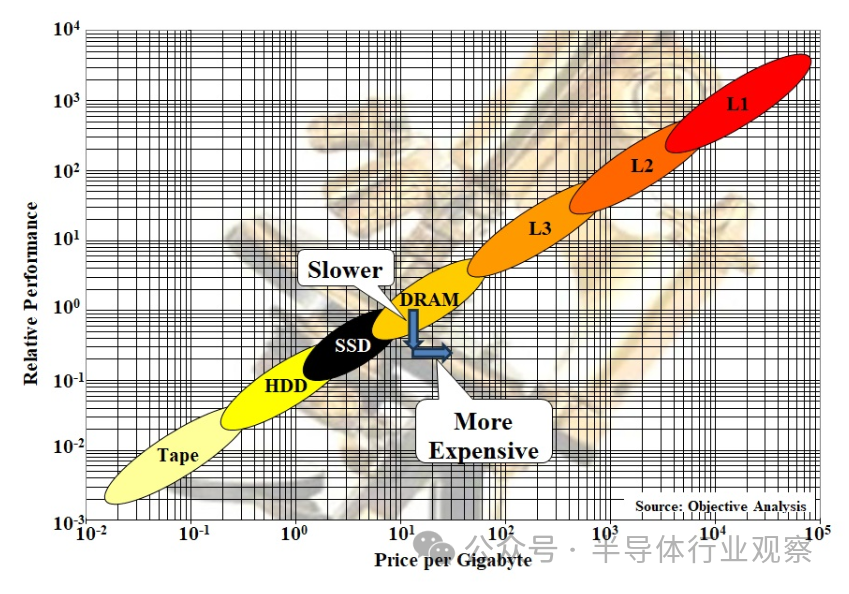

CXL 在哪裏適合這個?由於近期主要針對 DRAM,因此它將減慢 DRAM 層的速度,同時增加其成本。這由下面的再現中的箭頭表示:

精明的讀者可能已經注意到,上面引用的 Pond 論文指出,CXL 為 DRAM 訪問增加了 222% 的延遲,使其速度慢了三倍多。(誠然,這個數字來自測試設置,該設置很可能比明天基於 CXL 的系統慢。)儘管如此,CXL DRAM 模塊的控制器確實給 CXL 連接的 DRAM 增加了大量的延遲。CXL 2.0 中定義的更復雜的系統通過將信號引導通過交換機而增加了更多延遲,增加了額外的延遲,而 CXL 3.0(如下)的結構支持通過將信號引導通過兩個交換機來創建結構,從而導致更多的延遲。

在這裏,我們遇到了決定哪個更重要的挑戰:延遲或帶寬。這一切都取決於主機上運行的應用程序。帶寬匱乏的程序以及具有更可預測的數據訪問模式的程序將受益於 CXL 的高帶寬。數據訪問模式更加隨機的程序將受到 CXL 延遲的影響。

一些讀者可能已經注意到,這個問題與幾十年前硬盤世界中注意到的問題相同。在 20 世紀 80 年代,人們強烈主張串行數據訪問速度與磁頭延遲之間的關係。為了解決這個問題,設計了一種稱為 IOPS 的新測量方法,它反映了典型應用程序的行為來測量兩者的混合。也許記憶需要這樣的衡量標準。

與此同時,基於 CXL 的 DRAM 的性能可能有利於某些應用程序,但會降低其他應用程序的性能。隨着 CXL 得到更廣泛的部署,這一點將變得更加明顯。

從長遠來看,CXL 允許非 DRAM 內存競爭該大容量設備。使用 DDR 的 CPU 上的直連通道對新技術非常不利,因為 DRAM 的詳細狀態機已融入通道操作中。任何不是 DRAM 的東西,都有不同的狀態機,如果它試圖競爭本地通道,就需要模仿外來的解決方案,這是一個巨大的障礙。新技術只是在實驗室中停滯不前,無法投入商業應用。

然而,在 CXL 上沒有人知道你是否是 DRAM。它是用於加載和存儲操作的乾淨事務語義,以及有關一致性和隱私的補充信息。這創造了一個新的市場機會,不同形式的內存可以競爭相同的乾淨的加載-存儲語義。這需要幾年時間,但這才是 CXL.mem 可能帶來的真正革命。更大、更低功耗、更密集且更便宜的主存儲器。