掩膜的“大”麻煩_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。1小时前

作者| 杜芹

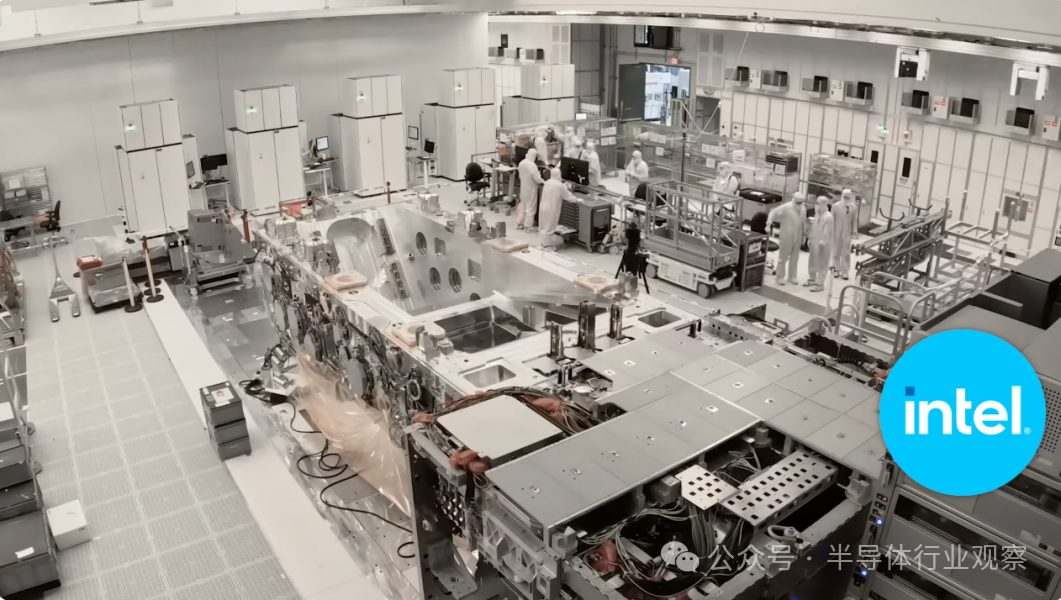

近日,一段ASML的高數值孔徑(High-NA) EUV光刻機進駐英特爾工廠的視頻,引發了半導體行業的廣泛關注。因為,這關乎着摩爾定律能否繼續走下去。對於2nm以下的芯片製造,擁有更高數值孔徑的0.55 High-NA EUV光刻機起到至關重要的作用。

然而,一個不爭的事實是,High-NA EUV光刻機要比上一代EUV光刻機要複雜的多,其必然帶來芯片設計和製造的新挑戰。作為最早購買到High-NA EUV光刻機的英特爾,近日其CEO帕特·基辛格在More than moore的一次採訪中透露,想採用更大的掩膜來發揮High-NA EUV光刻機更大的經濟效益。

一台EUV光刻機的成本約為2.5億美元,而這台高數值孔徑(High-NA)EUV光刻機的成本大約為4億美元。如此昂貴的投資,值得嗎?我們都知道,摩爾定律本質上屬於經濟定律。摩爾定律指出,集成電路上的晶體管數量每隔18個月會翻一番,而芯片的成本會下降一半。這推動了芯片製造技術的不斷進步,也使得電子產品變得更加普及。

不由發問,芯片微縮(or 摩爾定律)的下一步,是製造更大的掩膜嗎?

原因幾何?

眾所周知,在當下先進工藝芯片製造過程中,光刻是芯片製造中最關鍵的工藝步驟之一,其精度直接影響芯片的良率和性能。為了繼續縮小邏輯和存儲節點,光刻工具必須能夠打印更小的特徵。通過增加數值孔徑,High-NA EUV光刻機能夠實現更小的特徵尺寸和更高的圖案密度,可以説是“全村的希望”。

雖然High-NA EUV光刻機帶來了更高的分辨率等好處,但是其也帶來了其他的不利之處。與普通的EUV光刻機相比,High-NA EUV光刻機最大的變化是,其曝光視場減半(即在單個曝光步驟中曝光的晶圓區域較小了一半)。

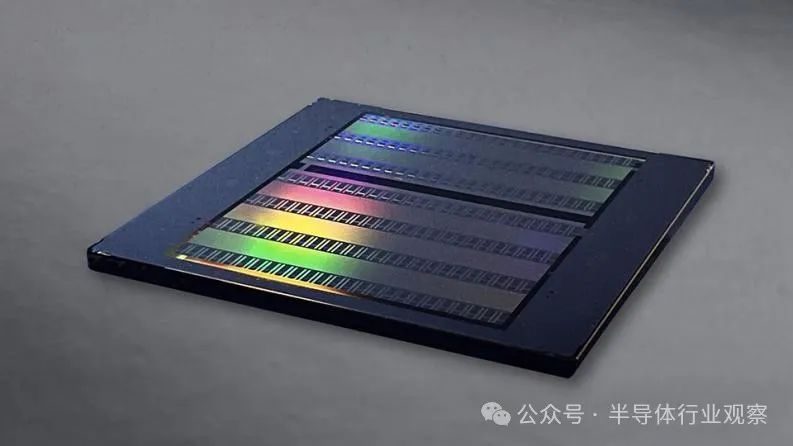

High-NA EUV 使用變形鏡頭,X 和 Y 方向的放大倍率存在差異,其掩模尺寸的縮小比例在水平方向不變,保持4倍,但在垂直方向上縮小了8倍,這導致曝光區域縮小了一半,變成了 26 x 16.5 毫米,目前業界標準的 EUV 曝光區域是 26 x 33 毫米。這意味着,**High-NA EUV光刻機掩模能夠映射到晶圓上的區域面積減少了一半,形成了所謂的半場成像。**因此,對單個晶圓進行圖案化需要兩倍的曝光次數,這也使得打印晶圓的時間延長了一倍。

一個解決方案是,**將設計分成兩個掩模版並縫合在一起,但這不是易事。**想象一下,嘗試用兩張相鄰的底片打印一張照片來生成一張無縫的圖片,這是非常困難的。

而且,如今為了滿足AI、5G等計算能力需求旺盛的應用程序的需求,行業正在朝着大芯片的方向發展,許多當前的 Nvidia 芯片無法使用High-NA EUV進行打印。這個挑戰將早早晚晚不得不解決。

因此,業界開始考慮另外一種方案:**生產更大的掩膜。**掩膜(Mask)是光刻過程中的關鍵元素。掩膜上有預先定義的圖案,這些圖案在光刻過程中通過曝光光線傳遞到晶圓上,形成電路圖案。掩膜的精確度和尺寸直接關聯到最終產品的質量和產量效率。

作為最早“吃螃蟹”的英特爾,正在帶頭推動半導體行業採用更大的掩模尺寸標準。雖然英特爾表示,與傳統的雙重曝光技術相比,High-NA EUV 光刻機的單次曝光技術可以減少工藝步驟,提高生產效率,降低生產成本。而且,相比其他多圖案和自對準技術,High-NA EUV 光刻也具有優勢。

但帕特·基辛格也指出,也許更大的掩模尺寸可以使 EUV 整體上更加經濟。

目前EUV光刻機所使用的標準掩膜尺寸是 6 x 6 英寸。英特爾希望ASML和英特爾內部的掩模製造團隊,能夠研發更大尺寸的掩模,將掩模尺寸加倍到6 x 12英寸,恢復到標準的曝光區域大小。這樣就可以在生產較大芯片時避免複雜且難度較高的縫合過程。

綜合來説,使用更大的掩模尺寸可以帶來以下優勢:

提高產量:在一個步驟中曝光更多的晶圓面積可以提高產量。降低成本:減少曝光步驟可以降低成本。消除設計限制:更大的掩模尺寸可以使芯片製造商在設計芯片時更加靈活。

據悉,英特爾獲得的High-NA EUV光刻設備最初將用於學習和掌握該技術,並計劃在未來兩到三年內在英特爾18A工藝節點上實現(儘管不是用於大批量生產),並最終採用其英特爾 14A 製造工藝進行大批量製造。

挑戰重重

然而,掩膜尺寸的擴大是一項巨大的技術挑戰,而且還會產生許多連鎖反應,因為當前的掩模基礎設施是圍繞6x6英寸方形掩模版基礎設施設計的。將掩膜尺寸擴大到6x12可能需要新的光刻膠、計量、薄膜材料、掩模和檢查工具等,不可避免的要對基礎設施重新進行大量投資。即使在當前尺寸下,生產無缺陷掩模坯料也是低數值孔徑EUV開發的一個障礙,更不用説擴大一倍。

從本質上講,整個掩模行業的供應鏈都必須改變,可謂是牽一髮而動全身。相關的產業鏈主要有:

**掩膜版寫入器:**IMS Nanofabrication GmbH是一家銷售 6 x 6 英寸掩模的掩模寫入器的公司。英特爾和台積電都是它的股東。IMS很大程度上可能將支持 6 x 12 英寸格式。生產EUV掩膜寫入器的重要廠商還有應用材料。

**光掩膜版:**通常掩膜版是由塗有金屬膜和感光劑的 6 x 6 英寸玻璃基板製成,製作6 x 12英寸的掩膜版比標準6 x 6英寸的掩膜版要複雜,因為它需要更大的玻璃基板和更多的材料。同時,製造過程中對精度和均勻性的要求更高,因為任何小的缺陷在大尺寸掩膜上都可能放大。此外,處理和對齊更大的掩膜也會更加挑戰,需要特殊的設備和技術。

2024年2月,IBM與日本光掩膜供應商Toppan Photomask簽訂了半導體EUV光掩模聯合研發協議,從2024年第一季度開始的五年內,兩家將合作開發用於 2nm 工藝節點的極紫外 (EUV) 掩模,還包括開發用於1nm技術的High-NA EUV 技術的掩模。

**掩膜保護膜:**這是一種薄膜(pellicles),在芯片製造過程中覆蓋在光掩模上。其主要作用是保護光掩模免受灰塵、碎屑和其他污染物的損壞。這些污染物會造成光掩模缺陷,進而導致芯片良率下降。與光掩膜類似,6x12的薄膜開發相比6x6薄膜也會更具挑戰性。

**掩模檢測設備:**Lasertec和KLA銷售EUV掩模檢測系統。Lasertec 於 2019 年發佈了光化圖案掩模檢測 (APMI) 系統 ACTIS,此後一直將其作為 EUV 掩模檢測的光化檢測解決方案提供。Lasertec已經在進行下一代High-NA EUV光刻檢測設備的研究,預計可能會支持 6 x 12 英寸掩模(感興趣的可以查看《Actinic pattern mask inspection for high-NA EUV lithography》)。

作為光刻機的製造商,ASML需要適應更大尺寸掩模的變化。這是一項具有挑戰性的任務,因為它涉及到多方面的技術和工程調整。

High-NA EUV時代下,各產業鏈之間的複雜性和相互依賴性達到了新的水平。正如 EUV 需要生態系統整合一樣,將High-NA EUV 光刻技術投入生產也需要深入的協作和夥伴關係。學習如何利用它將推動下一個十年的半導體創新。

在這方面,美國紐約州與IBM、美光和其他行業參與者投資了100億美元擴建奧爾巴尼納米技術園區,新建一個尖端的High-NA EUV 中心,今年破土動工。其中包括在奧爾巴尼納米技術綜合體建造一個名為 NanoFab Reflection的新設施,併購買ASML的5200 High-NA EUV 設備。現有的 NanoTech Complex 成員,包括東京電子和應用材料公司,將與日本 Rapidus等國際合作夥伴一起獲得新的EUV設備的使用權。

**大芯片?小芯片?**未來芯片設計之思考

從芯片設計公司的角度來看,如果要使用High-NA EUV光刻機生產更大的芯片,行業可能面臨需要重新設計芯片以適應新技術的挑戰。有幾個趨勢值得關注:

向Chiplet邁進:由於製造大尺寸的芯片在成本和複雜性上都較高,製造商可能會重新評估單個大芯片的設計。通過優化設計,可以將大芯片分割成多個小芯片,每個小芯片執行特定的功能。這些小芯片可以在後期通過封裝技術整合,實現與單個大芯片相同或更好的性能。這不僅能減少生產難度,還可以提高產出的靈活性和整體性能。

先進芯片封裝技術的發展:隨着芯片尺寸減小,先進的封裝技術變得至關重要,因為它們允許不同的芯片組件在較小的空間內集成,而不會犧牲性能。通過多芯片模塊(MCM)或芯片堆疊技術等封裝方法,可以實現高性能計算和存儲,同時優化功率效率和信號傳輸。這些技術的進步是克服High-NA EUV在製造大型芯片方面遇到的挑戰的關鍵。

寫在最後

總結來説,在經濟定律為本之下,High-NA EUV還有很長的路要走。

相信這也是台積電謹慎選擇High-NA EUV光刻機的箇中原因。有分析師表示,High-NA EUV可能要到2030年或更遠的時間才會出現在台積電的路線圖上。

High-NA EUV光刻機其他潛在廠商還包括三星、美光、SK海力士。ASML已經透露了大約10~20個High-NA EUV設備訂單。ASML 韓國公司總裁 Lee Woo-kyung 在參加今年1月舉行的SEMICON 韓國 2024 行業領導晚宴之前透露,“我們期待2027年帶來三星電子和ASML的合資企業新研發中心的High-NA EUV設備。”據悉,三星電子從 1nm 工藝開始就使用該設備。其他廠商暫無明確信息透露。

對於High-NA EUV光刻機的實際商用,未來台積電和三星又會如何看待增大掩膜尺寸的問題呢?