功率半導體測試,這個值得一看_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。1小时前

WBG半導體可靠度測試H3TRB專區

測試類型

動態 H3TRB/ DRB 測試系統

測量技術

◆每個系統80-240個被測設備(80個被測設備1個高壓電源)

◆0V至1500V;4A,用於80DUT

◆單個DUT泄漏電流測量(靜態H3TRB期間)

80個測量通道

◆通過關閉開關提供單個DUT過流保護

基於硬件的單個DUT快速關斷,應力階段為65mA±20%,讀出階段為650μA±20

◆單DUT電壓控制

主動電壓控制可將負載電壓補償至<±0.5V

動態測試輸出級

◆最大輸出電壓高達1500V

◆輸出頻率可在0Hz至500kHz之間配置(最大頻率取決於電壓和DUT電容)

◆佔空比在25%至75%之間可變,每5%為一檔

軟件和測試程序

◆全自動測試程序

◆測量數據保存在tdms文件中

◆基於NILabVIEW和TestStand的軟件

安全

◆用軟件連接和評估試驗箱的外部安全鎖

◆高壓插頭連接的安全電壓監控

◆高壓供電設備的安全釋放

最新一代功率半導體SiC憑藉其在禁帶寬度和熱導率等方面的優勢,成功擊中高功率高能效應用需求。SiC測試有何挑戰與應對方法?以下技術文章介紹了使用動態柵極應力(Dynamic Gate Stress, DGS)測試過程對基於SiC的功率半導體進行新型可靠性測試的意義。相信您看完會受到啓發。

艾默生測試與測量業務集團-NI旗下公司SET GmbH半導體研究主管 Gabriel Lieser

碳化硅(SiC)組件擁有眾多技術優勢,適用於要求嚴格的應用。但硅(Si)組件和SiC組件之間存在結構差異,該差異會影響可靠性測試。

SiC(碳化硅)因其諸多出色性能成為半導體市場的重要材料。SiC的電氣擊穿電壓高於硅,因此可以提升組件的性能和效率。SiC還支持在更高温度下運行,這樣更有利於散熱,並可在更小的空間內實現更出色的性能。由於SiC具有高導熱性,使組件在嚴苛條件下也可高效運行。SiC組件的高開關頻率支持更小巧輕便的設計,這一點作為主要優勢使其可用於眾多應用。得益於上述特性,SiC涉及的應用行業日益廣泛,如電動汽車、可再生能源、工業驅動技術和航空航天。

SiC功率半導體需要新的可靠性測試

儘管SiC的應用前景廣闊,但仍需要針對基於SiC的新組件開發特定的可靠性測試。由於SiC和硅之間存在結構差異,無法使用現有的硅組件測試方法和假設條件。SiC的晶體結構與硅不同,因此具有不同的電學和熱學性能。如果忽略這些差異,則可能無法檢測組件的潛在生命週期或性能弱點。本文介紹了使用動態柵極應力(Dynamic Gate Stress, DGS)測試過程對基於SiC的功率半導體進行新型可靠性測試的意義。

DGS測試主要用於SiC-FET(場效應晶體管)。在測試過程中,向DUT(待測設備)的柵極以方波信號形式施加應力信號,該信號使用DUT的最大和最小柵極電壓。應力循環期間,採用主動温度控制將DUT調整至所需的應力温度。按照規定時間間隔暫停施加應力,以測量DUT的柵極閾值電壓和RDSon。

對於寬帶隙半導體測試過程,動態應力法和靜態應力法之間存在顯著差異。本文所述的測試過程採用SET GmbH的測試系統。使用該測試裝置對測試規範做出準確解釋,並將測量結果與實際應用進行比較。正確的測量過程對獲得可靠且可重複的測量結果同樣重要。測試相關內容可參考ECPE(歐洲電力電子中心)指南AQG 324,其中為歐洲SiC組件的新測試過程提供了實踐規範和指南。

動態柵極應力(DGS)測試:功能原理和測量過程

在DGS測試過程中,FET將其漏極和源極接點處連接至地電位,並在其柵極接點處施加應力(圖1)。施加的應力信號定義請參見AQG324指南。應力信號參數如下:方波信號的幅值是所需DUT規格所允許的最大負電壓和正電壓。DUT的上升時間(dV/dt)應為1V/ns左右,應力頻率應大於或等於50 kHz,佔空比範圍為20%至80%。

應力的持續時間由頻率決定,因此頻率越高測試時間越短。根據指南AQG324的規定,應力持續時間應不小於10^11個週期。測試温度應主動調節且嚴格控制在25 °C。

作為該測試過程的一部分,在全自動應力暫停期間對柵極閾值電壓和RDSon電阻進行測量。精確測量和適當預處理在測試過程中非常重要。預處理用於確保每次測量時測試對象的條件相同,從而保證測量結果具有可比性。本文中的指南AQG引用了JEDEC指南JEP184,其中介紹了正確的測量過程。柵極定義電壓應與建議的柵極-源極有效電壓或允許的最大/最小柵極-源極電壓相對應。

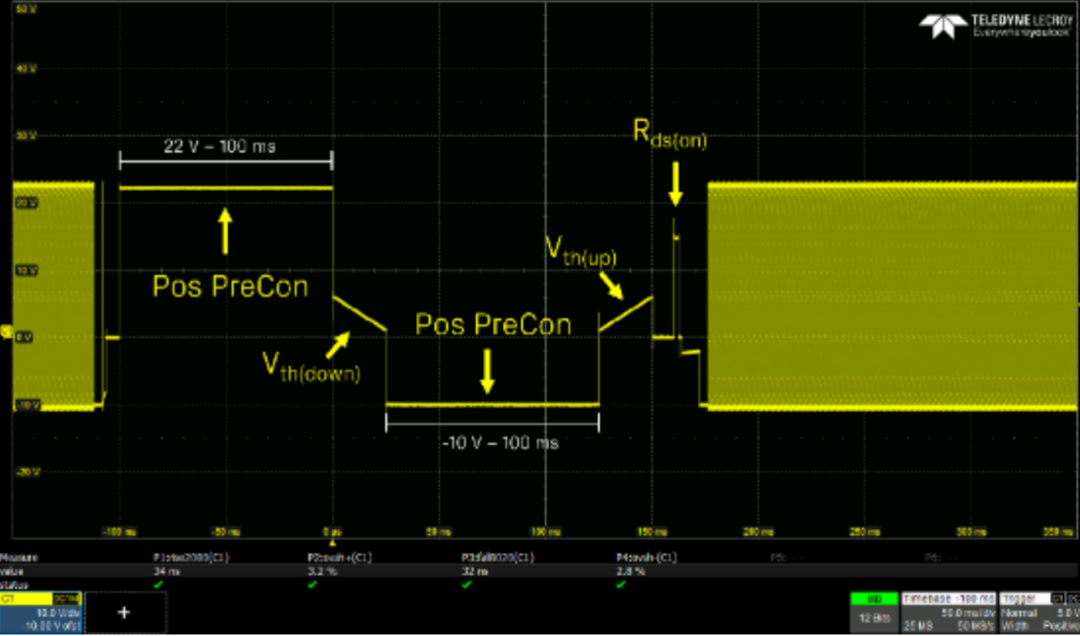

常見的預處理時間為100ms,但有時也會明顯延長。預處理完成後,應快速測量柵極閾值電壓,根據指南建議測量應在10ms內進行。此處所示的示波器記錄結果由SETGmbH的DGS系統完成,用於説明測量過程。

圖2中的曲線與柵極信號相對應。開始時,可以觀察到300kHz下-10V~+22V 的應力施加階段,隨後在測量過程開始時暫停。

測量過程從+22V預處理脈衝開始,該脈衝持續100ms。隨後,柵極電壓以非常小的步長持續變化。在測試階段,將測量漏極電流Idrain並將其設置為特定值,例如20mA。由於FET已打開,因此在“Vth(down)”測試階段開始時,有20mA電流流過。一旦柵極電壓接近閾值電壓,FET就會緩慢關閉,之前可完全通過FET的電流會緩慢減小。當Idrain電流達到定義值(例如10mA)時,柵極電壓保存為Vth(down)。對電壓負值區域重複相同的測量步驟:最小柵極電壓-10V持續100ms。 然後柵極電壓逐漸增加,在10mA處保存Vth(up)電壓。

Vth測量完成後,測量測試對象的Rds(on)電阻。為此,在漏極和源極之間產生可調電流脈衝。通過測量漏極和源極之間的電壓降來確定Rds(on)電阻。完成這些測量後,繼續進行動態柵極應力測試。可靠實施該過程對準確表徵SiC半導體在應力下的行為並保障其可靠性至關重要。

DGS測量結果與靜態測量結果的比較

為評估DGS測試的必要性並將其與傳統靜態測試過程進行比較,進行了大量比較試驗。使用RDSon為80mΩ的常規1200V SiC MOSFET為測試對象。該過程使用的MOSFET均為最新一代產品,目前已在公開市場上銷售。使用數據表中在100kHz應力頻率和50%佔空比下的最大建議柵極電壓作為以下測試的應力參數。整個測試過程均在穩定的25 °C實驗室條件下進行。

對所得數據的分析表明,靜態和動態測試過程之間存在巨大差異(圖3)。

根據圖形可知二者差異顯著,特別在柵極閾值電壓漂移方面。動態測試中,經過300千兆週期後,柵極閾值電壓出現大於4V的明顯漂移。而靜態測試中未觀察到這種漂移效應。標準MOSFET的漂移約為0.5 V,而動態測試中的漂移較正常值高出7倍。對於多數電路而言,這種電壓升高可能會導致性能顯著下降甚至電路故障。SET GmbH在動態測試中多次識別到這些偏差; 但在靜態測試中未發現此類漂移。

此外,進一步研究了柵極閾值電壓的變化與RDSon電阻之間的關係。圖4則基於圖3中第一次測試的測量結果,明確説明了閾值電壓漂移和RDSon電阻之間的關係。可以假設,當柵極閾值電壓發生漂移時,RDSon電阻也會根據組件的特性數據曲線而變化。這一關係會在運行過程中影響組件效率,因此,也會對電動汽車行駛里程等實際應用造成影響。根據測試期間的連續測量結果來估計工作條件下的具體影響。

為不斷加深對SiC功率半導體現象的理解,應繼續進一步發展DGS測試和所有其他動態測試過程。特別是對於長期分析的建模,應收集儘可能多的數據,以便開發可靠的功率半導體來應對未來的挑戰。