PCIe路線圖讓人失去耐性?7.0爭奪戰已然打響!_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。1小时前

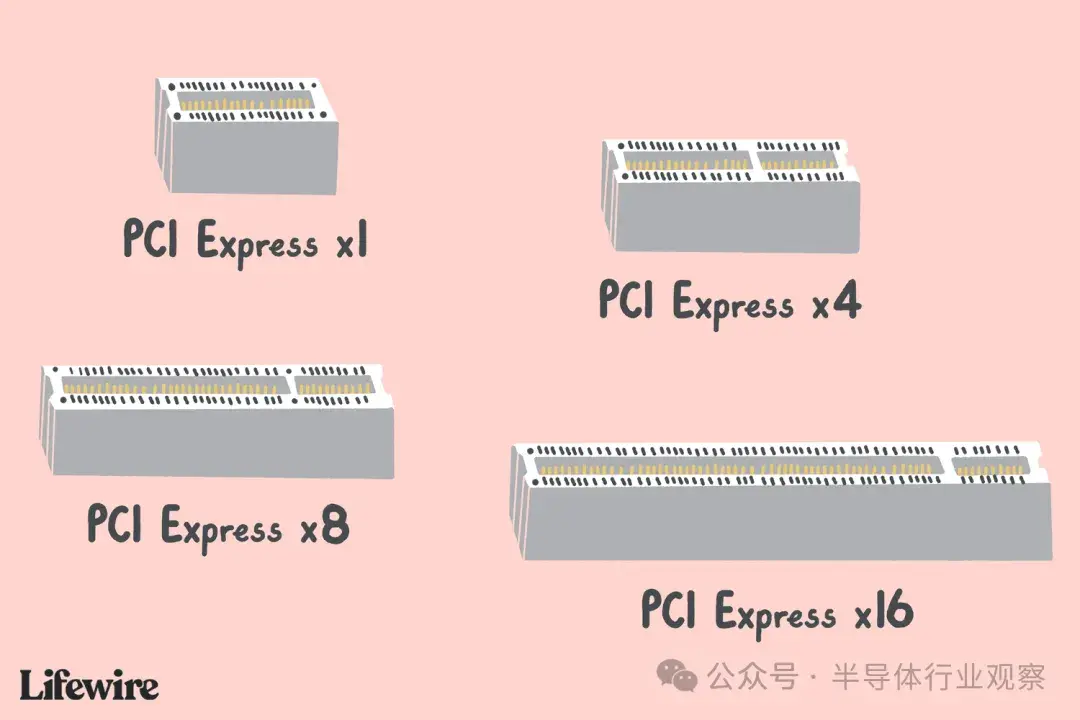

PCIe作為高速串行計算機擴展總線標準,現如今早已普及到每一台PC當中,不論是普通用户還是專業人士,不論是大型公司還是小型企業,都在享受這一項標準帶來的好處。

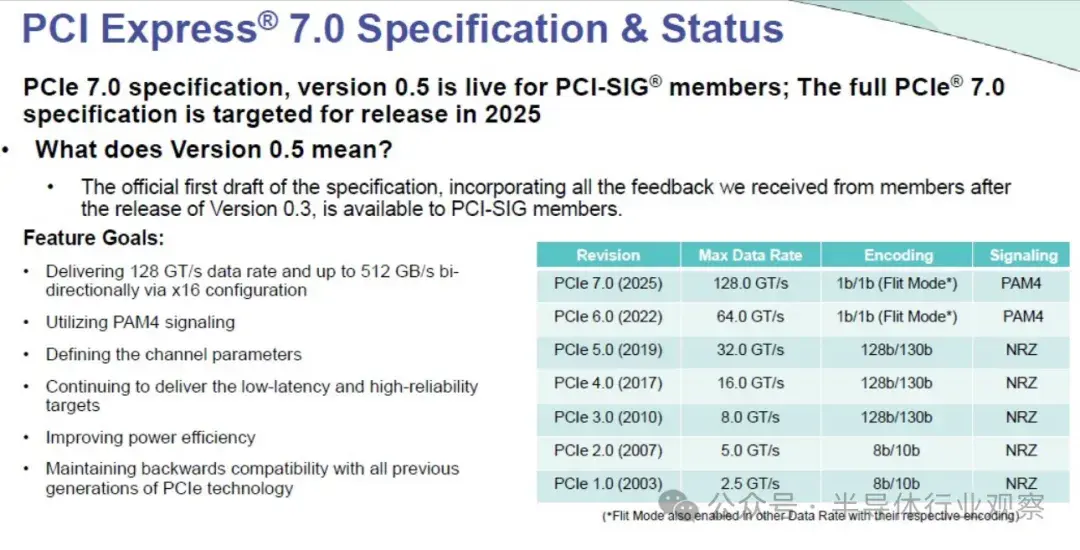

但這項歷史悠久的標準並非一成不變,在過去的二十餘年時間裏,它已經經歷了六次迭代,每通道的傳輸速率從2.5 GT/s升至128 GT/s,實現了翻天覆地的變化。第七代也穩步推進,一切看起來都欣欣向榮。

外媒Next Platform更是直言,PCI-SIG 需要加快其時間表,並努力使 PCI-Express 的路線圖與芯片製造商和服務器供應商的路線圖保持同步。對於同時擁有以太網、InfiniBand和Nvidia 專有的 GPU 內置 NVLink 的行業來説,這是一種廣泛使用的互連,預計隨着基於 CXL 的分層和共享主內存的使用增加,對 PCI-Express 的需求將會增加。

不過Next Platform也承認,一個擁有如此多成員的組織(目前大約有 970 個成員,並且還在不斷增長)以及針對每項規範的高度審議流程可能無法以速度為目的。規範有無數委員會和工作組,這可能導致各種變更、預 FYI 和 FYI 測試以及合規研討會。

所羅門在本週於加利福尼亞州聖克拉拉舉行的 2024 年 PCI-SIG 開發者大會上也告訴記者和分析師,所有這一切都需要時間。

然而,一場圍繞PCIE 7.0的爭奪戰,已然打響。

PCIe 7.0,即將到來

PCIe 7.0 是下一代計算機互連技術,旨在將每個引腳的數據傳輸速度提高至 128 GT/s,是 PCIe 6.0 的 64 GT/s 的兩倍,是 PCIe 5.0 的 32 GT/s 的四倍。這將允許 16 通道 (x16) 連接在每個方向同時支持 256 GB/秒的帶寬(不包括編碼開銷)。這樣的速度對於未來的數據中心以及需要更快數據傳輸速率(包括網絡數據傳輸速率)的人工智能和高性能計算應用來説將非常方便。

回看PCIe 7.0 的發展歷程,其早期工作從2022年開始。在當年的 PCI-SIG 開發者大會上, PCI-SIG 宣佈PCI Express (PCIe ) 7.0 的規範,到了2023 年會議上,PCI-SIG 已完成了規範的第一個草案版本 0.3,並在隨後分發給該組織的成員,這也標誌着PCIe 7.0 標準開發正式開始。

今年4月,PCI-SIG 向成員發佈了 PCI-Express 7.0 規範的 0.5 版,這是該規範的第二版草案,也是 PCI-SIG 成員向該標準提交新功能的最終呼籲,PCI-SIG 使用最新更新來重申新標準的開發仍在正常進行中2025 年最終版本。

翻看這個版本規格,PCI-SIG 將最高數據速率提高到每秒 128 千兆傳輸 (GT/s),提高了能效,並保留了與前幾代規範的向後兼容性。它還保留了從 PCI-Express 6.0 開始的 Flit Mode 編碼和 PAM4 信號。

“我們的主要工作是維持 PAM4 信號,維持我們為 PCI-Express 6.0 開發的 Flit 模式,所有這些,並且真正專注於速度翻倍,”Solomon 説。“將傳輸速度提高到每秒 128 千兆是重點。我們首先要保持向後兼容性。這是 PCI-Express 的重要組成部分。多年來,我們成功推出了所有 PCI-Express 規格。我們一直在努力提高能效,雖然我有點笑了,因為您會看到每秒 128 千兆的傳輸速度與我們原來的每秒 2.5 千兆的傳輸速度相比。是的,它比 2003 年消耗更多的電量。”

他説,功能平衡也很重要,並補充説:“PCI-Express 不一定是你能買到的最快的技術。它肯定不是最便宜的技術。但我們試圖實現這種最佳性價比的平衡——努力提供真正高的帶寬,真正合理的實施。因此,你為 PHY 選擇的硅技術就是你選擇的 PCB 技術。”

PCI-Express 7.0 還遵循了以前的規範,根據組織的產品需求為其提供一系列選項,如下表所示:

Solomon 表示,圖表頂部的通道數與硅片面積有關,並指出 16 條通道將比兩條通道佔用更多的硅片空間。但是,你可以用更便宜的工藝技術實現 16 條通道;兩條通道佔用的面積較少,但要實現 128 GT/s 可能需要更昂貴的硅片。“這只是給生態系統提供了選擇的機會,”他説。“你可以選擇帶寬,然後看看對你的特定產品來説什麼是重要的,然後選擇你想要的一個矩形。”

PCIe 7.0的下一個主要步驟是最終確定0.7版規範,該版本被認為是完整草案,其中所有方面都必須得到充分定義,並且電氣規範必須通過測試芯片進行驗證。本次規範迭代發佈後,無法添加新功能。PCIe 6.0 最終經歷了 0.3、0.5、0.7 和 0.9 4 個主要草案才最終定稿,因此 PCIe 7.0 很可能走在同一軌道上。

值得一提的是,去年夏天,PCI-SIG 宣佈將探索PCIe光纖連接的可能性。為此,PCI-SIG 光學工作組於 2023 年 8 月成立,旨在為連接器和收發器設計適當的外形尺寸,通過光波傳輸數據的光學連接技術有可能擴大 PCI Express 的應用領域,例如雲計算、高性能計算和量子計算等領域。與通過銅線傳輸相比,這有望實現更高的吞吐量、更低的延遲和更低的能源需求。

而在今年6月最新的PCI-SIG開發者大會上,該組織表示PCIe 6.0 規範的邏輯層和電氣層將接受新的光學 PCIe 標準化,PCIe 6.0 已經考慮使用光纖連接,這將改進當前的 PCIe 電氣系統,而不是取代它,這一變化很有可能會在PCIe 7.0中延續。

儘管控制器 IP 和初始硬件的開發工作已經在進行中,但當2025年PCIe 7.0標準最終確定後,第一個實際量產應用 PCIe 7.0 硬件還需要幾年時間才能正式和大家見面。

新的戰火已點燃

雖然PCIe 7.0的正式版本要到明年才會推出,但有些廠商早已準備好了自己的解決方案和IP,意圖在即將到來的新標準普及浪潮中搶先一步,拿下更多市場份額,在最近舉辦的PCI-SIG DevCon 2024上,各家廠商拿出了自己的最新技術,新的戰火已被點燃。

Alphawave Semi

在PCI-SIG DevCon 2024上,Alphawave Semi作為高速連接和計算硅片供應商,展示了用於快速實施下一代PCIe 7.0規範的 IP 子系統解決方案,以及為 PCIe 6.0 技術生態系統樹立新標準的先進技術。

Alphawave Semi主要展示了支持 DSP 的 PAM4 SerDes 技術,該技術為加快新興 PCIe 7.0 解決方案的上市時間奠定了基礎,其展示了完全集成的控制器和頂級 PAM4 SerDes PHY IP 如何為 AI 和高性能計算 (HPC) 數據中心應用帶來可互操作的 PCIe 6.0 技術連接。

Alphawave Semi表示,Silicon-Ready PipeCORE PCIe IP 在實現 PCIe 7.0 標準方面,能夠與 Tektronix DPO70000 高性能示波器配對,以 128 GT/s (PAM4) 的速度導航發射機性能,該解決方案以高度相關的模型和實驗室測量為後盾,保證以完整的 128 Gbps 解決方案快速進入市場。

此外,Alphawave Sem還展示了完整 PCIe 6.0 子系統解決方案,其具備突破每通道 64 Gbps 極限的電光鏈路,該集成包括 Alphawave Semi 的高級控制器 IP 和頂級 PAM4 SerDes PHY,以及 InnoLight 的 LPO OSFP 光學器件。其表示,這項技術可以為現代數據中心的性能、能效和延遲設定新基準,從而推動 PCIe 6.0 生態系統的發展。

新思科技

在PCI-SIG DevCon 上,新思科技展示了全球首個基於光學的 PCIe 7.0 IP,展示了該技術在實際場景中的功能。其中包括使用 OpenLight 光子 IC 以 128 Gb/s 運行的 Synopsys PCI Express 7.0 PHY IP 電-光-電 (EOE) TX 到 RX,以及使用 Synopsys PCIe 7.0 控制器 IP 成功實現根複合體到端點的連接和 FLIT 傳輸。

新思科技的 PCIe 7.0 IP 解決方案是高性能計算 (HPC) SoC 設計更廣泛的產品組合的一部分,其中包括適用於 1.6T/800G 以太網、CXL 和 HBM 的解決方案。據瞭解,新思PCIe 7.0 IP 解決方案的主要亮點包括:

完整解決方案:新思科技提供業界唯一完整的 PCIe 7.0 IP 解決方案,包括控制器、IDE 安全模塊、PHY 和驗證 IP。該解決方案在 x16 配置下可實現高達 512 GB/s 的雙向數據傳輸。

節能和低延遲:預先驗證的 PCIe 7.0 控制器和 PHY IP 與之前的版本相比,可提供低延遲數據傳輸,並且能效提高高達 50%,同時保持信號完整性。

安全性:Synopsys IDE 安全模塊適用於 PCIe 7.0,已通過控制器 IP 預先驗證,可提供數據機密性、完整性和針對惡意攻擊的重放保護,確保安全的數據傳輸環境。

經驗和可靠性:憑藉二十多年的 PCIe IP 經驗和超過 3,000 個設計成功案例,Synopsys 提供了一條低風險的硅片成功之路,為客户提供了強大而可靠的 IP 解決方案。

新思科技表示,該解決方案對於芯片製造商解決大型語言模型和計算密集型 AI 工作負載帶來的帶寬和延遲挑戰至關重要,公司的 PCIe 7.0 IP 解決方案支持安全數據傳輸,緩解 AI 工作負載數據瓶頸並實現生態系統內的無縫互操作性。

新思科技 IP 營銷與戰略高級副總裁 John Koeter 表示:“作為領先的接口 IP 提供商,新思科技不斷為設計人員提供最先進節點的最新接口,幫助他們滿足計算密集型設計的需求。新思科技的 PCI Express 7.0 IP 將為客户提供完整的、基於標準的解決方案,使他們能夠儘早開始下一代 HPC 和 AI 設計,並加速硅片的成功之路。”

Rambus

Rambus也在PCI-SIG DevCon上正式宣佈推出自己的PCIe 7.0 IP 產品組合,其中包括一套全面的 IP 解決方案:PCIe 7.0 控制器旨在提供下一代 AI 和 HPC 應用所需的高帶寬、低延遲和強大性能;PCIe 7.0 重定時器,用於高度優化、低延遲信號再生數據路徑;PCIe 7.0 多端口交換機具有物理感知能力,可支持多種架構;XpressAGENT TM幫助客户快速推出第一款芯片。

據瞭解,Rambus PCIe 7.0 控制器 IP 主要特性包括:支持 PCIe 7.0 規範,包括 128 GT/s 數據速率;實施低延遲前向糾錯 (FEC) 以實現鏈路穩健性;支持固定大小的 FLIT,可實現高帶寬效率;向後兼容 PCIe 6.0、5.0、4.0 等;藉助 IDE 引擎實現最先進的安全性;支持 AMBA AXI 互連。

Rambus 高級副總裁兼硅 IP 總經理 Neeraj Paliwal 表示:“隨着新型數據中心架構的出現,數據中心芯片製造商的格局正在蓬勃發展,因此需要高性能接口 IP 解決方案來培育強大而蓬勃發展的生態系統。Rambus PCIe 7.0 IP 產品組合通過提供無與倫比的帶寬、低延遲和安全功能來解決這一挑戰。這些組件協同工作,提供無縫、高性能的解決方案,滿足 AI 和 HPC 應用的嚴格要求。”

Cadence

Cadence同樣在最新的 PCI-SIG DevCon上展示了自己完整的 PCIe 7.0 解決方案,尤其是其 128GT/s SerDes IP 的接收器和發射器功能,展現出了出色的電氣性能和裕度。Cadence表示,自己的PCIe 7.0子系統測試芯片板可以通過外部環回模式配置的非重定時光電鏈路成功地發送和接收128GT/s信號,並留有多個數量級的餘量。

Cadence還在這次展會上做了多項演示,包括用於PCIe 7.0的Cadence IP在非定時光學上收發128GT/s信號的強大性能,使用示波器儀器測量Cadence IP for PCIe 7.0的能力,詳細説明其穩定的電氣性能和餘量,使用測試設備鑑定PHY接收器質量的PCIe 6.0接口Cadence IP的可靠性,以及符合PCI-SIG標準的PCIe 6.0 Cadence IP子系統,針對功耗和性能進行了優化。

Cadence表示,自己是第一家為 PCIe 3.0、4.0、5.0 和 6.0 提供完整子系統解決方案並具有行業領先 PPA 的 IP 提供商,公司很自豪能夠通過最新的 PCIe 7.0 IP 子系統解決方案延續這一趨勢,它為功耗、性能、面積和上市時間樹立了新的標杆。

從1.0到6.0的回顧

PCI 技術於 1992 年首次亮相,支持 133 MB/s 的峯值吞吐量和 33 MHz 的時鐘速度,並很快成為連接計算機系統組件的標準總線,隨後在 1998 年,PCI-X(PCI 擴展)提供了行業所需的更高帶寬,

2004 年,一羣英特爾工程師成立了 Arapaho 工作組,開始制定新的標準,後續,其他公司也加入了這一小組。在正式確定 PCI Express(PCIe)之前,新標準考慮過多個名稱。某種程度PCIe是 PCI 的繼承者,因為其具有類似的功能,但PCIe其實是一種完全不同於PCI 的設計。它更像是板上網絡,而不是 PCI 時代的眾多舊式並行接口,最終,行業在這一年成功走向PCIe 1.0標準。

最初的標準 PCIe 1.0a 每條通道的數據傳輸速率為 250MB/s,總傳輸速率為 2.5GT/s(每秒千兆傳輸),與其他串行總線一樣,性能通常以每秒傳輸次數來衡量,以避免將開銷比特算作 “數據”。PCIe 1.0a 採用 8b/10b 編碼方案,因此只有 80% 的傳輸位是真正的 “數據”。開銷比特有兩個主要功能。首先,它們確保串行接口始終有足夠的時鐘轉換來恢復時鐘。其次,它們確保沒有淨直流電流。

之後PCIe標準開啓了定期升級,其傳輸速率不斷提高。由於 PCIe 主要用於基於英特爾處理器的個人電腦和服務器,因此在實踐中,英特爾一旦發佈使用 PCIe 的處理器,新標準就會生效。該標準演變的總體思路是選擇可在當時主流工藝節點上製造的傳輸速率。不過,由於 PCIe 無處不在,因此無論底層架構如何,大多數需要高性能外設總線的設計都會使用 PCIe,例如Arm 服務器基礎系統架構規範中就規定了 PCIe 要求。

2007 年推出的 PCIe 2.0 將傳輸速率提高了一倍,但編碼方案保持不變,它的帶寬翻倍,且兼容PCIe 1.0標準,此外還改進了數據鏈路層的處理,支持更高效的電源管理,同時增強了數據完整性和信號傳輸的穩定性。

2010 年推出的 PCIe 3.0 改用了效率更高的 128b/130b 編碼方案,並增加了已知二進制多項式的擾碼功能,從而在時鐘恢復和無直流偏置方面實現了 0 和 1 的良好平衡。這也大大提高了傳輸速率,16 通道 PCIe 3.0 接口的傳輸速率最高可達 15.7 GB/秒。如今,PCIe 3.0 是已上市設備中部署最廣泛的 PCIe 版本。例如谷歌第三代 TPU 就使用了 PCIe 3.0,而目前普遍應用的 USB4 標準也基於 PCIe 3.0。

PCIe 5.0標準於 2019 年 5 月發佈,它帶來了 128 GBps 的吞吐量,同時提升了信號完整性和誤碼率(BER)控制,還支持了更高性能的設備,如用於人工智能和高性能計算(HPC)。該規範向後兼容前幾代 PCIe,英特爾是第一個在 CPU 上採用 PCIe 5.0 的公司,其推出的Alder Lake 平台就支持了PCIe 5.0標準。

定義 PCIe 標準的 PCI-SIG 曾預計 PCIe 4.0 和 PCIe 5.0 將在一段時間內共存,PCIe 5.0 用於需要最大吞吐量的高性能需求,例如用於 AI 工作負載和網絡應用的 GPU。因此,PCIe 5.0 將主要用於數據中心、網絡和高性能計算 (HPC) 企業環境,而強度較低的應用(例如台式電腦使用的應用)則可以使用 PCIe 4.0。

2022年發佈的也是目前最新的PCIe 6.0標準帶寬再次翻倍,顯著提升至每通道8 GB/s,其在互連方面也實現了巨大的變化:

PAM-4電信號調製方案:不再使用傳統的不歸零(NRZ)信號,而是採用具有四種電壓電平的脈衝幅度信號,能夠產生三眼眼圖。預編碼和前向糾錯(FEC)可以分別減少模擬誤差和數字誤差。該方案能夠以低延遲提供64GT/s的帶寬。

流量控制單元(FLIT)數據包傳輸:這種新的數據包傳輸架構(FEC要求採用該架構)不僅支持增加的帶寬,而且還使系統能夠處理增加的帶寬。

L0p低功耗狀態:當系統中的帶寬需求降低時,新的L0p低功耗狀態允許一些通道進入睡眠模式,從而能夠優化功耗,同時又確保鏈路始終保持開啓。

數據完整性和安全保護:該規範在較低的帶寬級別上使用數據對象交換(DOE)作為PCIe安全構建塊,並使用加密數據和密鑰。組件測量認證(CMA)提供固件加密簽名。完整性和數據加密(IDE)為系統提供數據包級別的安全防護,以防止物理攻擊。通過將IDE與控制器耦合,它可以在64GT/s的高帶寬速度下提供高效的安全防護。

雖然我們在不遺餘力地推廣新技術,但我想問個問題,我們還要多久才能看到PCIe 6.0的產品正式問世呢?