DAC 61週年 | 日觀芯設攜一站式數字後端籤核平台重磅亮相_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。1小时前

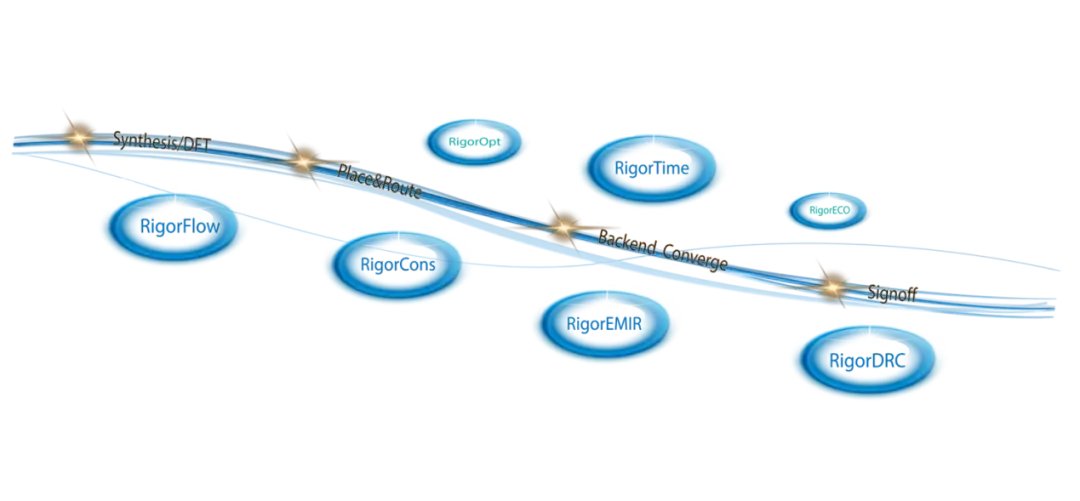

2024年6月23-27日,在一年一度的全球電子設計自動化盛會DAC(Design Automation Conference)上,面向來自世界各地的業內頭部芯片設計廠商 ,作為EDA籤核領域的後起之秀上海日觀芯設自動化有限公司(Rigoron),屆時將攜全新升級的一站式數字後端籤核工具系列重磅亮相61屆DAC會議,並隆重發布並現場展示數字籤核領域的一系列產品:

IC設計全流程管理軟件RigorFlow 2.0時序約束驗證與管理軟件RigorCons靜態時序分析軟件RigorTime物理驗證及籤核軟件RigorDRC功耗分析及籤核軟件RigorEMIR

RigorFlow是日觀芯設旗下一款創新的管理芯片設計全流程的EDA/CAD軟件,旨在解決集成電路(IC)設計流程中多種難題與痛點,並大幅提升IC設計工程師的工作效率以及開發團隊整體管理效率。

此次亮相DAC的RigorFlow 2.0在其前身1.0版本的基礎上,進行了全面升級,特別是強化了實時數據存儲與可視化統計分析功能。這一新功能使用户能夠直觀地比較不同設計方案的性能和效率,進而制定出更加科學、高效的設計決策,顯著提升項目成功率。

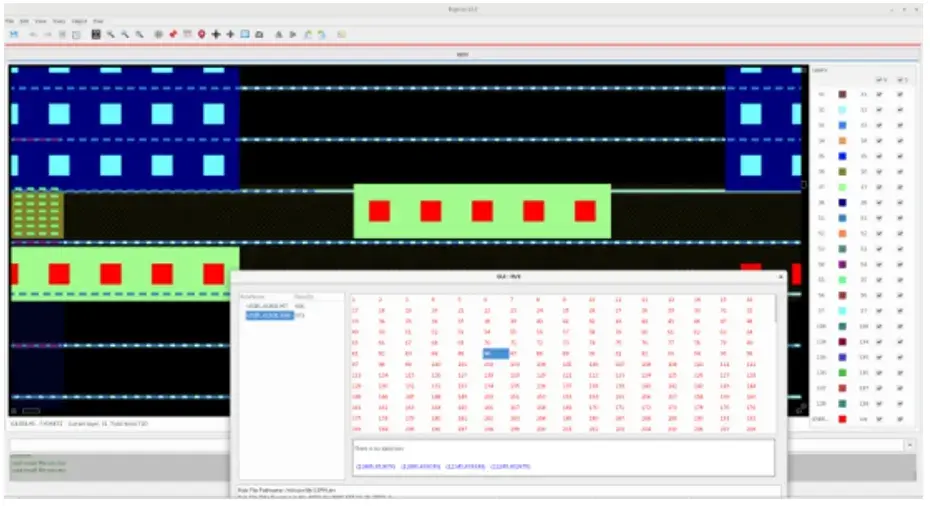

圖1:RigorFlow2.0數據對比與可視化統計分析

RigorFlow2.0還為複雜的工作流程管理提供一整套完備系統,它包括了:運行狀態監控管理器、清晰明瞭的圖形化流程管理、多維度可視化統計分析、超大吞吐容量、先進的分佈式架構、透明的團隊協作。

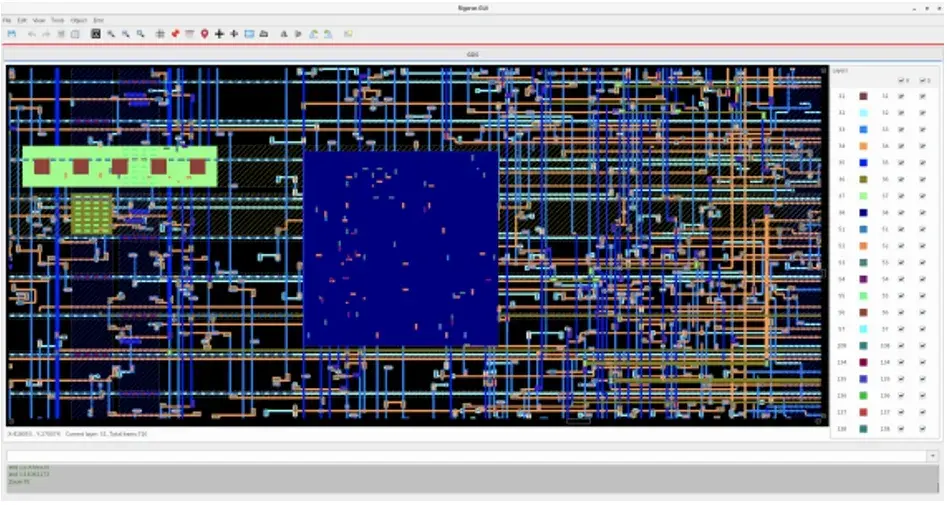

另一方面,RigorDRC 也是我們推出的一款重要里程碑式的物理驗證工具。它能夠快速而準確地檢測和糾正電路設計中的物理錯誤,支持互連線 、單元/ 器件的設計 規則檢查等。具有支持先進工藝節點的能力、.運行效率高於國外同類工具,更適宜於處理超大規模的版圖,包含友好的圖形界面工具,便於設計者快速修復發現的設計違例之處。

圖2:RigorDRC GUI界面

此外,我們的RigorCons產品正在重點客户的定點試用中。RigorCons是一個強大的時序約束驗證和管理工具,它可以幫助驗證SoC、5G、GPU、CPU等芯片中的複雜SDC時序約束。為任何層次結構和模式自動生成和管理SDC,從而顯著縮短時序收斂週期,保證籤核的質量和效率。

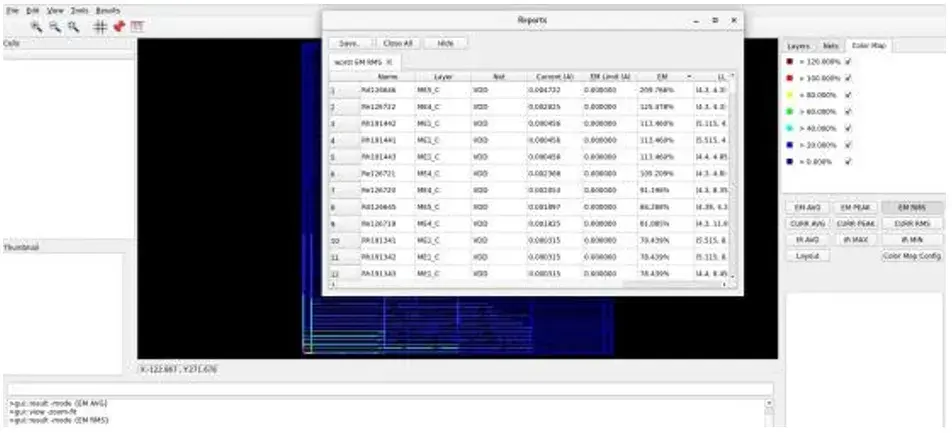

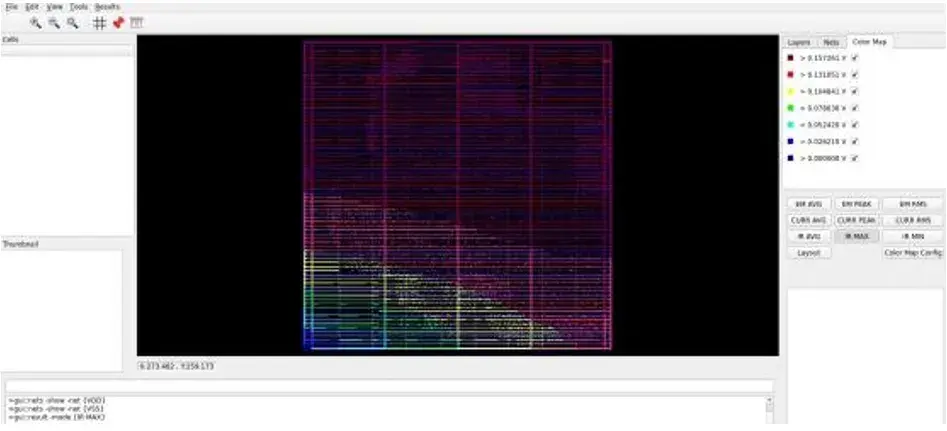

與此同時,在本次DAC展會中日觀芯設也將宣佈,經過了過去一年半日觀EMIR團隊的努力,旗下功率分析和EMIR等技術產品將於下半年推出市場。

圖3:RigorEMIR GUI界面

對於日觀芯設於本屆DAC中即將展示的一站式數字後端籤核工具系列,許多即將參會的業界領袖都表現出了濃厚的興趣。他們期待這些新產品能帶來更高性能的設計驗證,為未來的創新打開更廣闊的可能性。

在此,日觀芯設將熱忱得歡迎您在DAC 展會期間參觀日觀芯設的展台(展位號:1552),親自體驗我們的一站式數字後端籤核工具系列。我們將現場答疑和研討,與業界專家和客户分享我們的最新成果和見解。

最後,希望在此次DAC展會上,能和客户以及業界專家進行深度交流和學習,同時也為日觀帶來了新的合作機會和可能性,與更多的夥伴共享資源、共贏市場。