NoC技術,重煥新生_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。25分钟前

數十年來,在摩爾定律的推動下,集成電路工藝取得了高速發展,單位面積上的晶體管數量不斷增加。

SoC憑藉集成度高、功耗低、成本低等優勢,已成為大規模集成電路系統設計的主流方向,解決了通信、圖像、計算、消費電子等領域的眾多挑戰性的難題。

隨着應用需求越來越豐富,SoC需要集成越來越多的不同應用的IP,片上多核系統MPSoC也已經成為必然的發展趨勢。

以數字電視的SoC芯片為例,包含了運行操作系統和應用程序的CPU,處理音頻編解碼的DSP,處理圖形相關任務的GPU,處理AI圖像算法的NNA,以及一些視頻編解碼、後處理等專用模塊,以及視頻信號的調制解調器等,一個複雜的SoC系統上有各種功能模塊IP。

在複雜的異構計算生態系統中,採用多個不同IP的複雜組合對片上通信提出了更高的要求,同時片上服務質量、仲裁和數據流優化的複雜性越來越高,傳統的片上互連方法已經無法適應時代的變化。

對此,片上網絡互連技術(NoC)日益成為行業關注的焦點,旨在提供一種解決芯片內不同IP或者不同核心之間數據傳輸的片上通信方案,成為連接多個處理單元和外設的關鍵。

為什麼説NoC是****多核系統的最佳互聯機制?

片上網絡互連(Network-on-Chip,NoC)是集成電路上的一種基於網絡的通信子系統,用於SoC中的模塊之間,基於路由器的分組交換網絡,連接SoC各模塊。

NoC技術作為一種分佈式、高度並行的通信架構,通過網絡化的方式連接處理器核心、內存和各種外設,大幅提高了數據傳輸效率和通信帶寬。其設計不僅需要考慮高帶寬、低延遲,還需要兼顧功耗、面積和可靠性等多方面因素。

在介紹NoC之前,我們先來看一下片上互聯技術近些年來的發展歷程,主要可以分為三個階段:

**共享總線(Bus):**傳統的SoC片上通信結構一般採用共享總線的方式。在此結構中,所有處理器和IP模塊共享一條或多條總線。當有多個處理器同時訪問一條總線時候需要有仲裁機制來決定總線的所有權。

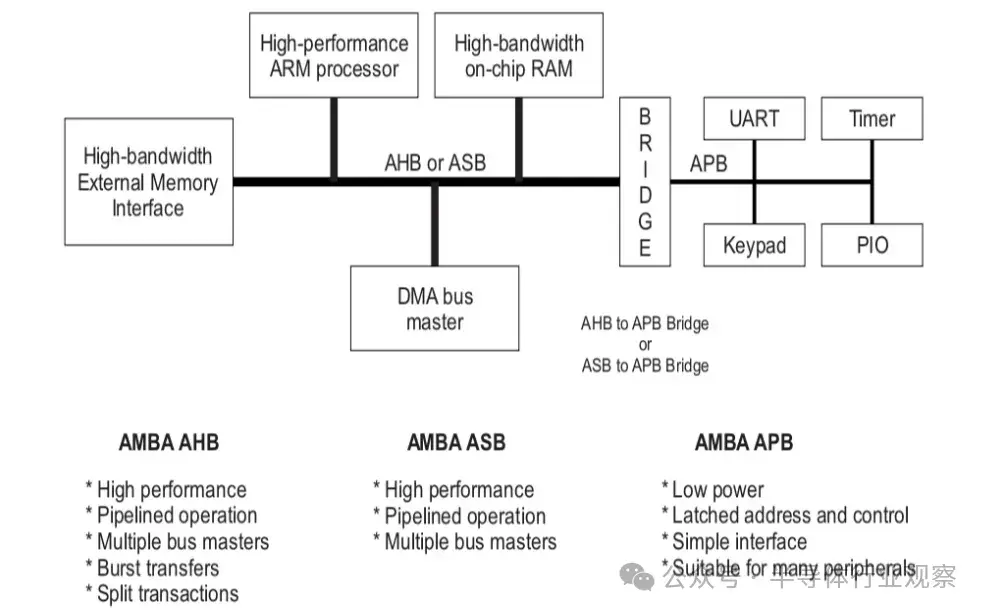

共享總線片上通信系統結構一般比較簡單,硬件代價也小,但帶寬有限,而且帶寬也沒法隨着IP的增多而進行擴展。ARM公司在1996年提出的AMBA總線廣泛應用於嵌入式微處理器的片上總線,現已成為事實上的工業標準。

可以認為,Bus是最簡單的互聯,一般適用於十個以下互聯設備的小系統。

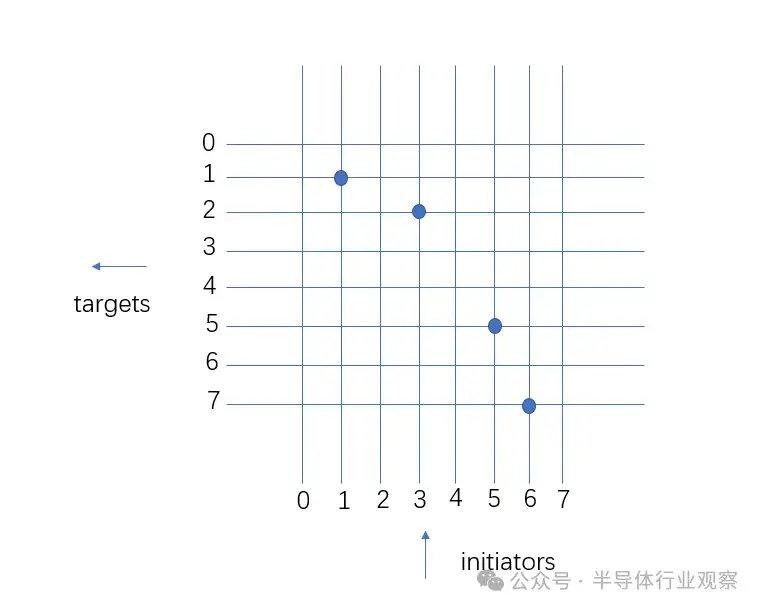

**交叉開關矩陣(Crossbar):**傳統的共享總線面對多個處理器同時訪問不同IP的情況時,因為需要仲裁機制去決定總線所有權,所以這種方式在此情況下就會造成一定瓶頸,導致訪問的延時。對此,為了滿足多處理同時訪問的需求,並提高整個系統的帶寬,一種新的解決方案Crossbar孕育而生。

Crossbar保證了多路通信同時進行的實時性,只要不是訪問同一個目標設備,就不需要用到仲裁,大大減少了因為仲裁帶來的瓶頸問題。但是隨着設備數的增加,Crossbar的規模會以幾何級數增長。所以通常我們通過橋接設備去級聯多個Crossbar來支持設備的擴展。但是橋接設備可能會成為系統的瓶頸,增加傳輸的延遲。

相較於Bus適合小系統,Crossbar適合不太大的系統,一般用於幾個到十幾個connected nodes的系統。

能看到,傳統共享總線和Crossbar架構各有優勢。在實際應用中,業界通常採用Crossbar和共享總線相結合的方式,用橋接器將Crossbar網絡和共享總線網絡連接起來,形成一個典型的混合型拓撲結構。

然而,儘管業界已經提出了很多改進的總線結構,但隨着進入MPSoC時代,總線結構在通訊性能、功耗、全局時鐘同步、信號完整性以及信號可靠性等方面面臨着巨大的挑戰,這些複雜的改進型總線結構仍無法解決片上多核間通信所面臨的問題。

因此,MPSoC上多核間的通信問題已經成為制約系統性能提升的主要瓶頸。

為此,片上網絡技術(NoC)應運而生,逐漸取代Bus和Crossbar,成為片上互連的行業標準。

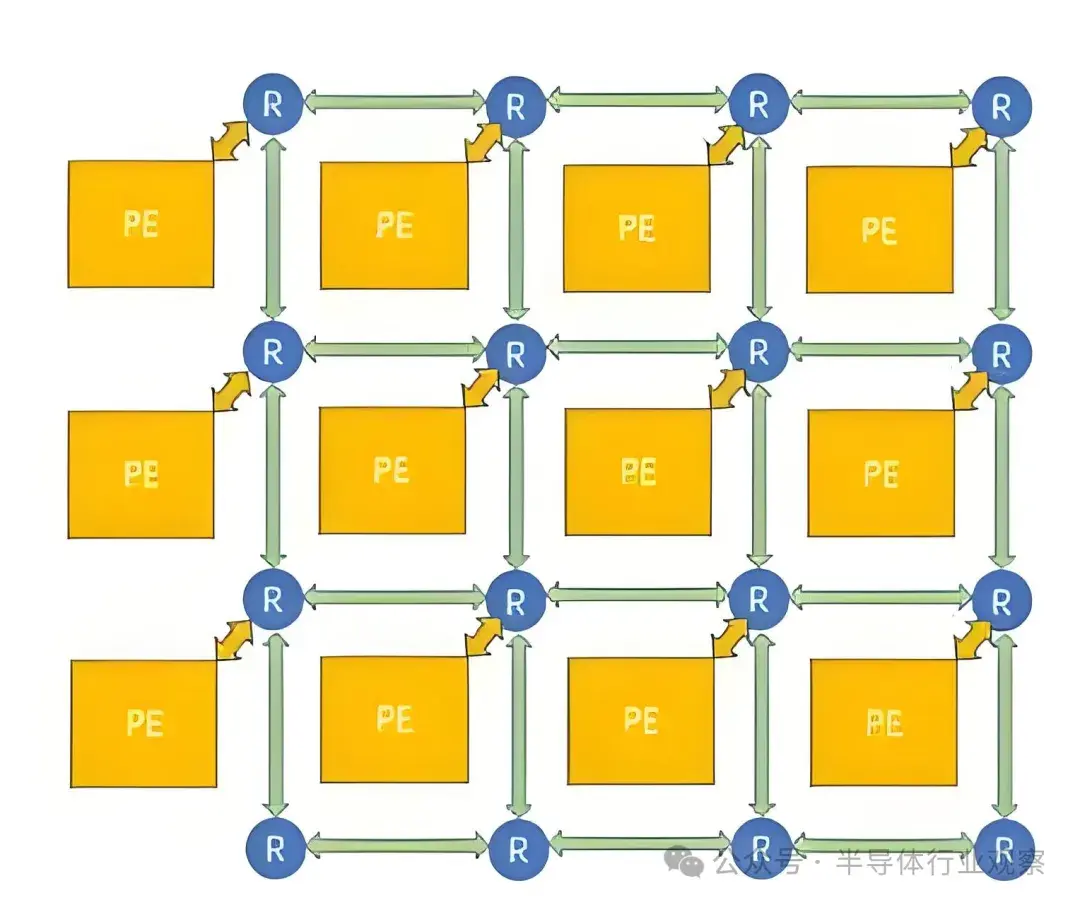

如圖所示,NoC結構中的R表示Router,所有的Router可以是同步,但每個Router所連接的PE(Processing Element)與Router異步,自成一個時鐘域。所以基於NoC的系統能更好地適應在複雜多核SoC設計中使用的全局異步局部同步時鐘機制。

在NoC架構中,每一個模塊都連接到片上路由器,模塊傳輸的數據則是形成了一個個數據包,通過路由器去送達數據包的目標模塊,多個通信流在這些鏈路上進行多路複用。

通常,NoC由多段佈線和路由器組成,這些佈線和路由器的佈置旨在減少寄生效應,從而避免在整個SoC中更大的損失和延遲。這通常採用類似城市佈局的網格結構的形式。

在NoC中,路由節點之間通過局部互連線相連接,每一個路由節點通過網絡接口NI與一個本地IP核相連接,源路由節點和目的路由節點之間的數據通訊需要經過多個跳步來實現。因此,NoC技術的出現使得片上系統SoC的設計也將從以計算為中心逐漸過渡到以通信為中心。

NoC技術不僅提供了高帶寬、低延遲、低功耗的通信,還為複雜的SoC系統提供了可擴展性和靈活性,以及信號完整性和信號延遲等方面的優勢。

整體來看,NoC使得在芯片內部的異構計算單元之間能夠高效地傳輸數據,同時最大限度地減少所需的資源,不僅可以幫助優化資源利用,還可以保持分佈式計算單元之間的數據一致性,對於複雜的設計尤為重要。

NoC本質上就是提供一種解決芯片內不同IP或者不同核心之間數據傳輸的片上通信方案,可以克服基於傳統總線網絡和Crossbar的帶寬瓶頸。通過採用高效的內部通信架構和靈活的互聯方式,NoC可以憑藉高性能、低功耗、可擴展性和可靠性等優勢,為未來的人工智能、物聯網、自動駕駛、數據中心等新興領域的發展提供重要的支撐。

因此,NoC被視為當前多核系統的最佳互聯機制。

國產廠商,擠進NoC賽道

大到巨頭,小到初創企業,如今都開始把NoC作為關鍵技術推進,成為未來多核/眾核處理器的核心之一。

隨着2018年英特爾收購NoC IP供應商Netspeed;2019年Meta收購另一家NoC公司Sonics;2020年,Arteris作為大股東,在中國合資設立傳智驛芯(Transchip),逐漸鋪開中國業務。片上網絡技術漸漸再次迴歸人們的視野。

至此,雖然市面還有SignatureIP、Truechip等玩家,但方案比較全的NoC IP公司基本只有Arteris一家了。不過,Cadence、開芯院、賽昉科技等企業近年來也在相繼入局,取得了一定進展。

Arteris:NoC IP一家獨大

Arteris是領先的系統IP提供商,其NoC互連IP和SoC集成自動化技術致力於加速當今SoC芯片的開發。

Arteris片上網絡互聯IP產品:

FlexNoC Non-coherent NoC IP – 具有物理感知的片上網絡IPNcore Cache-coherent NoC IP – 通過提供安全支持解決多核設計挑戰CodaCache Last-level Cache IP – 通過無差錯的系統內存映射加快產品上市時間

去年,Arteris推出Arteris FlexNoC 5物理感知NoC互連IP,使SoC架構團隊、邏輯設計人員和集成商能夠整合跨功耗、性能和麪積(PPA)的物理約束管理,以提供連接SoC的物理感知IP。

據介紹,對於汽車、通信、消費電子、企業計算和工業應用,該技術使佈局團隊的迭代次數更少,物理收斂速度比手工優化快5倍。

此外,FlexNoC 5擴展了對Arm AMBA 5協議和IEEE 1685 IP-XACT的支持,包括與Arteris Magillem的連接流程,用於與其他SoC IP 模塊的NoC集成。FlexNoC 5還支持經過生產驗證的用於汽車功能安全認證和數據中心可靠性的Arteris彈性選項,用於優化內存流量的高級內存選項,以及用於超大型設計的Arteris選項。

據2023年底信息披露,Arteris公司的互連IP和系統IP已被600多家SoC設計公司所選用,全球已有超過30億顆利用其IP的SoC 應用在各種電子系統中。

隨着其經過硅驗證的IP的聲譽不斷擴大,Arteris在過去兩年中獲得了65+新客户,已經有不少AI芯片、服務器芯片、汽車芯片廠商都和Arteris達成了合作。僅在2023年,就有SiFive、Tenstorrent、Axelera AI和ASICLAND等公司與其達成了授權合作。海思、瑞芯微、全志等國內移動芯片廠商,包括博世、NXP、瑞薩、地平線和上面提到的Mobileye等汽車芯片廠商,也都曾在其SoC設計中應用了Arteris的FlexNoC IP,持續幫助客户提升性能、降低功耗和麪積、提高設計複用效率、加快 SoC 開發速度,從而幫助降低芯片的開發生產成本。

現在其IP已經用於70%的汽車ADAS SoC中。然而,商用NoC不僅僅應用於汽車市場,包括通信、消費電子和工業在內的其他領域正在尋找經過硅驗證的系統IP解決方案,以縮短上市時間、優化工程資源並提高SoC經濟性。

隨着第五代FlexNoC技術FlexNoC 5的推出,Arteris未來幾年註定會在更多最先進SoC設計的開發中發揮重要作用。

同時,Arteris還有用於保證緩存一致性的Ncore、降低DRAM讀寫次數的CodaCache等一眾SoC設計。Arteris的IP對處理器架構支持非常廣泛,主流的ARM、RISC-V、ARC、MIPS等都已經達成支持。

**傳智驛芯:聯手Arteris,**以NoC技術駕馭複雜SoC設計

國內第三方NoC IP供應商比較少,傳智驛芯恰好出現在行業最需要的時候。

傳智驛芯成立於2020年,是Arteris在中國的合資公司,核心業務包括基於NoC技術開發設計的解決方案、子系統IP開發、芯片設計服務等。在子系統IP開放方面,傳智驛芯,依託Arteris IP打造了TC x NoC、Safety lsland以及Die to Die三大產品矩陣,主要面向汽車芯片、GPU/AI芯片、RISC-V芯片以及FPGA芯片等芯片廠商。

未來,隨着芯片內部晶體管數量會持續上升,片上系統SoC的性能需求越來越高,NoC將勢必成為多核/眾核處理器的關鍵技術。同時,國內市場對於NoC IP擁有有多樣化需求,要求企業可以根據不同需求進行修改定製。傳智驛芯科技將繼續與Arteris強強聯合,以NoC IP服務、子系統IP開發、芯片設計服務等業務紮根中國市場,從而加速國產SoC處理器芯片設計。

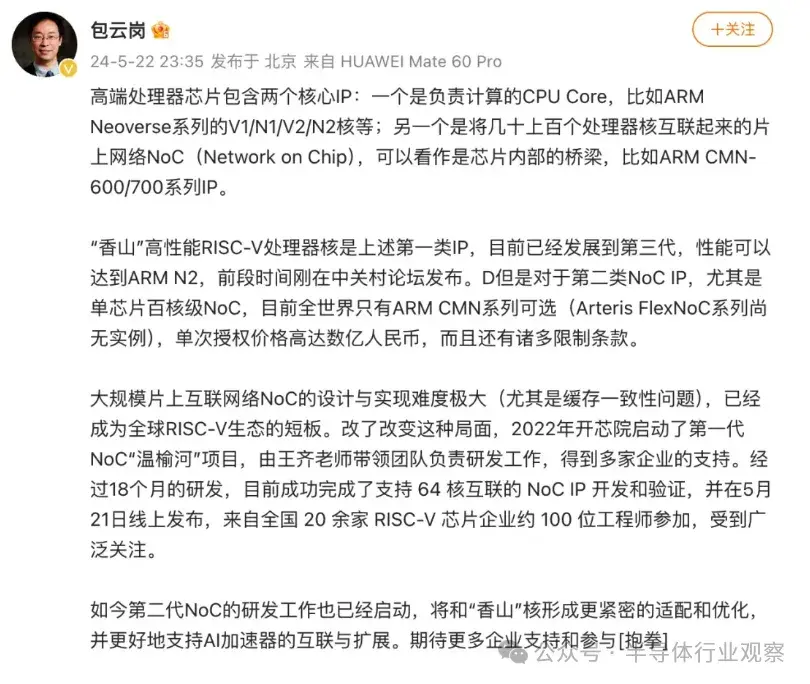

開芯院:發佈全球首個開源NoC IP

2024 年 5 月 21 日,開芯院發佈全球首個開源大規模片上互聯網絡(NoC)IP,代號“温榆河”,這一重大突破標誌着開芯院在推動數據中心服務器芯片技術發展方面邁出了堅實的一步。

據介紹,開芯院自項目成立以來,經過18個月的緊張開發,成功完成了支持64核互聯的NoC IP開發和驗證。“温榆河”NoC IP的發佈進一步推動了RISC-V生態的發展,並使得開芯院能夠提供數據中心服務器CPU芯片的核心基礎IP,包括“香山”高性能處理器核和“温榆河”大規模片上互聯網絡。這是全球首次基於開源項目完成數據中心服務器CPU芯片的構建,具有重要的產業價值。

這一突破創新,不僅為行業帶來了更多選擇和靈活性,還極大地增強了RISC-V產業生態的信心,是全球開源芯片生態的重要里程碑。此次發佈會吸引了來自全國20餘家RISC-V芯片企業約100位工程師參加,受到廣泛關注。

此外,開芯院正在研發第二代NoC,並與“香山”核緊密適配優化,支持AI加速器的互聯與擴展,期待更多企業支持和參與。

開芯院首席科學家包雲崗對“温榆河”項目的相關背景也進行了補充介紹:

近日,Cadence宣佈擴充其系統IP產品組合,新增了Cadence Janus Network-on-Chip(NoC),以優化電子系統連接性。

據介紹,Cadence Janus NoC 能夠以極低的延遲高效管理這些同步高速通信,幫助客户以更低的風險更快地實現其 PPA 目標,節約寶貴的工程資源,傾力打造SoC的差異化功能。

Cadence Janus NoC可有效應對與當今複雜的SoC互連相關的佈線擁塞和時序問題,這些問題在物理實現之前往往並不明顯。Cadence的第一代NoC不僅能滿足當前最迫切的需求,還提供了一個有利於未來的創新平台,例如支持行業標準存儲器和I/O一致性協議。目前該產品提供的功能和優勢包括:

易於使用:Cadence擁有功能強大、設計先進的圖形用户界面(GUI),可輕鬆支持從小型子系統到完整SoC和未來多芯片系統的NoC配置。加快產品上市:RTL針對PPA經過優化,使SoC設計人員能夠實現帶寬和延遲目標。封包化信息可提高線路的利用率,減少線數量,降低時序收斂難度。降低風險:NoC的內置功耗管理、時鐘域交叉和寬度匹配功能有助於降低設計複雜性。快速設計週轉:Cadence廣泛的軟件仿真和硬件仿真能力可實現早期架構探索,以便於快速驗證PPA結果,確保配置滿足設計要求。可擴展架構:客户可以設計一個子系統,並在NoC的完整SoC環境中重複使用,以便將來在多芯片系統中重複使用。靈活:Cadence NoC兼容任何具有行業標準接口的IP,包括AXI4和AHB。

值得注意的是,Cadence Janus NoC依託Cadence值得信賴且久經考驗的Tensilica RTL生成工具。客户可以使用Cadence廣泛的軟硬件產品組合對其 NoC 進行軟件仿真和硬件仿真,並使用 Cadence的系統性能分析工具(SPA)深入瞭解 NoC 的性能。該流程支持架構探索,有助於實現可滿足產品需求的最佳NoC設計。

NoC依託Cadence在IP和設計質量領域久負盛名的領導地位,由客户滿意度遙遙領先的技術團隊提供技術支持。

Arm

Arm一向擁護開放標準,因為這有助於龐大生態系統中的合作伙伴在使用Arm AE IP設計時能夠蓬勃發展,同時還能提高可移植性和軟件複用率。

一個典型的例子是在Arm與Arteris的合作,在這個合作中,Arteris通過使用Arm全新的CPU IP驗證了他們的互連產品(NCore和FlexNoc)。雙方針對AMBA5 CHI.E標準進行Arm CPU和Arteris Ncore的組合驗證。這項驗證為生態夥伴採用Arm IP組合來構建其特定專用的SoC解決方案增添信心。

除了第三方NoC IP之外,如果是Armv9架構的話,也有CoreLink NI-700這一NoC互聯方案,可以與Arm CPU、GPU和NPU IP完美搭配,相比傳統的Crossbar方案可將線束減少30%。不過在汽車SoC的IP集成上,Arm和Arteris也是合作關係。

Arm的CoreLink互連可生成面向Arm Cortex和Mail內核定製的針對緩存一致性CMP和移動SoC的總線和mesh網絡。

賽昉科技

據瞭解,昉·星鏈-500是賽昉科技首款自研的支持緩存一致性的Interconnect Fabric IP,支撐構建多核CPU和SoC,提供緩存一致性NoC,通過連接多個CPU Cluster、IO設備和DDR,並在SoC範圍內維護緩存的一致性。

賽昉科技作為全球領先的RISC-V計算平台提供商,不僅提供了高性能內核和高能效內核,還提供了高速的一致性NoC、RISC-VTrace/Debug調試接口、RISC-V中斷控制器、功耗管理、安全管理、虛擬化、IO一致性和內存子系統等全面的解決方案。這些解決方案將幫助客户實現嵌入式、客户端、服務器和高性能計算等多個場景的芯片落地。

從行業現狀來看,擁有NoC IP的玩家並不多,大多都是擁有處理器IP核的配合使用,比如Arm、Intel、Meta、高通、英偉達、Achronix等。

寫在最後

未來,多核處理器的規模會更大,尤其是在摩爾定律放緩的基礎上,提升算力很大程度上要靠在芯片內部堆積更多的核,這些核心可能使用不同的架構,這種異構多核的數量和複雜度都會增加。

隨着芯片設計日趨複雜,NoC已成為實現異構計算組件之間高效數據通信的重要組成部分。在AI、邊緣計算、汽車芯片、數據中心和雲端等不同領域中,NoC技術正在起到關鍵作用。

然而,在當前火熱的3D IC和小芯片(Chiplet)集成方面,NoC技術還需要不斷演進以適應新的挑戰和需求。

3D芯片設計是多個芯片垂直堆疊在一起的設計,為 NoC 架構帶來了新的挑戰和機遇。在3D設計中,芯片的垂直集成可顯著縮短通信距離和延遲,但同時也需要重新考慮 NoC拓撲和協議,以充分利用三維結構的優勢。

大型、複雜的多核Chiplet同樣需要新概念來實現內核、內存和外設之間的高級通信。這樣的通信結構必須是分層的,為芯片內和芯片間通信分別設計不同的NoC,這樣可以更好地管理複雜性和安全性。

整體來看,無論是ChatGPT的爆紅、汽車芯片的潛力,還是3D IC與小芯片的興起,都在催生更高性能SoC芯片、更多核異構處理器的發展和演進,隨着半導體工藝技術的進步和芯片集成度的提高,NoC的設計已成為現實,並展現出非常廣闊的前景。

這個誕生於20多年前的技術,時至今日才逐漸爆發出生命力。

Achronix資深現場應用工程師黃侖:片上網絡 (NoC) 技術的發展給高端FPGA帶來的優勢;

Cadence:Cadence擴充系統IP產品組合,推出NoC以優化電子系統連接性;

逍遙設計自動化:駕馭三維芯片設計中不斷演變的片上網絡(NoC)體系結構;

北京開源芯片研究院:開芯院發佈全球首個開源大規模片上互聯網絡IP“温榆河”;

IP與SoC設計:片上網絡入門;