硬核國產EDA,已跨入智算創新時代_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。47分钟前

在算力即國力的智算時代,算力芯片設計規模和複雜度大幅提升,封裝、工藝和系統設計也都面臨着前所未有的挑戰。尤其恰逢日益激烈的競爭態勢、日趨嚴苛的投資環境以及風險劇增的地緣政治帶來的疊加影響,國產EDA面臨着多重且緊迫的時代考題。與此同時,EDA行業自身的特點也帶來了諸多挑戰,如較高的技術壁壘、專家人才的緊缺以及實際部署的迭代演進等。

為此,本土EDA從業者也正在思考,如何能將國產EDA工具推向先進水平,並在國際競爭中佔據一席之地。特別是在以人工智能驅動的智算時代科技比拼的當下,EDA工具對於支撐中國智算時代驅動的集成電路產業發展至關重要。

面對這些挑戰,國產EDA需要持之以恆的攻堅,則無旁騖的專注技術創新,堅持以客户為中心,加速產品迭代,以應對變化並抓住機遇。

智能時代,對國產EDA提出新需求

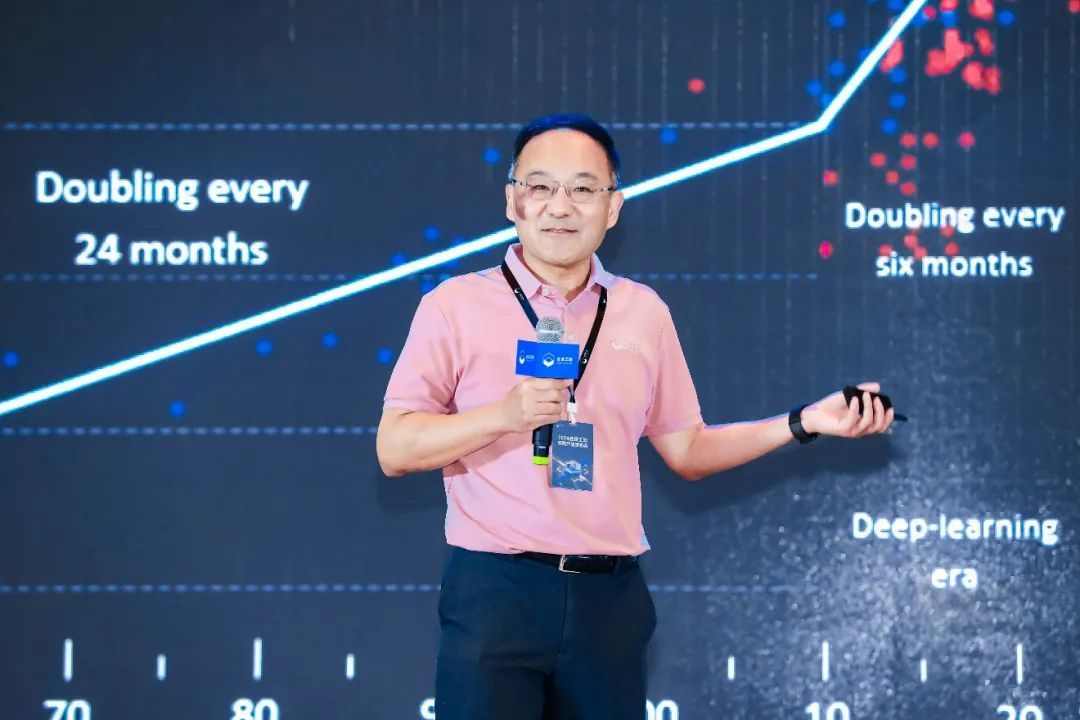

生成式AI引爆了智算產業的高速擴張,算力已成為數字時代的關鍵源動力,也是國家科技實力的基石與體現。智算系統中,芯片為整個架構提供算力基礎支撐,每一次大模型的訓練和推理參數量正在呈現指數級增長,帶動着作為算力基礎設施的算力芯片GPU和CPU芯片爆發式的自主化需求。同時,智算領域為芯片設計也帶來了多重挑戰,芯片的複雜度呈現大幅的提升,嚴苛的面世時間要求設計和驗證工作更加準確而高效,對系統級設計及軟硬件協同的要求也更為複雜。這些新的挑戰顛覆了既往的傳統芯片設計方法,同時持續推升EDA工具研發的複雜度。

以GPU、AI芯片為主的智能算力,效率更高,滿足大量數據的併發處理需求,採用400G/800G高帶寬,低延遲的網絡,支持大量數據傳輸。同時海量算力需求依託 AI 服務器,增配高算力 GPU 芯片。在系統級,PCB 作為算力芯片基座與信號傳輸通道,對服務器性能提升至關重要。

智算時代的爆發對國產EDA的支撐提出了嚴苛的時間表,時不我待。為了迎接智算時代帶來的高需求推動力,國產超算/智算芯片行業面臨着設計、工具與製造多重限制,以及複雜的系統的應用軟硬件需求,和非常嚴苛的產品面世時間。中國芯片設計領域對EDA的需求已經不同於往日, 如何破局給整個產業鏈帶來了全新的挑戰,國產EDA產業作為芯片行業的核心環節,既面臨嚴峻挑戰,也迎來了巨大發展機遇和廣闊成長空間。

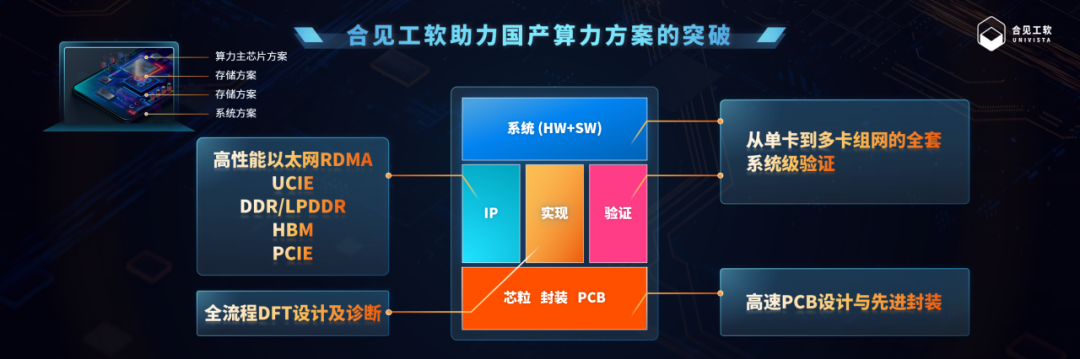

以上種種因素,都驅動着中國高端數字芯片設計面臨三個迫切的需求:第一、毫無疑問的國產EDA工具問題;第二、系統級上改善芯片性能,以及解決軟硬件協同的挑戰,從更早期的階段開始系統聯動設計的考量;第三,更好的支撐國內數字大芯片客户的需求,包括芯粒(Chiplet)時代所帶來的最新高速接口IP和系統級設計工具等領域。

作為國內領先的集成電路設計EDA及工業軟件企業,上海合見工業軟件集團有限公司(簡稱“合見工軟”)以三年推出20餘款產品的創新速度、硬核的技術實力獲得了國內集成電路行業的廣泛認可。公司在回答時代給予的考題的同時,也引領了產業發展、技術創新和生態完善的國產EDA新態勢。合見工軟的創新戰略,也從解決關鍵卡脖子問題,提升為打造技術領先優勢,對標國際壟斷產品性能,以應對目前智算大芯片所帶來的技術挑戰,提供高水平的數字芯片EDA及IP解決方案。

9月24日,在IDAS 2024設計自動化產業峯會期間隆重召開了“2024合見工軟年度新產品發佈會”,會上重磅發佈了多款國產自主自研EDA及IP產品,其中多項產品技術達到了國際先進性能水平,為中國本土EDA技術突破提供了強大的推動力。

在本次發佈會上,合見工軟發佈的產品包括國產硬件仿真器中首台可擴展至460億邏輯門設計的硬件仿真平台UVHP、新一代單系統先進原型驗證平台、DFT全流程平台、電子系統設計工具和五款高速接口IP產品在內的11款創新產品。

此次一年一度的產品發佈,正是合見工軟堅守初心、識勢而為、多措並舉的紮實發展道路的體現。合見工軟針對大規模算力集羣高速發展給數字大芯片設計帶來的多重挑戰,發佈了多個創新產品以供應對,包括算力主芯片方案、存儲方案、互聯方案和系統方案。

EDA²副理事長、深圳市海思半導體有限公司CIO刁焱秋,清華大學、復旦大學、上海大學等學界代表,以及知名半導體公司高管及客户共計超過400位代表,共同出席了合見工軟新產品發佈會。

發佈會上,合見工軟董事長潘建嶽先生作開幕致辭,EDA²副理事長刁焱秋先生進行特邀致辭。合見工軟董事長潘建嶽先生表示,合見工軟以世界級EDA公司為遠景,目標為中國集成電路行業提供國際領先水平的創新EDA工具,契合國家加快發展新質生產力的重要要求。縱覽歷史,EDA發展始終走在集成電路行業的最前端,引領創新。從創立伊始,合見工軟始終以產品技術為核心,保持着閉關研發、夯實基礎,幾年間合見工軟已從一家初創企業,發展為國內數字芯片EDA的領導企業,同時更跨越到系統級和IP多個領域,推出的EDA及IP產品以迭代到具有全球競爭力為目標。目前合見工軟成為國內首家可以為數字大芯片設計提供“EDA+IP+系統級”聯合解決方案的供應商,刷新了EDA研發的中國速度,引領了國產EDA創新時代。潘建嶽強調,合見工軟一路走來得到了很多用户及合作伙伴的支持,未來合見工軟將繼續保持技術攻堅和產品創新,助力國內集成電路設計企業乃至全球產業的進步。

數字驗證全新硬件平台:

數據中心級全場景超大容量硬件仿真加速驗證平台UniVista Hyperscale Emulator(簡稱“UVHP”)全新一代商用級、單系統先進原型驗證平台PHINE DESIGN Advanced Solo Prototyping(簡稱“PD-AS”)

數字實現EDA工具:國產自主知識產權的可測性設計(DFT)全流程平台UniVista Tespert:

高效缺陷診斷軟件工具UniVista Tespert DIAG高效的存儲單元內建自測試軟件工具UniVista Tespert MBIST

PCB板級設計工具:新一代電子系統設計平台UniVista Archer

一體化PCB設計環境UniVista Archer PCB板級系統電路原理設計輸入環境UniVista Archer Schematic

全國產自主知識產權高速接口IP解決方案:

UniVista UCIe IP——突破互聯邊界、下一代Chiplet集成創新的全國產UCIe IP解決方案UniVista HBM3/E IP——拓展大算力新應用、加速存算一體化的全國產HBM3/E IP解決方案UniVista DDR5 IP——突破數據訪問瓶頸、靈活適配多元應用需求的全國產DDR5 IP解決方案UniVista LPDDR5 IP——大容量高速率低功耗的全國產LPDDR5 IP解決方案UniVista RDMA IP——助力智算萬卡互聯、200G和400G高性能的全國產RDMA IP解決方案

全場景驗證硬件系統彰顯自主創新力

AI智算、HPC超算、AD/ADAS智駕、5G、以及超大規模網絡等應用領域,正推動芯片設計的規模、功能集成度和軟硬件系統級複雜度大幅提升。這對驗證工具的能力提出了更高要求,並帶來了多樣化場景驗證的挑戰。驗證工具除了必須為芯片設計開發提供更快速準確的編譯和更高效的調試能力外,還必須具備更靈活、更統一的全場景驗證平台。這不僅可提升故障糾錯效率和驗證吞吐量,還能降低大規模複雜芯片流片的風險,併為軟硬件協同仿真驗證提供強大的數字孿生能力。

**合見工軟宣佈推出數據中心級全場景超大容量硬件仿真加速驗證平台UniVista Hyperscale Emulator(簡稱“UVHP”),為國產自研硬件仿真器中首台可擴展至460億邏輯門設計的產品,並支持多系統進一步擴展,可大幅提升仿真驗證效率,縮短超大規模芯片的仿真驗證週期。**超大容量硬件仿真加速平台UVHP基於合見工軟自主研發的新一代專有硬件仿真架構,採用先進的商用FPGA芯片、獨創的高效能RTL綜合工具UVSyn、智能化全自動編譯器,以及豐富的高低速接口和存儲模型方案,為超大規模ASIC/SOC的仿真驗證提供強大支持。

客户評價:

燧原科技COO張亞林表示:“我們與合見工軟是長期的戰略合作伙伴。在我們之前的算力芯片項目中,合見工軟的UVHS雙模工具作為主要驗證平台,憑藉出色性能和全面的智算解決方案,大幅提升了我們AI軟件算法的開發效率,獲得工程團隊的一致好評。我們一直期望合見工軟推出更高集成度的大容量硬件加速器,如今UVHP平台的問世,填補了國產商用硬件加速器在千片FPGA規模級別的空白。我們期待UVHP以及其配套虛擬平台和hybrid方案在未來項目中的表現,會繼續與合見工軟攜手,共同推動國產算力平台的發展。”

國內首發!創新商用級單系統先進原型驗證平台

FPGA原型驗證平台能夠實現更快的軟件運行速度,大幅縮短軟件運行時間和驗證迭代週期,同時也使得軟硬件協同數字孿生設計開發成為可能,助力加速芯片上市。隨着用户設計的複雜度、靈活度等需求的挑戰不斷湧現,芯片驗證亟需更大規模且兼具靈活性、易用性及更高性能的單系統原型驗證平台。

**合見工軟推出全新一代商用級、單系統先進原型驗證平台PHINE DESIGN Advanced Solo Prototyping(簡稱“PD-AS”),**搭載AMD新一代超大自適應SoC——AMD Versal™ Premium VP1902 Adaptive SoC,採用先進工藝,整體設備性能提升兩倍以上,並配套靈活便捷的操作界面、豐富多種的接口方案,可覆蓋更大規模的芯片驗證場景,將廣泛應用於5G-WIFI通訊、智算、AIoT、智能汽車、RF-導航、RSIC-V IP、VR/AR等行業領域。

賽昉科技董事長兼CEO徐滔表示:“在開發和驗證過程中,效率至關重要。賽昉科技通過先進的設計環境,能夠快速定製符合客户需求的CPU,而驗證和軟件驗證是確保質量的關鍵環節。客户對高質量產品的期望,促使我們對所有RISC-V IP進行全面的驗證工作,包括功能驗證、迴歸測試以及整個軟件棧的驗證。為此,我們藉助合見工軟單系統先進原型驗證平台PD-AS系列1902平台和全場景驗證硬件系統UVHS開展這些任務。前者用於單核和雙核的開發,後者則適用於規模更大的四核以上系統。通過這些平台,賽昉每天能夠執行數萬億次週期,大大提升了開發過程中的驗證效率和問題識別速度。

隨着產品複雜度和規模的不斷提升,合見工軟超大容量硬件仿真加速驗證平台UVHP將持續支持賽昉未來的項目開發。UVHP卓越的性能和RTL調試能力,將幫助賽昉在更復雜的設計中實現快速驗證和調試,加速複雜RISC-V核心的開發流程。”

合見工軟全新一代PD-AS原型驗證平台,可用於SoC、IP等芯片驗證領域,適配各種驗證場景需求,縮減測試進程,加快芯片面市,平台具有更大容量,等效邏輯門數約1億門,比起上一代產品擴大了兩倍以上;更快的速度及更豐富的接口擴展方案,覆蓋了儘可能多的應用場景。

**自研DFT全流程平台,**助力半導體測試邁向新高度

為了滿足人工智能、數據中心、自動駕駛等場景對大算力的需求,芯片尺寸和規模越來越大,單芯片晶體管多達百億甚至千億級別。同時,高階工藝和先進封裝如Chiplet等技術的應用,也大大增加了芯片的集成度與複雜度,設計與製造過程中芯片出現故障的幾率大幅提升,對芯片測試DFT解決方案也提出了更高的要求。需要快速精準地發現故障,修復或者避開故障從而提升良率。同時需要進一步提升測試覆蓋率,將一些測試流程左移,以減少缺陷逃逸率,避免增加成本或延誤產品上市時間。

**合見工軟宣佈推出國產自主知識產權的可測性設計(DFT)全流程平台UniVista Tespert。**該平台集成了一系列高效工具,包括最新推出的高效缺陷診斷軟件工具UniVista Tespert DIAG、高效的存儲單元內建自測試軟件工具UniVista Tespert MBIST,以及合見工軟此前推出的測試向量自動生成工具UniVista Tespert ATPG。UniVista Tespert致力於為工程師提供更高效、更高質量的完整芯片測試平台化工具,滿足現代芯片設計複雜度和封裝技術挑戰,助力客户提升產品質量和市場競爭力。

最新推出的**UniVista Tespert DIAG是一款創新高效的缺陷診斷軟件工具,**自主研發了高效準確的診斷引擎,採用新一代數據結構,支持壓縮和非壓縮的測試向量診斷技術。其圖形化界面提供了缺陷全景對照,幫助工程師快速定位和解決系統性缺陷,大幅提升芯片測試效率,加速產品上市時間。

同時推出的**UniVista Tespert MBIST是一款先進存儲單元自測試工具,**集成了先進的IJTAG接口協議,提供直觀易用的圖形界面,支持多種測試算法和靈活的設計規則檢查引擎。通過UVTespert Shell自動化平台,它有效提高了測試設置的效率和可靠性,特別針對先進工藝如FinFET進行了優化,為客户提供了全面的存儲單元測試解決方案。

客户評價:

類比半導體高級總監王海金表示:“合見工軟DFT全流程平台UniVista Tespert為我們在測試領域提供了全面的解決方案,極大地提升了我們的產品測試效率和可靠性。更值得一提的是,UniVista Tespert DIAG的圖形化界面和高效的診斷引擎讓我們能夠更快速地定位和解決芯片缺陷,這對我們的項目進展至關重要。類比半導體作為模擬及數模混合芯片和解決方案供應商,專注於汽車智能驅動、線性產品、數據轉換器等領域的芯片設計,產品主要面向工業和汽車等市場。與合見工軟的深化合作,將幫助類比致力於為客户提供高品質芯片,為世界科技化和智能化發展提供底層的芯片支持。”

青芯半導體科技(上海)有限公司DFT技術總監呂寅鵬表示:“合見工軟UniVista Tespert平台為我們提供了強大的DFT工具,幫助我們應對複雜芯片設計和測試的挑戰,提高了產品質量和市場競爭力。我們在使用UniVista Tespert MBIST時,發現該工具對存儲單元的測試管理非常有力,為我們的芯片設計團隊提供了更多的設計自由度。我們相信這款工具能夠得到更多的廣泛應用,為芯片製造業帶來更加精準、高效的解決方案。”

UniVista Tespert是合見工軟更廣泛的數字實現EDA產品組合的重要產品之一,目前已經實現了在汽車電子、高階工藝芯片等領域的國內頭部IC企業中的成功部署,應用於超過50多個不同類型芯片測試。

**HBM3e領銜,**完整IP組合打造大算力芯片強力引擎

合見工軟宣佈推出五款全新全國產自主知識產權高速接口IP解決方案,為用户提供了創新、高可靠性、高性能的網絡IP、存儲IP及Chiplet接口IP解決方案,應對智算時代所帶來的網絡互聯、先進封裝集成、高數據吞吐量等諸多挑戰。

UniVista UCIe IP——突破互聯邊界、下一代Chiplet集成創新的全國產UCIe IP解決方案

隨着各類前沿高性能應用對算力、內存容量、存儲速度和高效互連的需求持續攀升,傳統大芯片架構的設計和能力越來越難以及時滿足這些需求。Chiplet集成技術的出現開闢了一條切實可行的路徑,使得各個廠商能夠在芯片性能、成本控制、能耗降低和設計複雜性等方面實現新的突破。

作為Chiplet集成的關鍵標準之一,UCIe以開放、靈活、高性能的設計框架為核心,實現了採用不同工藝和製程的芯粒之間的無縫互連和互通。通過統一的接口和協議,UCIe可大幅降低同構和異構芯粒集成的設計複雜度,使設計人員能夠更加專注於各個芯粒的功能實現和優化,從而加速產品開發進程。

UniVista UCIe IP產品已在智算、自動駕駛、AI等領域的知名客户的實際項目中得到廣泛應用和驗證,在真實場景中展現出卓越的性能表現和穩定可靠的品質。合見工軟UCIe IP先進製程測試芯片現已成功流片,成為IP領域第二個經由硬件驗證過的先進製程UCIe IP產品。

隨着智能計算領域的高速發展,數據中心已逐步升級為智算中心,其中高性能計算芯片也已從CPU/DPU過渡到AI/GPU等大算力芯片。為了充分發揮大算力芯片的性能,大容量、高帶寬、高速率、低功耗的內存解決方案成為了重要的發展方向。在大算力場景下,內存容量或帶寬的限制會導致訪存時延高、效率低,嚴重製約算力芯片性能的發揮。此外,隨着數據傳輸速率的持續提升,芯片不僅需要保證高數據吞吐量,同時還必須兼顧低功耗,這已成為架構設計的關鍵重點關注點之一。

為保障芯片的高性能、低功耗,應對AI、ML、HPC等應用場景的發展,合見工軟推出全國產Memory接口解決方案,包括:

UniVista HBM3/E IP——拓展大算力新應用、加速存算一體化的全國產HBM3/E IP解決方案

UniVista HBM3/E IP包括HBM3/E內存控制器、物理層接口(PHY)和驗證平台,採用低功耗接口和創新的時鐘架構,實現了更高的總體吞吐量和更優的每瓦帶寬效率,可幫助芯片設計人員實現超小PHY面積的同時支持最高9.6 Gbps的數據速率,解決各類前沿應用對數據吞吐量和訪問延遲要求嚴苛的場景需求問題,可廣泛應用於以AI/機器學習應用為代表的數據與計算密集型SoC等多類芯片設計中,已實現在AI/ML、數據中心和HPC等領域的國內頭部IC企業中的成功部署應用。

UniVista DDR5 IP——突破數據訪問瓶頸、靈活適配多元應用需求的全國產DDR5 IP解決方案

UniVista DDR5 IP包括DDR5內存控制器、物理層接口(PHY)和驗證平台,採用先進的設計架構和優化技術,經過嚴苛的實際應用場景驗證和深度評估,可幫助芯片設計人員實現高達8800 Mbps的數據傳輸速率,支持單個最高64 Gb容量的內存顆粒,256 GB容量的DIMM並集成ECC功能,解決企業級服務器、雲計算、大數據等應用領域對高可靠性、高密度和低延遲內存方案的場景需求問題,可廣泛應用於數據中心/服務器、高端消費電子SoC 等多類芯片設計中,已實現在雲服務、消費電子、服務器/工作站等領域的國內頭部IC企業中的成功部署應用。

UniVista LPDDR5 IP——大容量、高速率、低功耗的全國產LPDDR5 IP解決方案

UniVista LPDDR5 IP包括LPDDR5內存控制器、物理層接口(PHY)和驗證平台,採用優化的設計架構,經過多種實際應用場景驗證和評估,可幫助芯片設計人員實現高達8533 Mbps的數據傳輸速率,支持單個最高32 Gb容量的內存顆粒,並集成ECC功能,解決移動設備、IoT、汽車電子等應用領域對高性能、低功耗和小尺寸內存方案的場景需求問題,可廣泛應用於移動設備、IoT和汽車電子SoC等多類芯片設計中,已實現在移動設備和IoT等領域的國內頭部IC企業中的成功部署應用。

AI大模型時代,算力集羣進行的分佈式訓練,節點間的通信消耗巨大,這使得通信網絡成為了制約大模型訓練效率的關鍵因素。除了訓練芯片,推理芯片比以往需要更大規模的組網完成更大token的運算。組網規模、網絡性能和可靠性等方面正在成為制約算力集羣效率的突出問題。越來越多的芯片正通過基於以太網交換機的RoCEv2網絡實現超大規模組網方案。為了保證大算力芯片能擁有完善的網絡性能,在設計和驗證網絡功能上給眾多AI芯片公司提出了新的挑戰。

合見工軟全新推出國內領先的高帶寬、低延遲、高可靠性的智算網絡IP解決方案UniVista RDMA IP,助力智算萬卡集羣,主要功能包括支持200G、400G帶寬的完整RoCEv2傳輸層、網絡層、鏈路層、物理編碼層,可幫助芯片設計人員實現快速的RDMA功能集成,解決智算芯片的高帶寬需求問題,可廣泛應用於AI、GPU、DPU等多類芯片設計中,相比於傳統25G/50G RDMA互聯方案,性能更領先,已實現在AI和GPU等領域的國內頭部IC企業中的成功部署應用。

**UniVista RDMA IP——助力智算萬卡互聯、200G和400G高性能的全國產RDMA IP解決方案。**UniVista RDMA IP的四大優勢包括:

更高的帶寬利用率:支持超頻點應用,比標準以太網提供多10%的帶寬;支持靈活支持可配置報文頭,包括可配置前導碼、IPG、MAC幀頭;支持超長報文,報文長度最高可達32K bytes。更高的可靠性:支持RDMA的傳輸層的端到端重傳,重傳完成時間達到10us量級;提供基於以太網MAC層的端到端重傳,重傳完成時間達到us量級;支持以太網PHY層的點到點重傳,重傳完成時間達到100ns量級。更靈活的組網方式:支持基於以太網PHY層協議的點到點直連;支持以太網PHY配置1拆2、1拆4,靈活支持8卡、16卡、32卡全互聯;RDMA QP數量,WQE數量可配置,與直連協議可切換。更低的延遲:優化FEC低延遲模式,在已有的RS272算法上進一步降低FEC的解碼延遲;提供PAXI直連模式,通過以太網物理層實現C2C連接,降低延遲;簡化UDP/IP以及MAC層協議,提供簡化包頭模式。

合見工軟的高速接口IP解決方案已實現了國產化技術突破,引領智算、HPC、通信、自動駕駛、工業物聯網等領域大算力芯片的性能突破及爆發式發展。

**解決高速、多層PCB設計挑戰:**國產首款高端大規模PCB設計平台

隨着電子系統技術的不斷發展,產品的核心功能極大程度地依賴於高性能大規模集成電路實現,大規模、高性能集成電路的廣泛應用,將電子系統的信號種類、數量、系統互連關係變得異常複雜。要實現複雜系統的精確描述,以確保電子系統設計的正確性與可靠性,對PCB及原理圖設計方法與流程的更新換代提出了更嚴苛的要求,大規模、小型化、高密度、高速率已經成為板級系統的重要發展趨勢。UniVista Archer平台是首款國產自主自研的高性能大規模PCB和原理圖設計工具,支持的PCB設計規模已達到國內先進水平,能夠實現更高密度的佈局佈線,並保障更快的軟件運行速度,助力更智能化電子系統產品的發展。

**合見工軟宣佈推出新一代電子系統設計平台UniVista Archer,作為自主知識產權的國產首款高端大規模PCB設計平台,滿足日益複雜的電子系統設計需求,解決高速、多層PCB設計中帶來的設計與仿真挑戰,**為電子系統和PCB板級設計工程師帶來更高的性能與可靠性,並支持客户歷史設計數據導入,易學易用。UniVista Archer平台包括領先的一體化PCB設計環境UniVista Archer PCB和板級系統電路原理設計輸入環境UniVista Archer Schematic兩款產品,採用全新的先進數據架構,部分產品性能大幅提升,精準洞察用户的需求習慣,大幅提升用户體驗,滿足用户的複雜功能需求,為現代複雜電子系統提供一體化的智能設計環境。

客户評價:

華勤通訊技術有限公司高級副總裁吳振海表示:“合見工軟UniVista Archer PCB 、UniVista Archer Schematic產品在我們多個產品線進行了設計、驗證。在使用合見工軟的工具設計週期中,設計數據精準,符合我們公司的設計要求。另外合見工軟的PCB工具支持導入行業內主流的PCB設計數據,其導入數據的完整性和還原度也非常優秀。除了產品本身,合見工軟技術團隊的支持力度和響應速度,讓我們充分感受到EDA工具本土化的優勢。”

合見工軟現可提供覆蓋“元器件庫+數據管理+流程管理+設計工具”的電子系統級EDA的全流程解決方案。在系統級EDA工具的高端市場上,全面展示了合見工軟公司產品的競爭。

關於合見工軟

上海合見工業軟件集團有限公司(簡稱“合見工軟”)作為自主創新的高性能工業軟件及解決方案提供商,以EDA(電子設計自動化,Electronic Design Automation)領域為首先突破方向,致力於幫助半導體芯片企業解決在創新與發展過程中所面臨的嚴峻挑戰和關鍵問題,併成為他們值得信賴的合作伙伴。

瞭解更多詳情,請訪問:www.univista-isg.com