Intel 3D封裝技術開始量產,後摩爾時代競爭已經到來

唐晓甫

(觀察者網訊)1月25日中午,英特爾官微發佈消息宣佈,該公司已實現基於業界領先的半導體封裝解決方案的大規模生產,其中包括英特爾突破性的3D封裝技術Foveros。

公司方面表示採用Foveros封裝技術的芯片將在英特爾最新完成升級的美國新墨西哥州Fab 9芯片工廠投產。這意味着,英特爾已經準備好挑戰台積電在先進封裝方面的領先地位。

據悉,此次投入量產的英特爾3D先進封裝技術Foveros在處理器的製造過程中,能夠以垂直而非水平方式堆疊計算模塊。此外,Foveros讓英特爾及其代工客户能夠集成不同的計算芯片,優化成本和能效。

英特爾宣稱,這個量產技術的突破為公司下一階段先進封裝技術創新奠定了基礎,同時也意味着公司在“後摩爾時代”,推進在單個封裝中集成多個“芯粒”(chiplets)的異構芯片生產中獲得了速度更快成本更低的技術路徑,為以後實“現單個封裝中集成一萬億個晶體管,並在2030年後繼續推進摩爾定律”創造了條件。

什麼是Foveros,採用Forveros有什麼好處

此次提到的英特爾Foveros技術是一種3D IC技術,也即一種3維集成電路。採用這種技術的芯片將和傳統芯片在結構上有質的不同。

傳統集成電路的製造方式是將晶圓經多次光掩模處理,將其光掩模上的電路克隆到每一層晶圓上。然後再進行刻蝕、摻雜等工序製成具有多層線路與器件的IC晶圓。最後將晶圓交給後段進行測試、切割、封裝,以製成實體的集成電路成品。這導致了不同功能的芯片只能集成在基板,而不能融合成一顆芯片。

這樣的設計雖然獲得了巨大的成功,但是隨着半導體產業的發展和AI大數據需求提升。傳統設計在面對大數據和AI需求時,在數據搬運、處理和功耗控制方面並不友好。相關運算過程中大量數據搬運本身就會導致大量發熱,同時基板的數據傳輸速度會限制芯片的處理能力。

而以Foveros為代表的先進封裝則改變了芯片的通過基板連接方式。使用先進封裝技術的芯片通過硅通孔、橋接器、硅中介層或導線層可以實現不同芯片之間完成更大規模串聯,然後再封裝成一顆芯片。這也就意味着存儲芯片可以更快處理更多數據。

這種在一個芯片上集成多種不同材料、不同結構和不同功能元件的一體化技術也被稱為異構/異質集成技術。

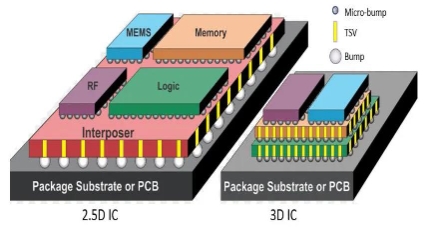

不同於2.5D封裝,3D 封裝不採用硅中介層

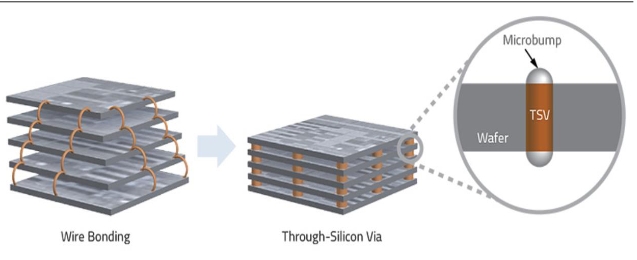

具體來説,Foveros採用的是3D堆疊芯片技術路徑,3D堆疊不同於其他如2.5D堆疊路線,不需要採用中介層才能實現各種不同功能芯片的連接。而是只需要透過硅穿孔(Through-Silicon Via,TSV)技術與微凸塊(micro-bumps)搭配,就可以把不同的邏輯芯片堆疊起來。通過實現包括“近存運算”佈局等方式進一步提高了數據處理速度,減少了能量耗散。但要實現相關工藝並不容易,根據英特爾2019年披露信息顯示,Foveros的凸塊接點的間距(pitch)僅有約36微米,提高其良品率非常考驗英特爾的生產技術了。

TSV(硅通孔)工藝將多層平面進行堆疊互連 圖片來源:開源證券

對此,英特爾此前曾非常自豪將其稱為“臉貼臉(Face-to-Face)”的封裝,強調它的封裝特點。

為什麼需要全新技術路徑的芯片

事實上,發展全新技術路徑的芯片已經成為業內的共識。在先進芯片領域,我們事實上已經進入了“後摩爾時代”。

摩爾定律是一個對很多人來説耳熟能詳的詞彙。摩爾定律是英特爾創始人之一戈登·摩爾的經驗之談,其核心內容是:集成電路單位面積上可以容納的晶體管數量每18個月到24個月就會增加一倍,與此同時功耗和價格不變。換言之,芯片的性能大約每兩年翻一倍,同時單位性能對應的價格減半。

在他的預測中,摩爾定律的實現有兩個關鍵要素:價格和單位面積晶體管數量。但是隨着半導體技術的發展,這兩者的發展都很難再繼續延續摩爾定律的預言。

根據《Chiplet Heterogeneous Integration Technology—Status and Challenges》,引用IBS數據測算,在22納米工藝製程之後的每一代技術設計成本增加均超過50%。7納米工藝的總設計成本約3億美元,而3納米工藝總設計成本將增加5倍,達到15億美元。此外中芯國際招股書中引用IBS數據表明,集成電路製造的設備投入也呈大幅上升的趨勢。其中,5納米技術節點投資成本約155.6億美元,約為28納米的四倍。

ASML EUV光刻機 圖片來源:ASML官網

此外,由於單位面積晶體管數量快速上升,晶體管特徵尺寸縮小到10nm以下,量子隧穿效應導致漏電愈發嚴重。同時良率的技術限制(例如光刻機掩模尺寸),現有的單片集成提升變得難以為繼。所以先進芯片需要新的工藝來升級和擴展芯片功能和性能。

近年來AI的發展也迫使人們尋求更快速處理數據的芯片方案。深圳大學校長毛軍發院士在去年7月底的2023年全國虛實融合交互大會上做報告時候就提到了,近幾十年平均下來,處理器的峯值算力每兩年增長3.1倍,而動態存儲器的帶寬每兩年增長1.4倍,存儲器的發展速度遠落後於處理器,相差1.7倍。現有的TB級帶寬難以滿足P級和E級算力需求(1P相當於每秒1000萬億次計算速度,1E是指每秒能做100億億次數值運算),未來數據的讀取存儲速度將決定超級計算機以及超級AI的性能上限。將存儲芯片和運算芯片直接連接的異構集成芯片將可以極大的緩解存儲讀取速度慢的難題。

所以為了以更低成本實現芯片性能的根本性提升,基於先進封裝和異構集成技術為芯片未來發展方案被視作超越摩爾定律的最主要技術方向。

先進封裝未來已至

隨着先進封裝技術在近年來的逐步成熟,現有世界半導體巨頭都在不斷推進包括2.5D和3D堆疊芯片在內的先進封裝芯片產業化應用。英偉達、AMD等公司甚至已經將先進封裝視作高級AI芯片的一種標配。

英偉達近年推出的包括H100、H200芯片在內的多種頂級AI芯片均採用了台積電成熟的CoWoS 2.5D封裝技術。而AMD旗下的MI300X AI芯片則混合使用了台積電的2.5D和3D封裝技術。

AMD MI300X芯片發佈 圖片來源:AMD

本文系觀察者網獨家稿件,未經授權,不得轉載。