GaN的未來,是什麼?_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。昨天 16:53

過去兩年中,氮化鎵雖然發展迅速,但似乎已經遇到了瓶頸。與此同時,不少垂直氮化鎵的初創企業倒閉或者賣盤,這引發大家對垂直氮化鎵未來的擔憂。為此,在本文中,我們先對氮化鎵未來的發展進行分析,並討論了垂直氮化鎵器件開發的最新進展以及相關的可靠性挑戰。

**氮化鎵的未來:**高電壓、高電流和雙向性

氮化鎵功率器件正在滲透並提高包括快速充電器和電源在內的多種消費類應用的效率。大眾市場對此反應熱烈,氮化鎵的應用在手機和筆記本電腦等便攜設備(功率範圍在 65 到 250W 之間)的快速充電器以及高達 3.2 kW 的電源中蓬勃發展。

隨着氮化鎵開始在低功率應用中部署並證明其在現場的可靠性,我們現在看到了氮化鎵滲透到高功率應用的機會,這將對經濟、生態和社會產生更實質性的影響。強大的機遇存在於能量收集、汽車、數據中心和人工智能領域。為了實現這一目標,必須對重要元素進行完善。為了提供高功率,氮化鎵必須處理高電壓和高電流,不僅要高效,還要安全、可靠且低成本。氮化鎵擁有所有成功的特性。

在本文中,我們將介紹突破性的賦能技術:1200V 額定值、大外延氮化鎵器件(電流額定值高達 170A,單芯片功率高達 14kW 的記錄)、高達 5μs 的短路能力(用於故障安全操作)以及用於新型、更緊湊電路拓撲的單片雙向開關,從而實現更輕、更小、更高效、更可靠的轉換系統。

1.高壓氮化鎵 (1200V)

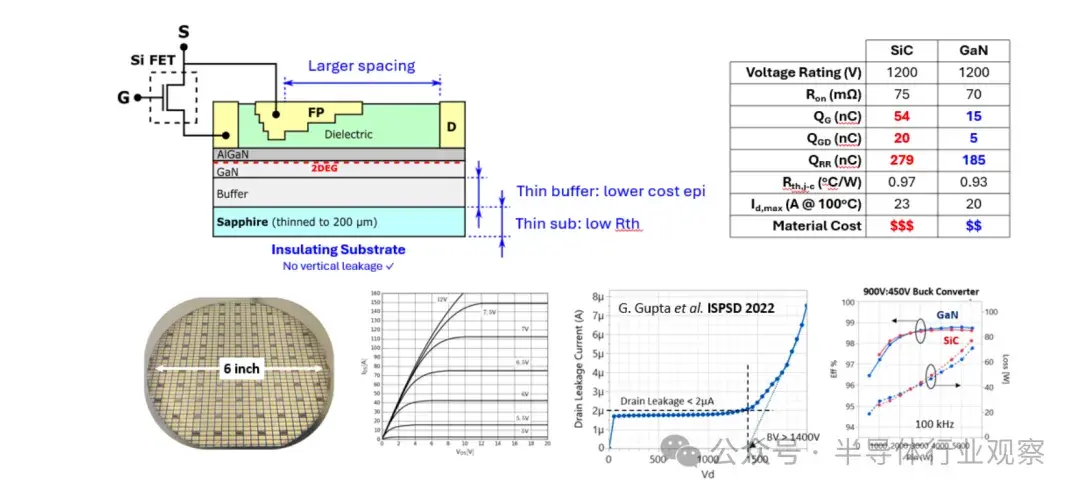

氮化鎵 HEMT 具有獨特的優勢,可以服務於商業上重要的寬電壓範圍,從 100V 到 1200V,並且相對於硅 IGBT、硅 CoolMOS 和碳化硅晶體管具有競爭優勢。直到幾年前,1200V 似乎在商業上使用氮化鎵是不可行的。但在 2020 年初,低成本、高性能的 1200V 氮化鎵解決方案出現在人們視線中。Transphorm 展示了1200V氮化鎵,它使用在藍寶石(一種具有出色電絕緣性的材料)上沉積的材料構建的橫向 HEMT,以消除漏極和襯底之間的擊穿,並阻斷 1200V 及更高的電壓。橫向 1200V 氮化鎵 HEMT 保留了橫向 HEMT 的所有優點:高遷移率(降低存儲電荷)、大面積(提高熱導率)和低製造成本。用藍寶石代替硅可以保持低產品成本和高熱性能。在前道製造過程中,藍寶石上 III-N 緩衝層的厚度可以減少 60% 以上,從而降低外延成本,同時保持良好的晶體質量和高電絕緣性,這不僅在 150 毫米基板上,而且在 200 毫米基板上也是如此。在後道工藝中,藍寶石可以減薄到 150-200 微米,以匹配硅的熱導率。藍寶石已經是氮化鎵 LED 的首選襯底,擁有大量的專業知識和工業大批量生態系統。

在這項工作中,我們展示了採用藍寶石襯底上高電子遷移率晶體管(HEMT)製造的 1200 V GaN 開關的結果(圖 1)。使用封裝在 TO-247 封裝內的 70 mΩ 藍寶石襯底 GaN 2 芯片常關型 GaN FET,我們獲得了 900:450V 降壓轉換器在 50 kHz 下大於 99% 的效率。該器件表現出出色的開關品質因數,Ron∙Qg = 0.9 Ω∙nC,Ron∙Qrr = 11 Ω∙nC。這些結果表明,經過優化的藍寶石襯底 GaN 技術可以成為 1200V 功率器件市場的極具競爭力的平台。目前正在進行重複性和認證任務,以期儘快推出中高功率產品。

2.高電流氮化鎵(170A)

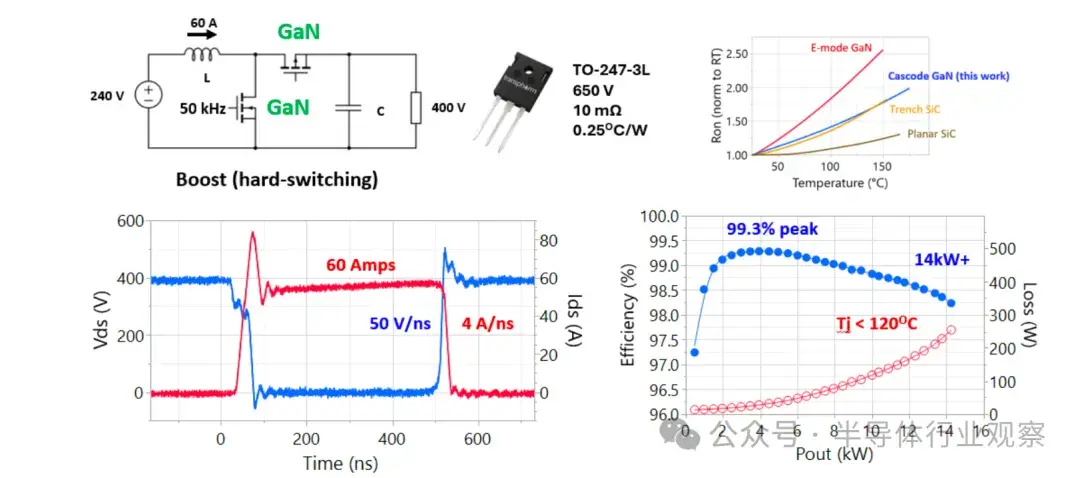

如今,氮化鎵解決方案應用於功率介於 65W 和 3.2kW 之間的低功率和中功率應用,處理的電流僅為幾安培到幾十安培,芯片面積為幾百平方微米。然而,沒有任何物理障礙阻止氮化鎵解決方案處理數百安培的電流,並應用於 10kW 甚至 100kW 以上的高功率應用。在這項工作中,我們展示了高電流氮化鎵原型的新數據,其導通電阻為 10mOhm,額定直流電流超過 170A。該芯片面積為數十平方毫米,並封裝在傳統的 TO-247-3L 封裝中。

硬開關波形和升壓轉換效率如圖 2 所示。該器件的開關速度達到 50V/ns 和 4A/ns,從而實現高功率和高頻開關。在 50kHz、硬開關模式下工作的 240V:400V 升壓轉換器中,效率峯值在 4kW 時達到 99.3%,並平穩地降至 14kW 的功率。可以看出,在 14kW 時,結温僅為 120℃,表明還有更大的裕量可以實現更高的功率。如此出色性能的原因是快速的開關速度,它最大限度地減少了開關損耗;D 模式氮化鎵與低壓硅 MOSFET 級聯配置的低動態 Ron(小於 10%);以及電阻的低温度係數(150℃ 和 25℃ 之間小於 1.8 倍,與 SiC Trench MOSFET 技術相似),這些共同促成了運行中的低傳導損耗。雖然本文展示的是 TO-247-3L 封裝,但本文提出的 10mOhm 芯片不僅可以組裝在帶有 Kelvin 源和更低漏感值的表面貼裝封裝中,還可以作為裸芯片組裝到工業或汽車模塊中。最近的研究表明,氮化鎵級聯器件的並聯已成功實現高達 500A 的電流。

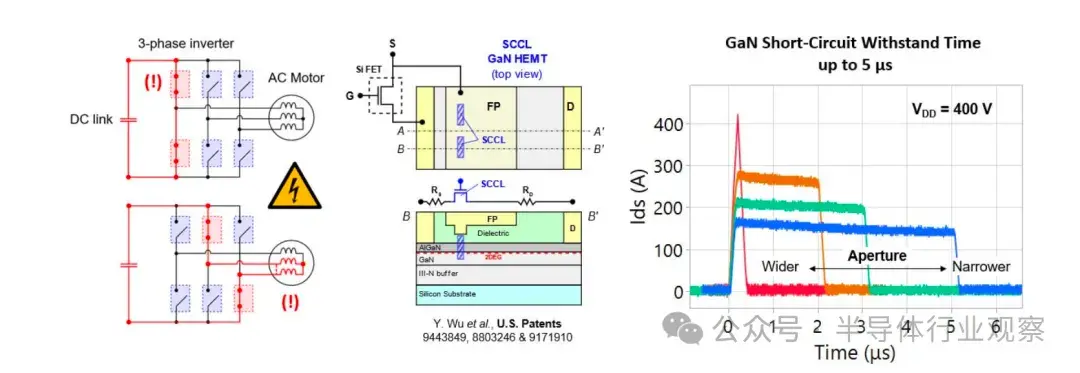

3.短路能力(5μS)

在電機驅動應用中,氮化鎵(GaN)器件不僅要通過嚴格的 JEDEC 或 AEC-Q0101 認證,還必須能夠承受由過載、直通、固件錯誤、電流浪湧和/或外部故障條件引起的短路事件。2021 年,Transphorm 展示了一項獲得專利的 GaN 技術,在 50 毫歐器件上實現了高達 3 微秒的短路耐受時間(SCWT)。今年,我們帶來了重大改進,展示了一款 15 毫歐器件,其短路耐受時間延長至 5 微秒,能夠進行高功率操作(12 千瓦)。該器件採用 TO-247 封裝,額定電壓為 650 伏,額定直流電流為 145 安。其峯值效率達到 99.2%,最大輸出功率為 12 千瓦。在 400 伏的漏極偏置下,其短路耐受時間為 5 微秒(圖 3),並且通過了 1000 小時 175 攝氏度高温反向偏置應力測試。這些數據表明了 GaN 的適應性,打破了其不具備短路能力的“神話”。作為參考,現代柵極驅動器的保護響應時間約為 1 微秒,確保有足夠的時間檢測故障並安全關閉系統,而不會導致器件損壞

4.單片雙向開關

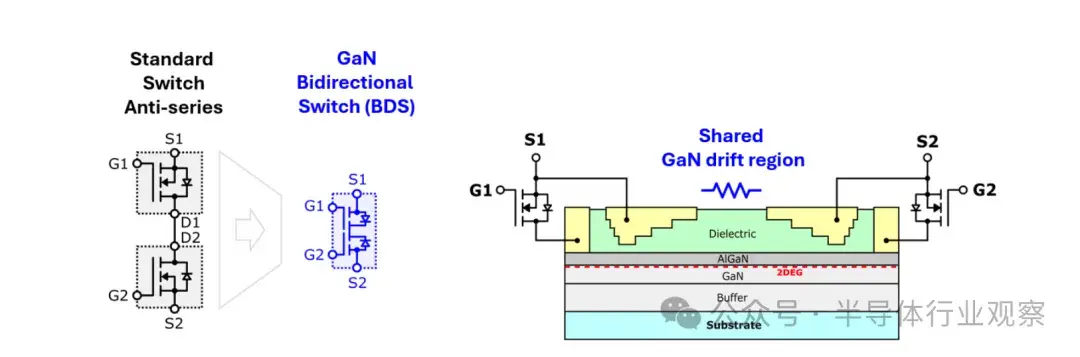

由於其橫向結構,氮化鎵器件非常適合單片集成。可以將兩個反串聯的晶體管單片集成在一起,形成所謂的“雙向開關”(圖 4)。雙向開關具有兩個由兩個相對的柵極控制的相對的源極,並且可以沿兩個方向承載電流,並在兩個極性上阻斷電壓。這種器件架構在氮化鎵中以其簡單性而獨有,對於需要功率器件承受正負交流波瓣的交流前端來説,具有重要意義。

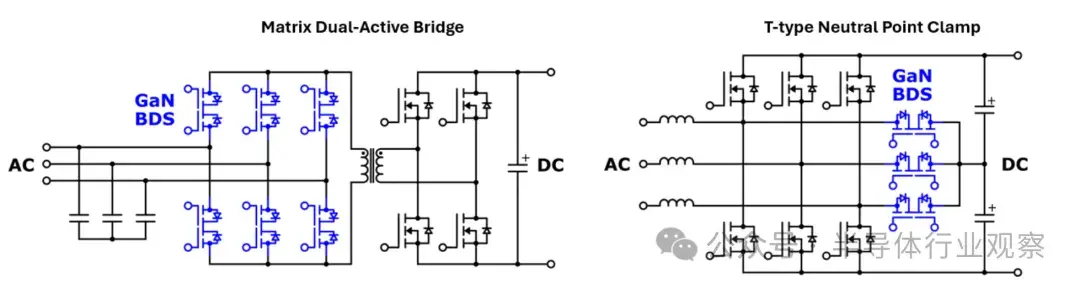

氮化鎵雙向開關支持諸如隔離矩陣雙有源橋(圖 5 左)、非隔離 T 型中性點鉗位 (T-NPC,圖 5 右) 等拓撲結構,以及更多拓撲結構。這些拓撲結構允許在單級中進行 AC/DC 或 DC/AC 轉換——無需體積龐大且昂貴的 DC-link 電容器——從而實現更輕、更小、更高效、更可靠的電源系統。應用非常廣泛,包括電源和電池充電器、太陽能逆變器和電機驅動器。

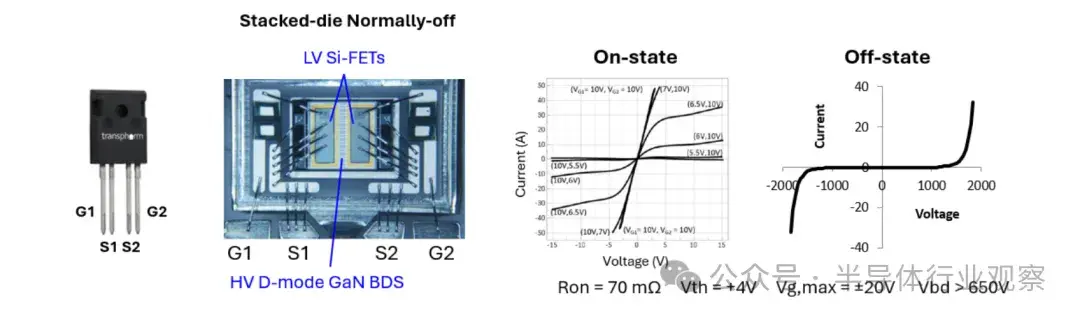

在這項工作中,我們展示了一種氮化鎵雙向技術,其中單片集成的 D 模式雙向氮化鎵 HEMT 與兩個低壓硅 MOSFET 以級聯配置連接,以實現常關操作。HEMT 的單片集成允許共享高壓漂移區,與兩個分立的氮化鎵開關相比,芯片尺寸減小了 40%。低壓硅 MOSFET 允許高閾值電壓 (4V)、高柵極裕量 (+20V)、高可靠性以及高抗噪聲和寄生導通能力。雙向級聯器件採用堆疊芯片技術集成,以最大限度地減少佔位面積以及互連電阻和電感(圖 6)。該解決方案封裝在帶隔離焊片的單個 TO-247 封裝中。如圖 4 所示,D 模式氮化鎵的漂移區在晶體管的兩側之間共享,從而顯着提高了 Ron x Qg 和 Ron x Qoss 的品質因數。導通電阻為 70 mΩ,該器件具有出色的雙向電流傳導和電壓阻斷能力,具有對稱的電流-電壓和電容-電壓特性。Ron∙Qg 比連接在反串聯中的最先進的分立式碳化硅 MOSFET 低 80%,從而降低了開關損耗,降低了成本,減少了零件數量,並減小了佔位面積。

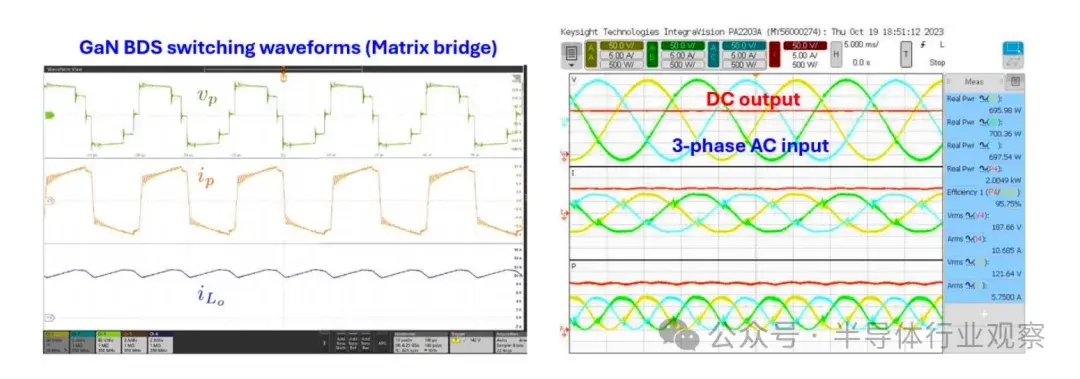

雙向氮化鎵器件已在用於單級 AC/DC 前端的矩陣有源橋中進行了測試,實現了兩個 AC 極性下的電壓阻斷和成功的系統演示(圖 7)。

雖然氮化鎵已經在許多低功率和中功率應用中投入生產和現場部署,但令人興奮的未來在於高功率機會,它將對經濟、生態和社會產生更強大的影響。本文介紹的高壓和高電流氮化鎵、短路能力和單片雙向集成將在數據中心、人工智能、交通運輸等領域發揮重要作用。

接下來,我們對有望挑戰SiC地位的垂直氮化鎵氮化鎵進行分析。

垂直氮化鎵,尚能飯否?

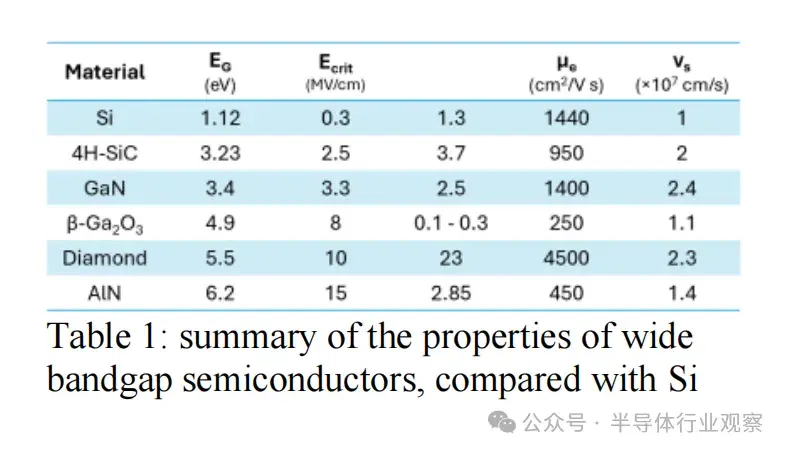

如大家所見在功率轉換領域,寬帶隙半導體正在迅速取代硅器件。大能隙(碳化硅為 3.23 eV,氮化鎵為 3.4 eV)和相應的大擊穿場使這些材料成為開發高效功率半導體器件的理想材料(材料對比見表 I)。

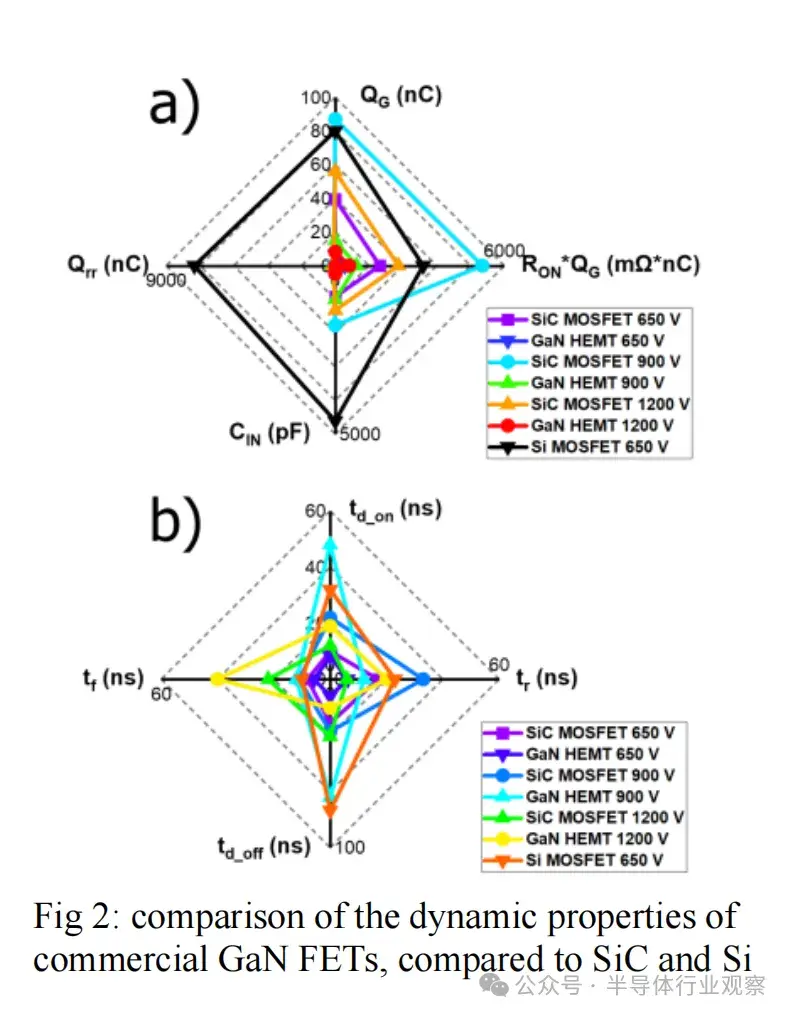

硅、碳化硅和氮化鎵商用器件之間的比較(圖 2)表明,氮化鎵 HEMT 結構的柵極電荷、反向恢復電荷和𝑅𝑜𝑛 ∙ 𝑄𝐺乘積都要低得多,從而大大降低了功率轉換器中的電阻損耗和開關損耗。最近,氮化鎵領域的創新來自垂直器件結構的開發,以進一步提高功率密度和電流密度 。

1.可靠性挑戰

A.優化漂移區以提高性能/可靠性

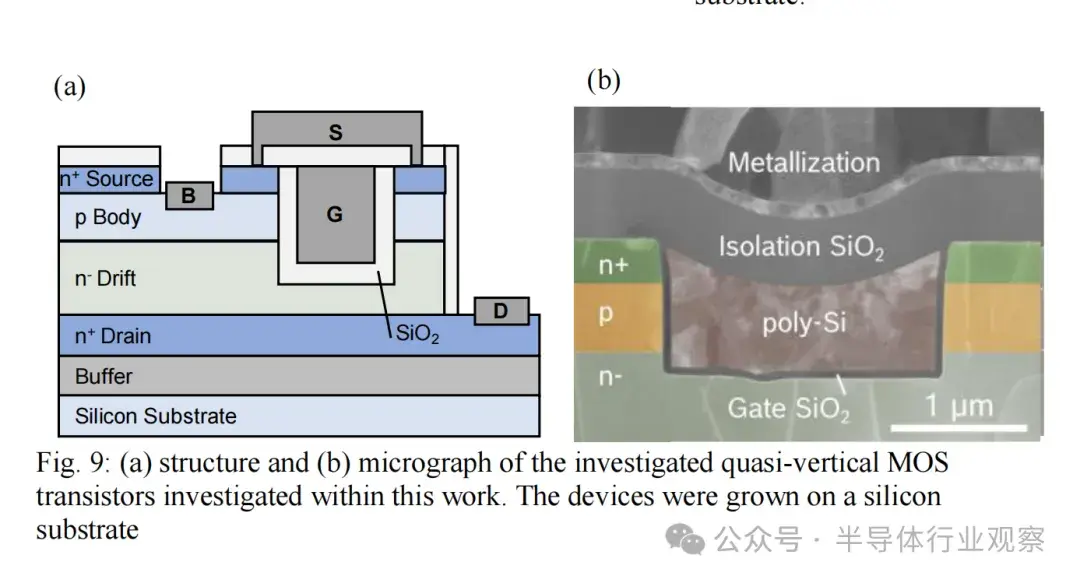

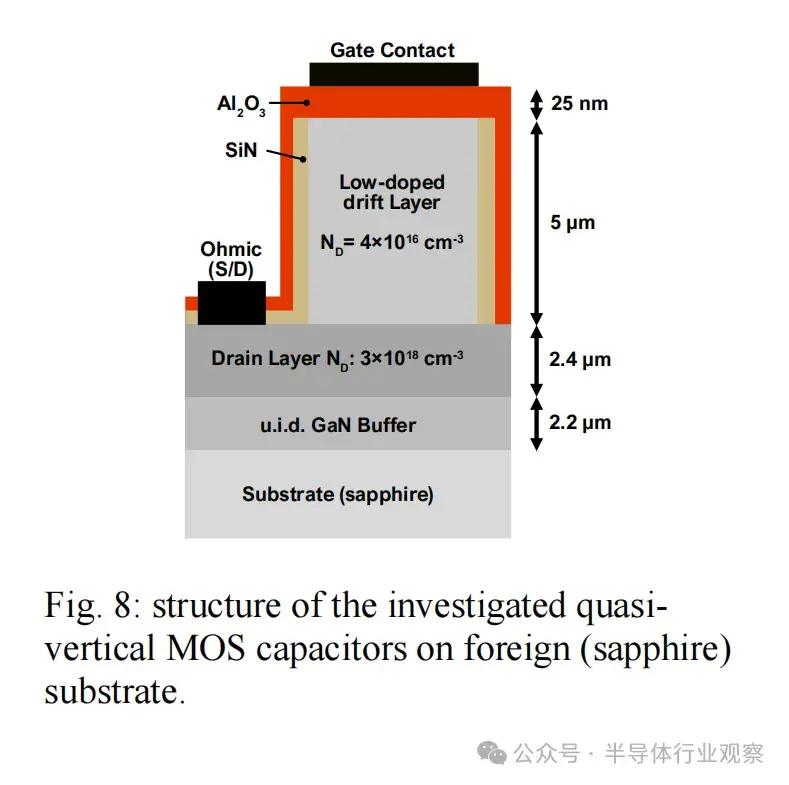

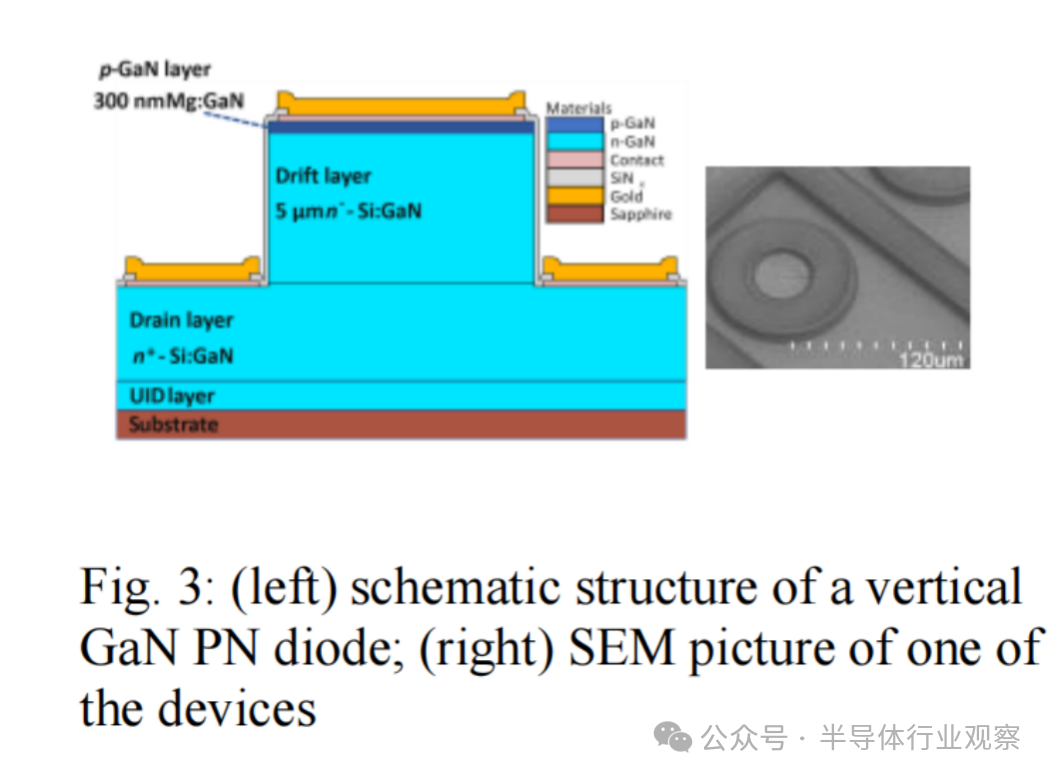

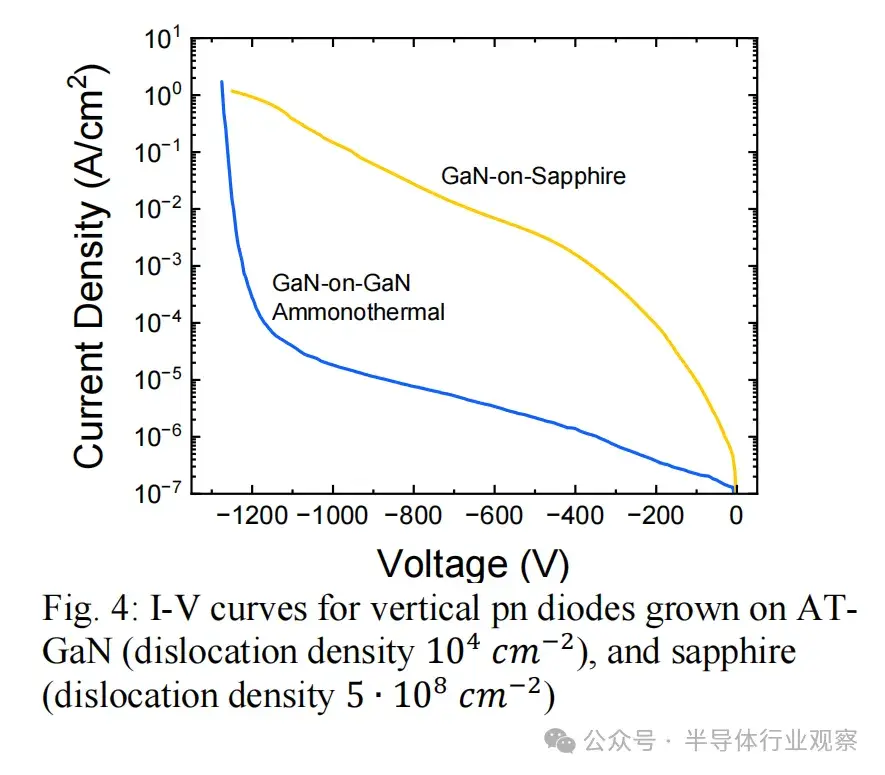

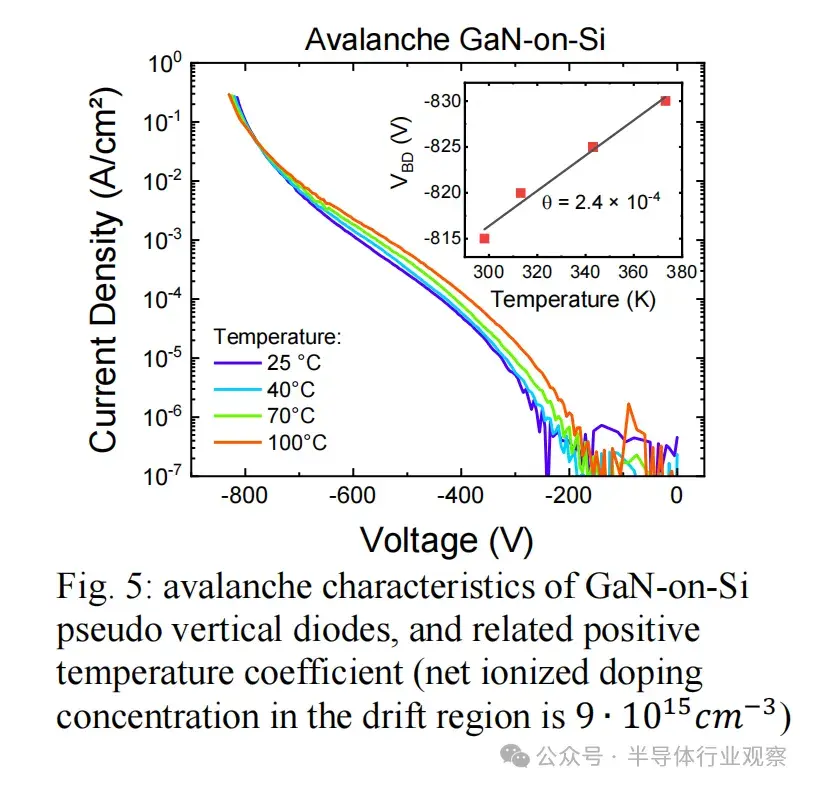

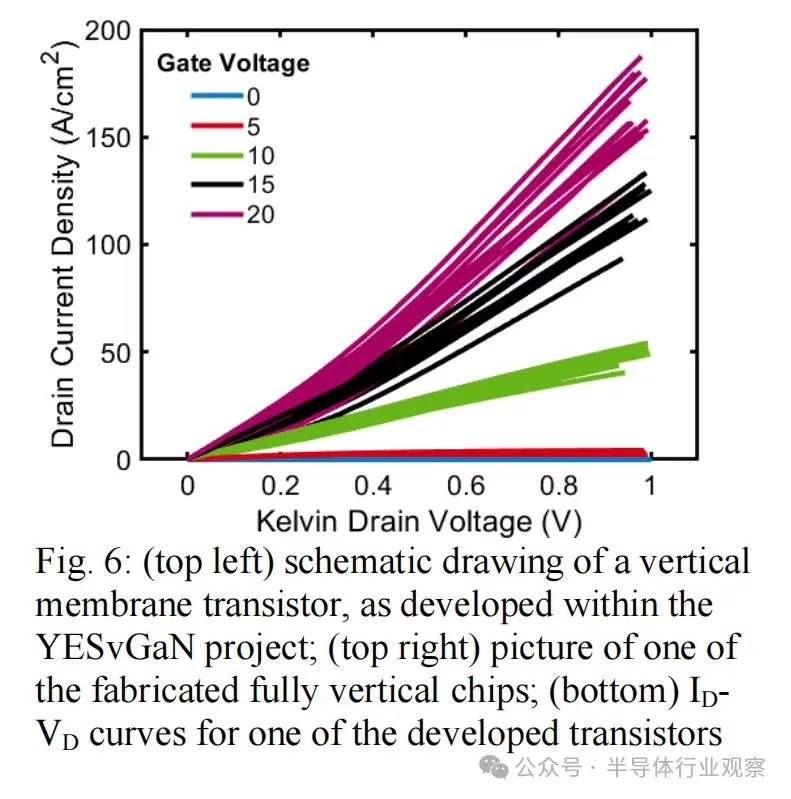

觀察圖 1 中的主要硅和碳化硅器件結構,可以瞭解到對於氮化鎵垂直器件來説,垂直電流流也是一個必要條件,以儘量減少寄生效應和電流擁擠效應。如果使用的是本地襯底,可通過在晶片底部直接沉積金屬來實現。對於外來襯底,可通過在晶體管區域下方局部移除襯底來實現。典型的工藝是蝕刻(用於硅襯底)或激光剝離(用於藍寶石襯底)。圖 6 顯示了由此產生的結構以及器件圖片和 ID-VD 曲線;為確保高導電性,使用了鈦/鋁背面觸點,並用銅金屬化加固。在 VD=1V 和 VG=20V 條件下提取時,0.52 平方毫米晶體管的最佳 RonA 測量值為 5.2 mOhmcm2。

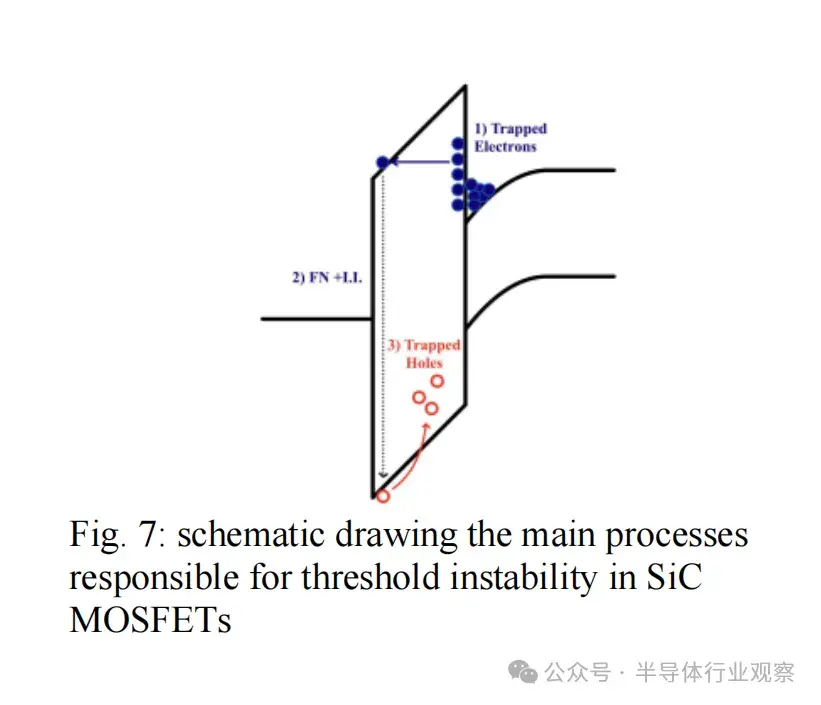

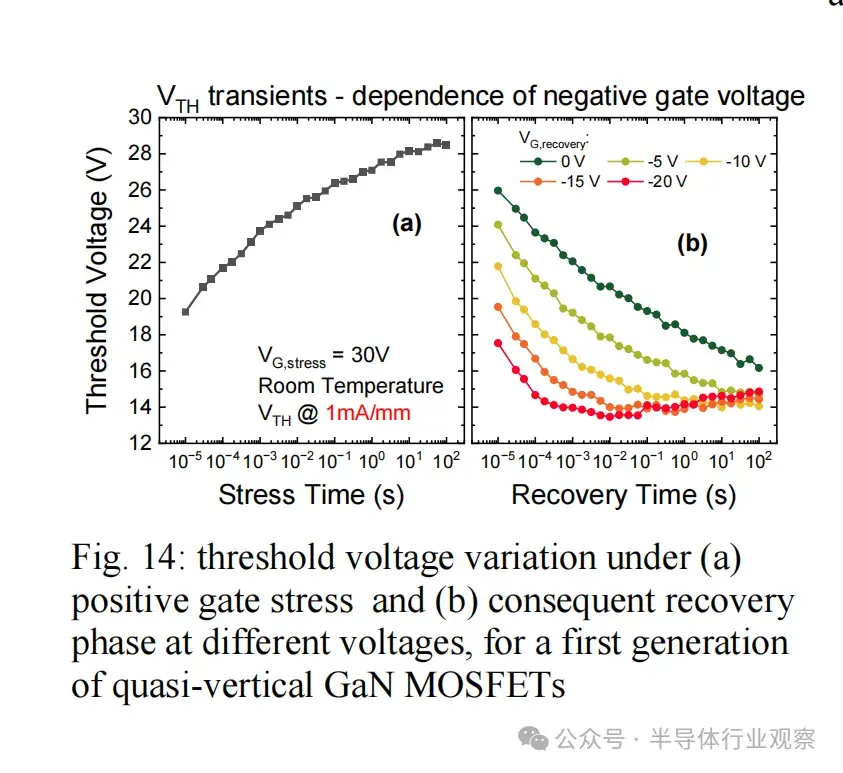

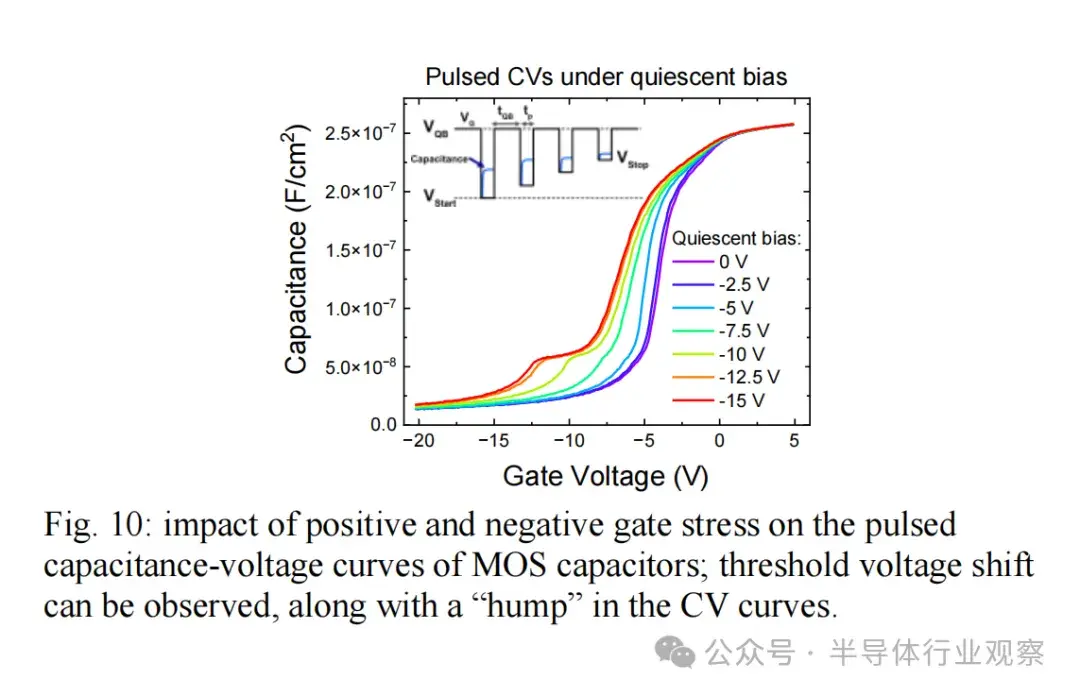

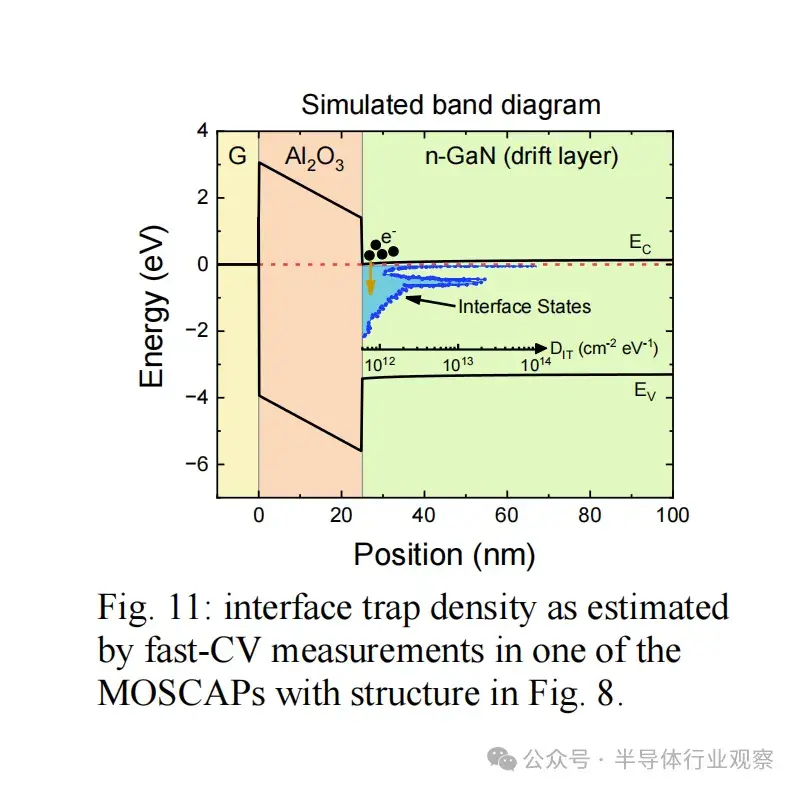

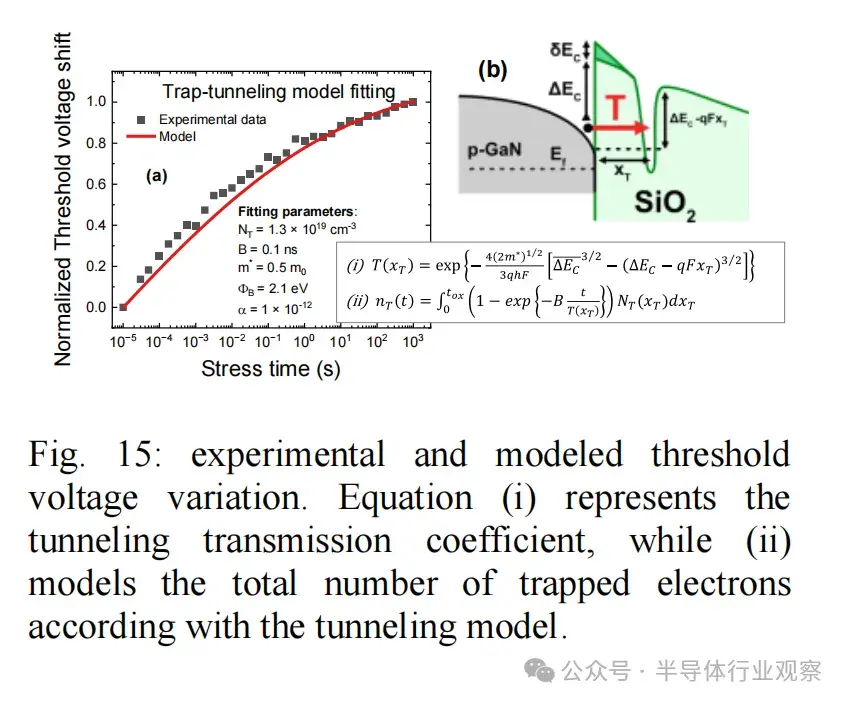

碳化硅器件在正柵極應力作用下可能會出現顯著的閾值電壓偏移(0.5V-1 V )。典型的過程包括(圖 7a的邊界/界面態的電子捕獲 圖7b)衝擊電離引起的空穴捕獲。