大芯片,靠它們了_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。38分钟前

編者按:

在此前的ISSCC上,英特爾SVP Navid Shahriari發佈了題為《AI Era Innovation Matrix 》的演講。他指出,人工智能具有改變人類的潛力,它提高了我們快速準確地解決複雜問題的能力,並開啓了創新和理解的新領域。人工智能的發展速度之快是史無前例的,這要求系統層面的快速發展,從低功耗和邊緣人工智能設備到基於雲計算的計算,以及連接它們的通信網絡。這種對快速人工智能系統擴展的需求正在推動硅片、封裝、架構和軟件領域的創新前沿。

在演講中,Navid Shahriari介紹了一系列技術。在他看來,這些技術使行業能夠在從芯片到系統的各個層面取得顯著進步。他重申,人工智能 (AI) 的快速發展將傳統計算技術推向極限,需要可持續且節能的解決方案來實現並行計算系統的指數級擴展。計算行業必須滿足所有行業對計算能力、內存帶寬、連接性、高性能基礎設施和 AI 日益增長的需求。

在本文中,作者着重強調了圖 1.1.1 所示的技術矩陣的進步,從軟件和系統架構到硅片和封裝。每個領域的進步都是必要的,但整個系統必須共同優化,以最大限度地提高性能、功耗和成本。強大的生態系統夥伴關係和新穎的設計方法對於高效的共同優化和更快的上市時間至關重要,為 AI 的變革潛力奠定了基礎。

芯片微縮一直是半導體行業進步的基本驅動力,並且仍然是創新矩陣的基石。硅片路線圖由非增量晶體管和互連架構進步、High NA EUV 光刻以及相關的掩模和建模解決方案實現。每代技術的功能擴展和改進都由設計技術協同優化 (DTCO) 流程指導,該流程設定並推動邏輯、內存和模擬/混合信號功率、性能、面積 (PPA) 和成本擴展的整體目標。設計和工藝技術之間的這種迭代循環對於實現持續的硅片微縮優勢至關重要。

一、RibbonFET

RibbonFET 是一種全柵極晶體管,超越了 FinFET 架構,提供性能擴展和工作負載靈活性 [1]。不同的帶狀寬度可在同一技術基礎上為不同的性能和效率需求提供定製解決方案。

二、PowerVia

PowerVia Power Via 是一種高產量背面供電技術,它集成了晶體管的供電,將 IR 壓降降低了 5 倍,併為信號路由提供了額外的正面佈線。它滿足所有 JEDEC 熱機械應力要求,零故障,並在硅片中顯示出超過 5% 的頻率優勢。值得一提的是,英特爾 18A 是英特爾領先的工藝節點,將提供業界首個 RibbonFET 和 PowerVia 技術的組合。

三、Hign NA EUV 優勢

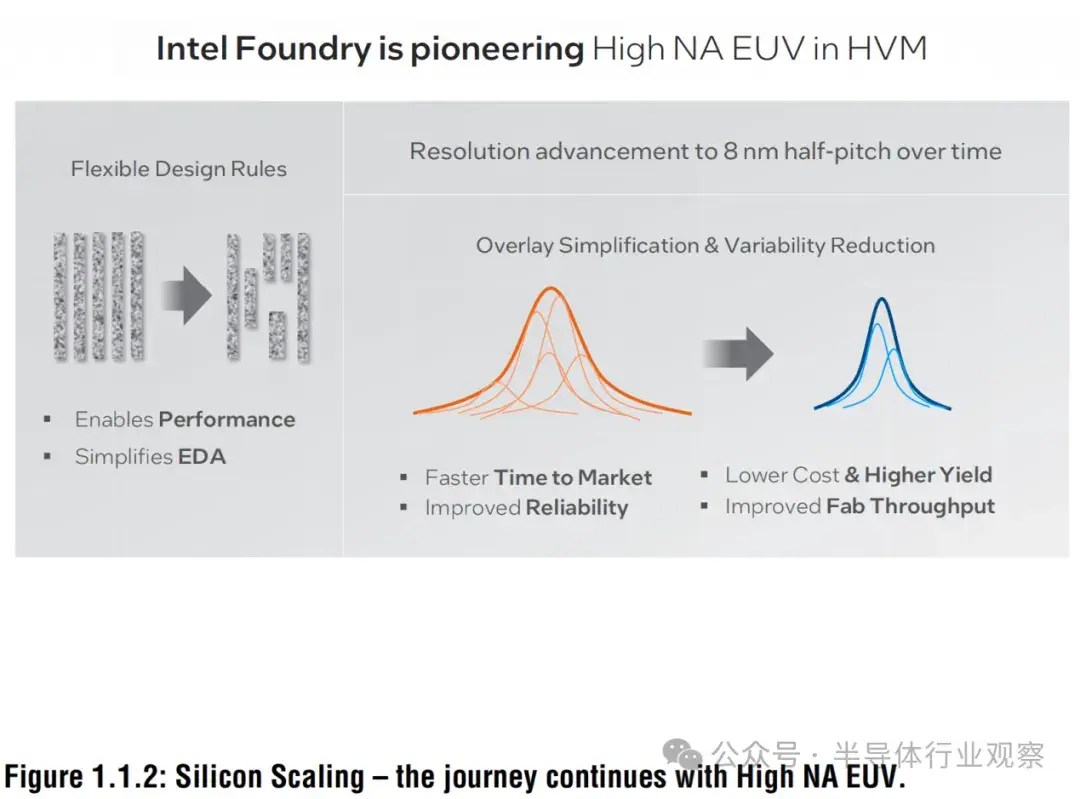

High NA EUV 可實現靈活的設計規則,減少寄生電容並提高性能 。它通過降低設計規則複雜性和多重曝光需求來簡化電子設計自動化 (EDA) 的各個方面。Intel 14A 正面互連針對High NA 單次曝光圖案進行了優化,提高了良率和可靠性(圖 1.1.2)。

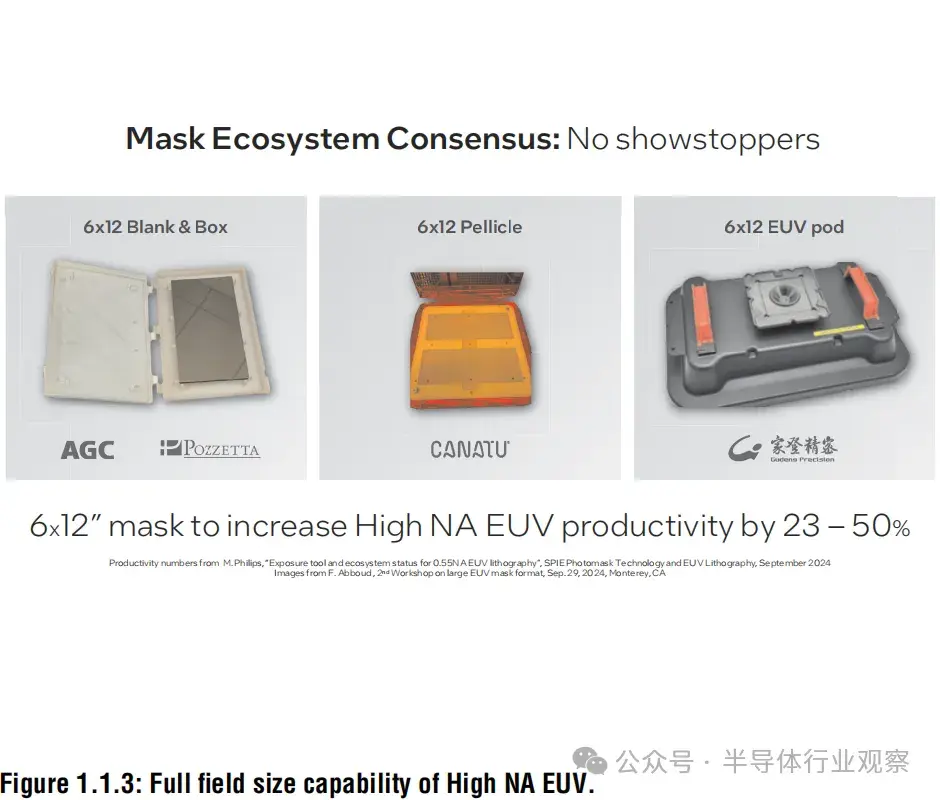

High NA EUV 工具的成像場(imaging field size)較小,但英特爾已開發出跨邊界電縫合芯片的解決方案。EDA 生態系統正在創建支持這一點的工具,而掩模生態系統則致力於實現無需光罩縫合的全場尺寸能力(圖 1.1.3),從而將生產率提高 23-50%。

High NA EUV 光刻需要先進的建模和掩模解決方案。英特爾使用 AI 和機器學習來實現準確性,同時管理計算成本。曲線掩模提高了圖案空間利用率、工藝窗口,並顯着降低了可變性。

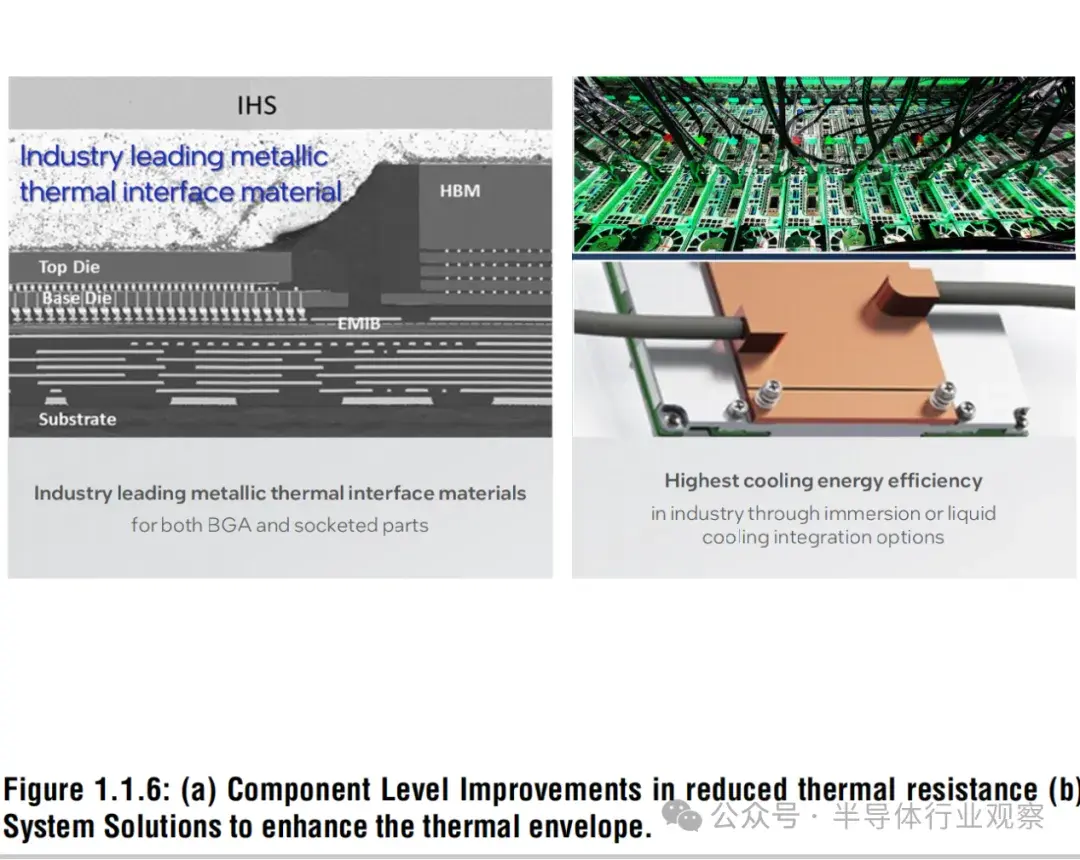

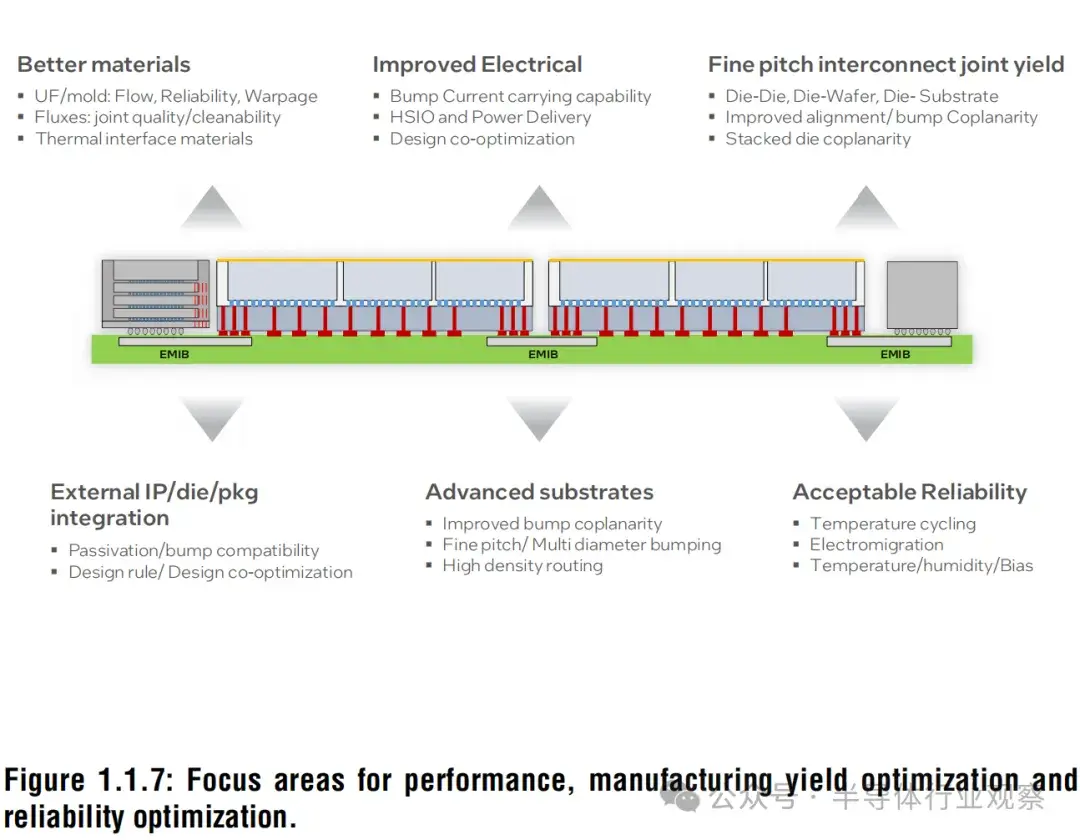

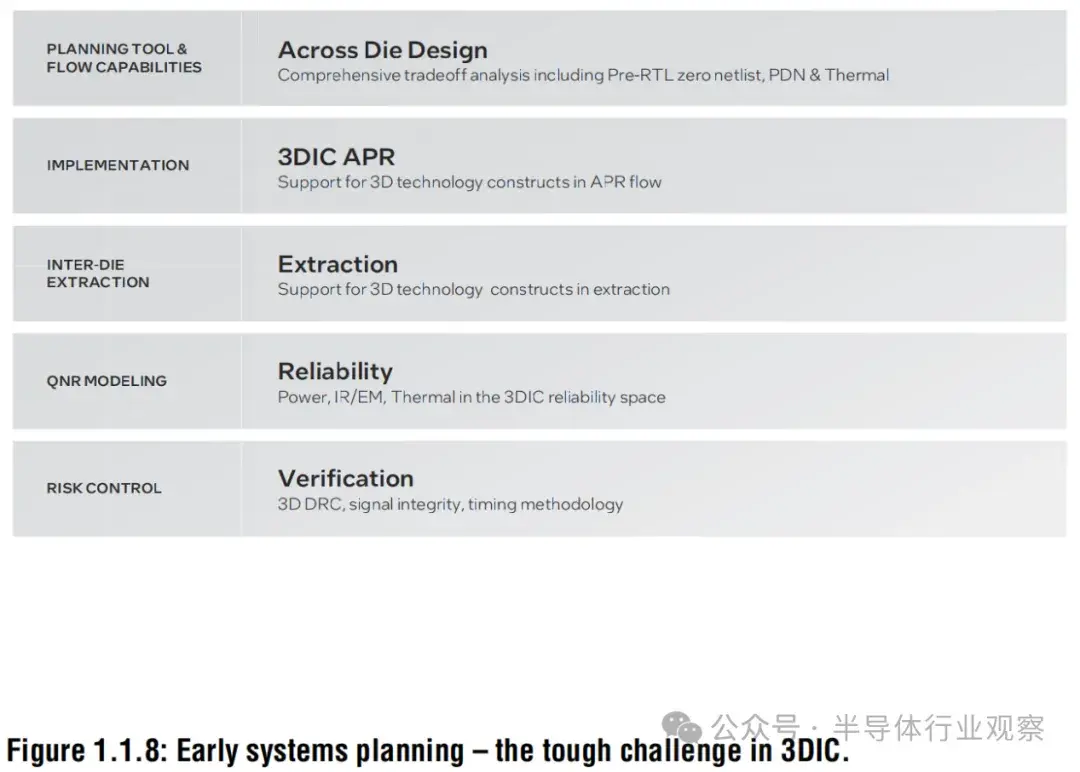

3D 集成電路 (3DIC)、封裝和組裝

隨着數據處理需求的增長,在更小的面積上實現更高的計算能力並降低能耗至關重要。3DIC 技術通過異構集成降低成本和佔用空間,通過更高的帶寬提高性能,並通過垂直堆疊降低功耗。先進節點上的基礎芯片對於實現硅通孔 (TSV) 和先進接口、無縫集成 3D 元素至關重要。

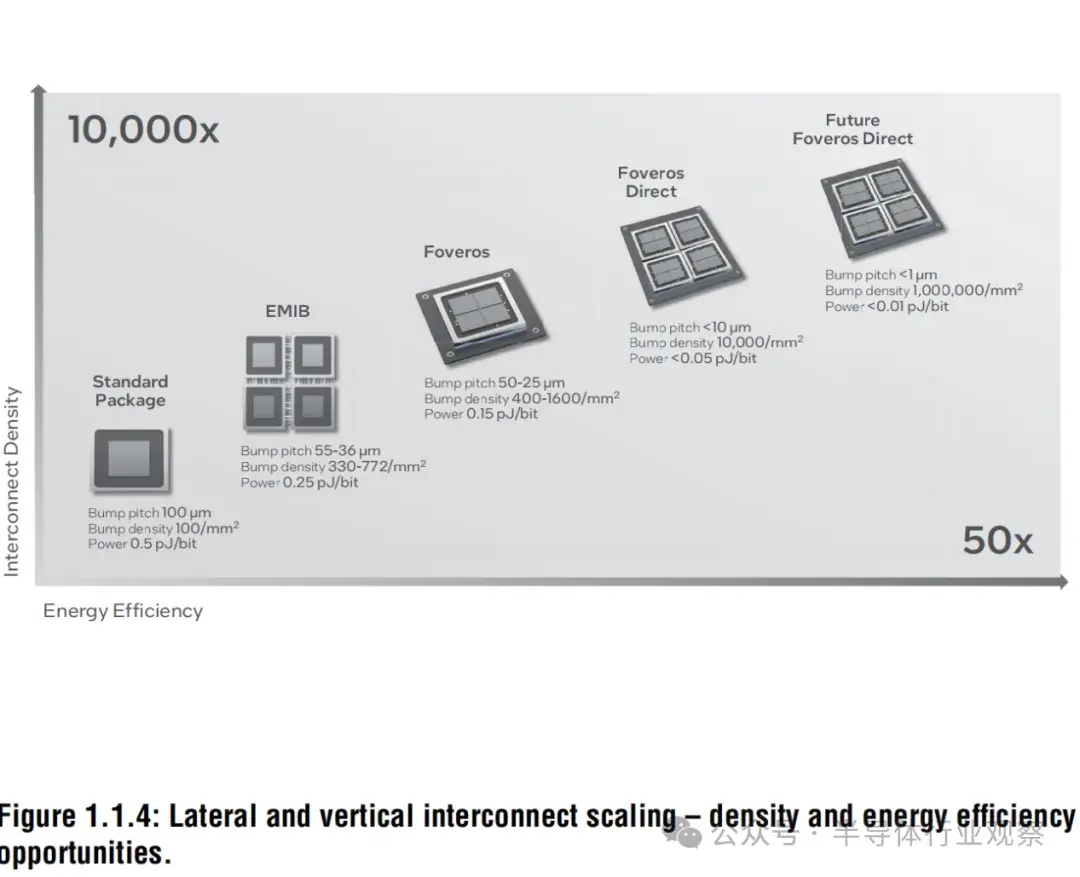

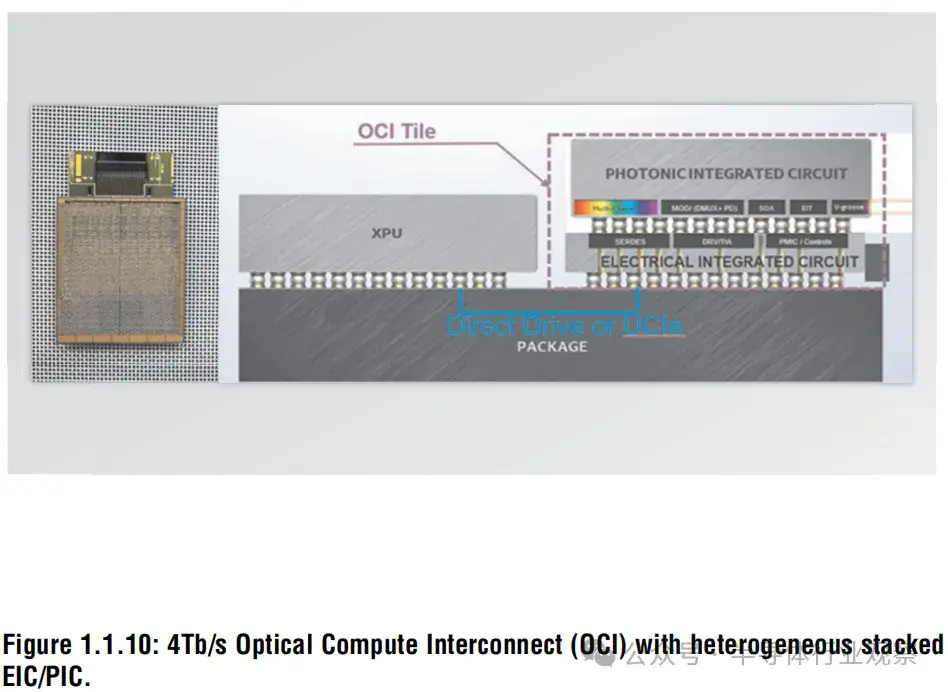

並行 AI 工作負載的指數級擴展給互連帶寬密度、延遲和功率帶來了壓力。如上所述,通過使用密集的 2.5D 和 3D 組裝技術更緊密地集成組件,可以改善這三個指標。新的封裝技術通過最小化 GPU 之間非常昂貴的(價格和功率)互連來提供更好的總擁有成本 (TCO)。傳輸每位數據的能量與通道損耗成比例 。這種權衡推動了行業規範的定義,例如 UCIe,用於低功耗、高密度封裝通信。UCIe 在 <1pJ/bit 時每毫米芯片周長可實現高達 1.35TB/s 的速度。

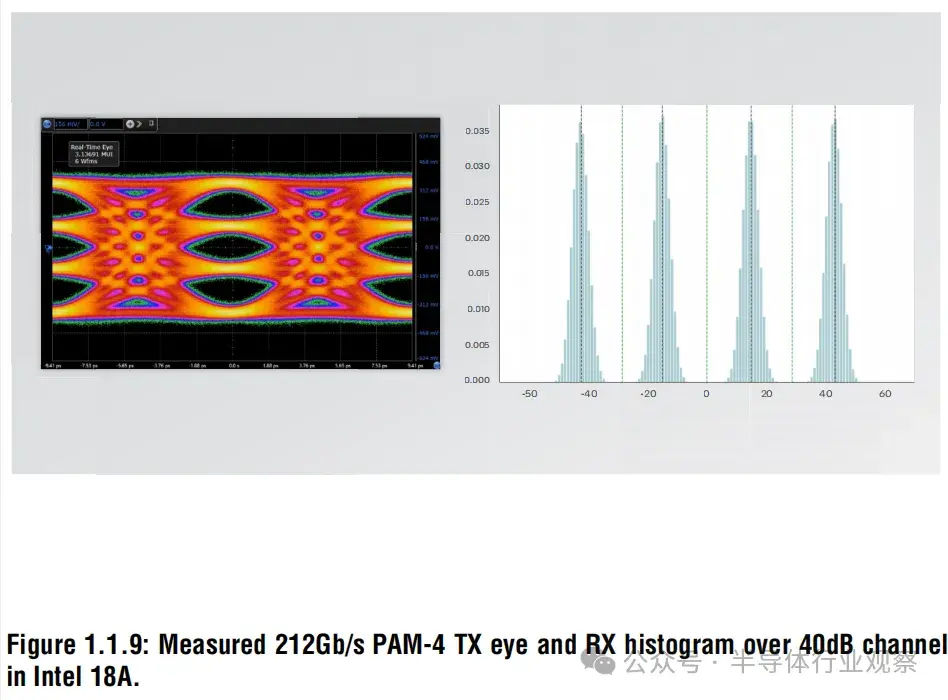

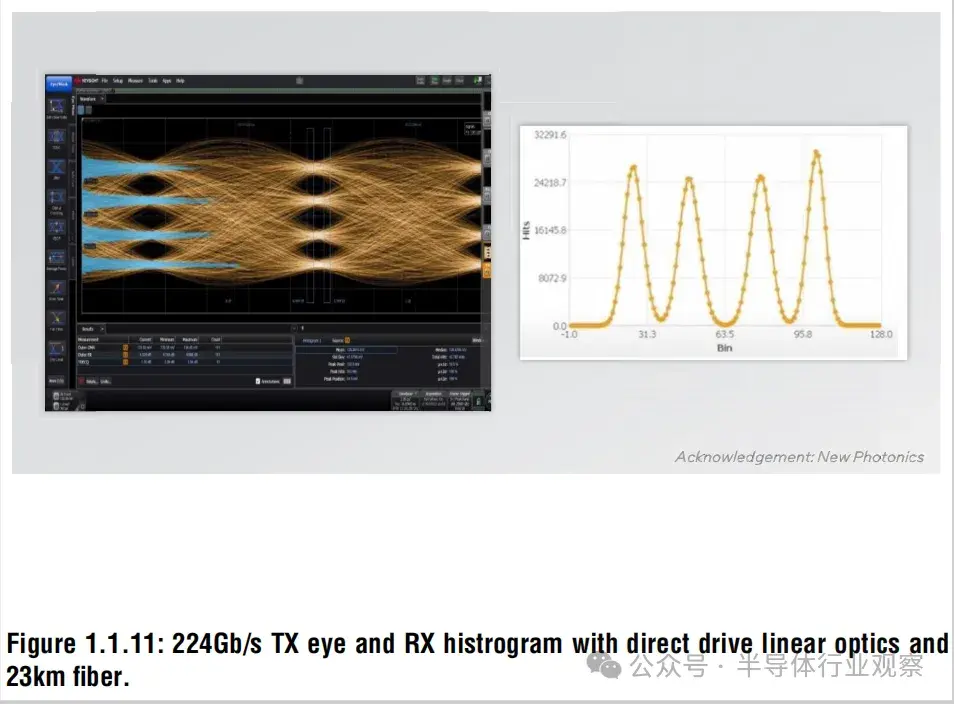

電路板和機架內的較長互連構成了擴展網絡拓撲中的高帶寬域,需要增加數據序列化以考慮實際連接器信號密度,從而擴大總帶寬。每通道串行數據速率每 3-4 年按 2 倍縮放,包括以太網、PCIe 和 OIF-CEI 等行業規範。最新生產的有線 SerDes 已達到 212Gb/s PAM4,以 4-6pJ/bit 的速度支持機架內(約 1 米範圍)通信。模擬電路的每比特能量和數字均衡都繼續受益於工藝技術的擴展。

添加更多重定時器可以擴大覆蓋範圍,但會增加功率、延遲和成本。這種經驗權衡導致在從海底電纜到機架到機架網絡等一系列應用中採用光互連。此外,使用光學器件將高帶寬域的覆蓋範圍擴展到機架之外符合 AI 的擴展網絡策略。因此,光互連將需要移入機架以擴展帶寬,

並達到可接受的功率範圍。正在開發共封裝光學器件 (CPO) 和直接驅動線性光學器件等技術來實現這一轉變。

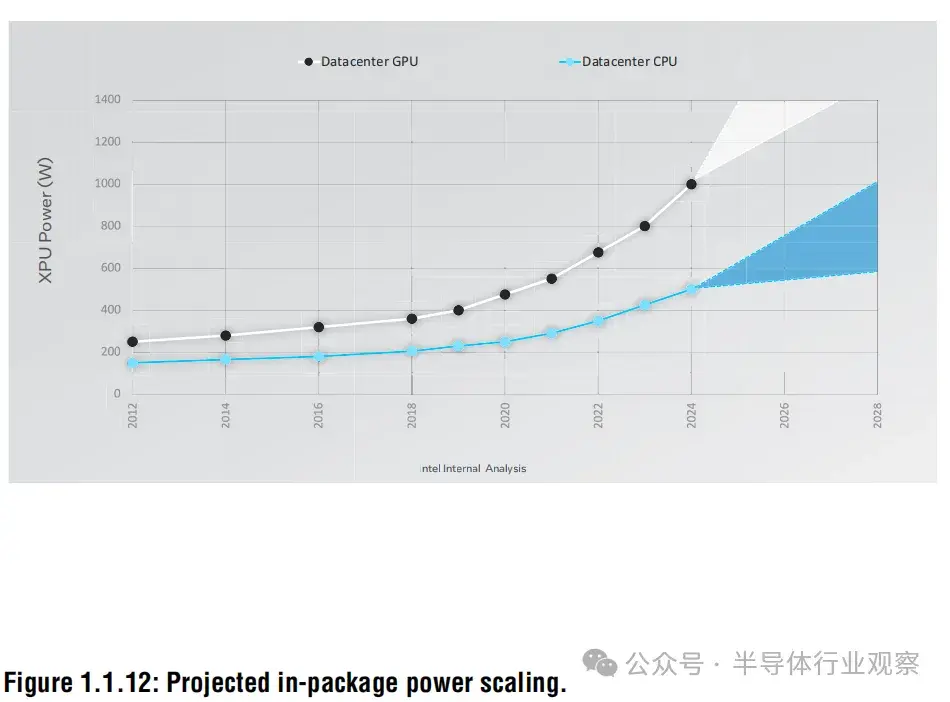

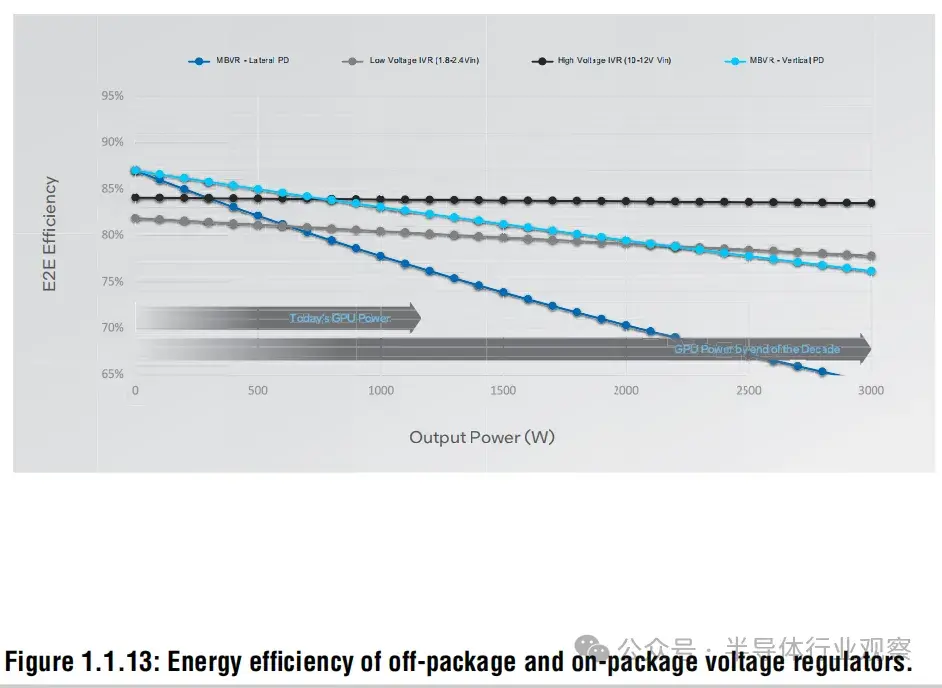

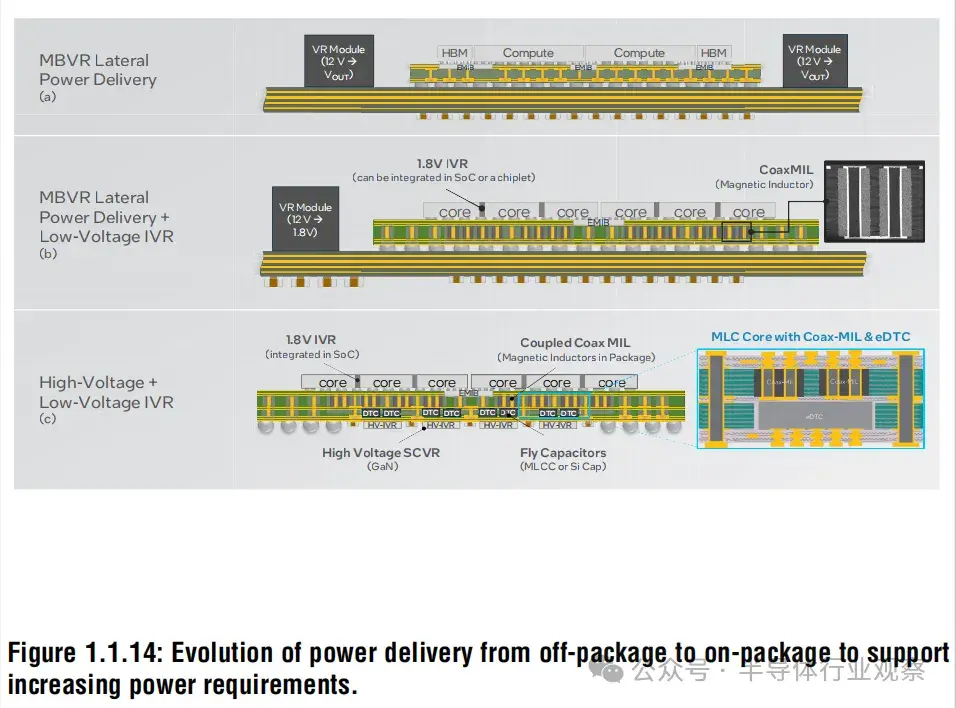

用於 AI 等並行工作負載的每封裝功率正在迅速擴大(圖 1.1.12)。為封裝供電的常見方法是主板電壓調節器 (MBVR:mother board voltage regulators)(圖 1.1.14(a))。這些調節器將板級電源(例如 12V)降低到封裝上芯片使用的電壓(VOUT)。無論是放置在封裝旁邊(橫向 MBVR)還是封裝下方(垂直 MBVR),MBVR 提供的電流密度都無法跟上未來高性能芯片的步伐。

為此,我們需要解決方案將電壓轉換更靠近芯片,並具有高電流密度、轉換效率和調節帶寬。一個解決方案是使用完全集成的電壓調節器 (FIVR:fully integrated voltage regulators ),將電源轉換的最後一步帶到封裝上(圖 1.1.14(b))。在封裝上進行最終電壓降壓可通過降低給定功率的電流來減少將電源軌佈線到封裝上時的能量損失(圖 1.1.13)。

除了集成到 SoC 中的 FIVR 之外,英特爾還開發了基於 CMOS 的獨立 2.4V IVR 芯片,該芯片使用英特爾的高密度電容器 (HDMIM) 技術開發了具有連續可擴展電壓轉換比的開關電容穩壓器 (SCVR:switched-cap voltage regulator) 。如果使用現有的 MBVR 架構,封裝內功率容量進一步擴展至 1-2kW 以上,則穩壓器效率將出現不可接受的下降,如圖 1.1.12 所示。通過將高壓 (12V) 功率轉換集成到封裝上,可以緩解此問題。12V 穩壓器集成將減少傳輸到封裝中的電流,從而減少I2R 損耗。

使用氮化鎵 (GaN) 等寬帶隙工藝技術可以使高壓轉換器具有比基於硅的解決方案更高的效率和密度。然而,功率轉換器的封裝實現需要更高的開關頻率和集成驅動器,而這在僅使用 GaN 的工藝上是無法支持的。

使用硅 CMOS 製造 GaN 器件可以為高壓功率轉換器的封裝集成提供更多機會,因為它可以在同一芯片上設計 CMOS 驅動器和 GaN 功率 FET。為此,英特爾最近展示了一項在同一 300 毫米晶圓上結合硅基 GaN 技術的技術 。該技術可支持輸入電壓高達 12V 的高壓 IVR 選項,從而實現 1-2 kW 以上的功率擴展。

架構和軟件

下一代計算架構必須推動系統性能指標(如每瓦性能-美元-毫米²)的指數級改進,同時解決熱和功率完整性挑戰。創新應通過先進的封裝和硅工藝堆疊和互連晶圓和小芯片來實現有凝聚力的系統。此外,它們還必須支持無縫集成各種工作負載的定製加速器 。

軟件是創新矩陣的重要組成部分,必須通過開源生態系統中的協作、標準化和互操作性來發展。自動化應增強安全性並簡化流程,而高度優化的軟件對於高效利用硅資源至關重要。在數千個 GPU 上分發軟件會帶來巨大的帶寬和延遲挑戰,例如高性能計算。人工智能軟件將成為微調系統元素、確保無縫集成和實現顯著進步的關鍵。

超越傳統計算

神經形態和量子計算等技術對於實現 AI 擴展所需的效率和速度突破至關重要。自 2018 年以來,全球超過 250 個實驗室都在使用英特爾的 Loihi 研究芯片,該芯片表明,採用 CMOS 工藝技術製造的神經形態芯片可以為廣泛的示例算法和應用帶來數量級的增益 。雖然其中許多示例涉及目前與當今的軟件和 AI 方法不兼容的新型大腦啓發算法,但一類新興技術表明,在不久的將來,當今廣泛使用的深度學習和轉換器方法將實現 1000 倍的增益 。

這些神經形態創新對於將先進的 AI 功能擴展到在即時設置下運行的功率、延遲和數據受限的智能設備至關重要。量子計算代表了一種新範式,它利用量子物理的力量以比傳統計算快得多的速度解決複雜問題。它有望徹底改變行業並解決關鍵問題,包括氣候變化、化學工程、藥物設計和發現、金融和航空航天設計。穩步推進將這項變革性技術從實驗室轉移到工程領域,為有用的近期應用提供客户解決方案至關重要。英特爾獨特的量子研究方法涵蓋了整個計算堆棧,包括量子比特製造 、用於量子比特控制的低温 CMOS 技術、軟件、編譯器、算法和應用程序。

憑藉 50 多年的大規模晶體管制造經驗,英特爾正在利用其成熟的技術開發硅自旋量子比特,作為量子計算可擴展性的最佳前進方向。英特爾還在投資定製設計的低温探測器等功能,這些功能可大大加快英特爾量子測試和驗證工作流程。量子計算硬件的現狀還不具備對當今人工智能產生直接影響的穩健性和規模。人工智能使用量子計算機面臨的另一個挑戰是如何將大量數據輸入這些複雜的機器。

然而,一旦我們擁有了可擴展的容錯量子計算機,就會帶來明顯的好處。量子計算機可以比傳統計算機更快地執行復雜計算,這可以加快人工智能模型的訓練和分析速度。量子計算的兩個關鍵原理是疊加和糾纏,它們可以同時探索多種解決方案,這可以直接有利於人工智能模型的訓練和優化。並行分析大量數據的可能性也可以提高人工智能識別模式的能力,例如在圖像或語音中。可以開發直接優化以利用量子特性的新人工智能算法,而不是使用傳統人工智能算法。

最後,量子計算機不應被視為傳統計算機的替代品,而應被視為特殊應用的計算加速器。因此,未來人工智能的系統解決方案可能會利用經典計算和量子計算的混合實現。

生態系統協作

快速開發下一代先進計算系統需要整個行業生態系統就此創新矩陣展開協作。與整個技術堆棧中的最終用户和合作夥伴(從製造到設計工具,從 IP 到系統設計再到軟件)進行合作,確保開發過程符合市場需求和時間表、環境可持續,並利用整個生態系統的關鍵學習和開發。系統級共同優化需要密切協作才能取得快速進展。跨學科專業知識和跨戰略伙伴關係的知識共享對於高效解決問題和加速開發週期至關重要。利用跨行業優勢並避免重複努力將使團隊能夠更有效地工作。

行業挑戰與機遇

近二十年前,CPU 時鐘頻率擴展面臨一個困境——持續追求指數級性能改進在功率密度方面遇到了瓶頸。

其結果是產生了一套新的並行處理器架構以及一系列用於硅、封裝和散熱、互連、電力輸送和核心架構的支持技術。今天,我們處於類似的境地,指數級性能擴展(這次是為了支持 AI)遇到了功率、連接性和成本方面的根本挑戰。

再次,我們的系統的增量擴展是不夠的,我們需要新的方法來解決這個問題——一個 AI 創新矩陣。從工藝技術擴展到 3DIC 系統設計,再到電力輸送、互連和核心架構,工程挑戰層出不窮。我們需要綜合這些領域的創新優勢,以可製造、可持續且經濟高效的方式滿足行業對計算能力的需求。