台積電尖端SoW-X封裝技術,2027年量產_風聞

半导体产业纵横-半导体产业纵横官方账号-赋能中国半导体产业,我们一直在路上。32分钟前

本文由半導體產業縱橫(ID:ICVIEWS)綜合

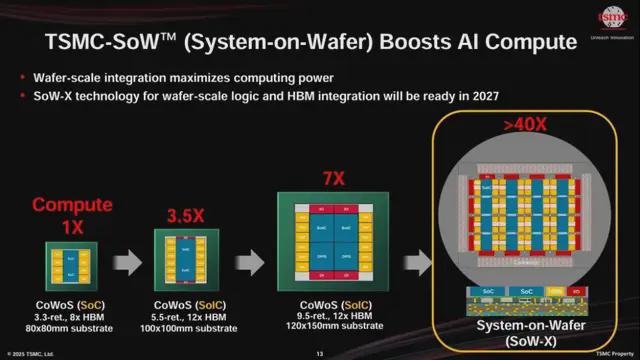

台積電計劃在2027年量產9.5倍光罩尺寸的CoWoS。

台積電 2025 年北美技術論壇不僅公佈了最先進的A14 邏輯製程,在先進封裝領域也有多項重要信息公佈。

台積電表示該企業計劃在2027 年量產 9.5 倍光罩尺寸的 CoWoS,從而能夠以台積電先進邏輯技術將 12 個或更多的 HBM 堆疊整合到一個封裝中,這意味着單封裝可容納的芯片面積將相較此前進一步提升。

而在更大的晶圓尺寸封裝系統方面,台積電則帶來了SoW 系統級晶圓技術的新版本 SoW-X。該技術採用不同於 SoW-P 的 Chip-Last 流程,計劃於 2027 年量產。

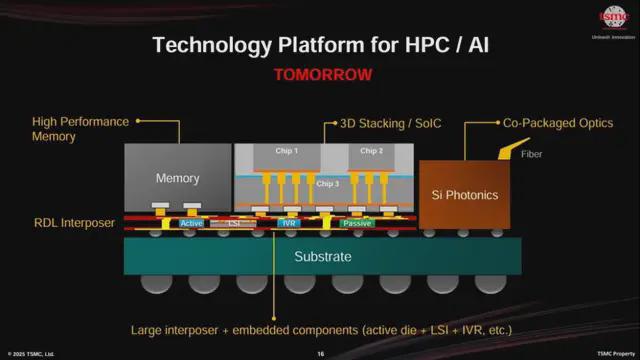

台積還介紹了其它一系列高性能集成解決方案,包括用於HBM4 的 N12 和N3 製程邏輯基礎裸晶(Base Die)、運用 COUPE 緊湊型通用光子引擎技術的 SiPh 硅光子整合。

未來的 HPC / AI 芯片需要複雜的整合集成

未來的 HPC / AI 芯片需要複雜的整合集成

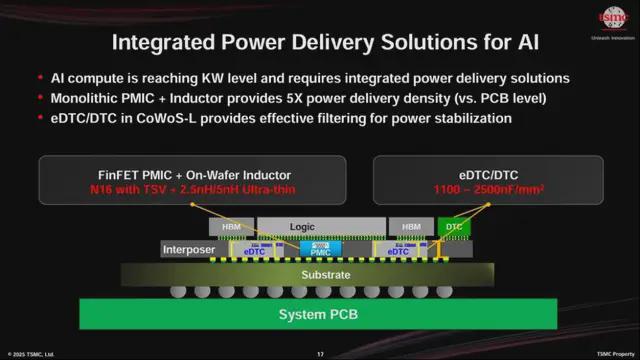

此外台積電也公佈了用於 AI 的新型集成型電壓調節器 / 穩壓器 IVR。與電路板上的獨立電源管理芯片 PMIC 相比,IVR 具備 5 倍的垂直功率密度傳輸。

自2020年以來,台積電的晶圓系統集成技術(InFO-SoW)已成功應用於如Cerebras和特斯拉等公司的尖端產品中,其中特斯拉的Dojo超級計算機所搭載的晶圓級處理器就是這一技術的標誌性產物。晶圓級設計通過直接在整片硅晶圓上構建處理器,實現了前所未有的核心間通信速度、性能密度以及能效,然而,其複雜度與成本也相應增加,限制了廣泛應用。

面對人工智能(AI)與高性能計算(HPC)領域日益增長的需求,簡單的二維擴展已無法滿足。台積電通過融合其InFO-SoW與集成芯片系統(SoIC)兩大封裝技術,推出了CoW-SoW技術,旨在實現晶圓級芯片的垂直堆疊。這項技術不僅允許邏輯芯片與內存芯片在同一晶圓上進行堆疊,還提供了前所未有的靈活性,使得不同製造工藝技術可以在同一封裝內共存,從而優化成本效益與性能表現。

特別是在內存集成方面,台積電特別強調了CoW-SoW在結合HBM4(第四代高帶寬內存)上的潛力。HBM4憑藉其2048位的超寬接口,有望通過與邏輯芯片的緊密集成,解決AI及HPC工作負載對高帶寬、低延遲內存的迫切需求。這種集成方式不僅極大提升了數據傳輸速度,還有效降低了功耗,為持續增長的計算密集型應用提供了理想的解決方案。

台積電業務開發副總裁Kevin Zhang在研討會中表達了對CoW-SoW技術的堅定信心,認為它將成為客户提升AI集羣或超級計算機性能的關鍵路徑。他強調,晶圓級集成不僅不再是理論設想,而是正在與客户合作轉化為實際產品,標誌着台積電正引領行業向更高層次的系統集成邁進。

今年3月SK海力士宣佈,推出面向AI的超高性能DRAM新產品12層HBM4,並且全球首次向主要客户提供了其樣品。SK海力士強調:“以引領HBM市場的技術競爭力和生產經驗為基礎,能夠比原計劃提早實現12層HBM4的樣品出貨,並已開始與客户的驗證流程。公司將在下半年完成量產準備,由此鞏固在面向AI的新一代存儲器市場領導地位。”

此次提供的12層HBM4樣品,兼具了面向AI的存儲器必備的世界最高水平速率。其容量也是12層堆疊產品的最高水平。

此產品首次實現了最高每秒可以處理2TB(太字節)以上數據的帶寬1。其相當於在1秒內可處理400部以上全高清(Full-HD,FHD)級電影(5GB=5千兆字節)的數據,運行速度與前一代(HBM3E)相比提高了60%以上。

帶寬(Bandwidth):HBM產品中的帶寬,是指一個HBM封裝每秒可處理的數據總容量。

同時,公司通過在該產品上採用已在前一代產品獲得競爭力認可的Advanced MR-MUF工藝,實現了現有12層HBM可達到的最大36GB容量。通過此工藝控制了芯片的翹曲現象,還有效提升了散熱性能,由此最大程度地提高了產品的穩定性。

SK海力士從2022年的HBM3開始,在2024年陸續實現了8層和12層HBM3E產品量產,通過恰時開發和供應HBM產品,維持了面向AI的存儲器市場領導力。

SK海力士AI Infra擔當金柱善社長(CMO,Chief Marketing Officer)表示:“公司為了滿足客户的要求,不斷克服技術侷限,成為了AI生態創新的領先者。以業界最大規模的HBM供應經驗為基礎,今後也將順利進行性能驗證和量產準備。”

未來,隨着HBM4的大量出貨,再加上SoW的技術加持,芯片性能有望提升到新的台階。

*聲明:本文系原作者創作。文章內容系其個人觀點,我方轉載僅為分享與討論,不代表我方贊成或認同,如有異議,請聯繫後台。