台積電公佈N2 2nm缺陷率:比3、5、7nm都要好_風聞

半导体产业纵横-半导体产业纵横官方账号-赋能中国半导体产业,我们一直在路上。53分钟前

台積電N2 製程工藝的缺陷密度低於N3、N5和N7製造節點。

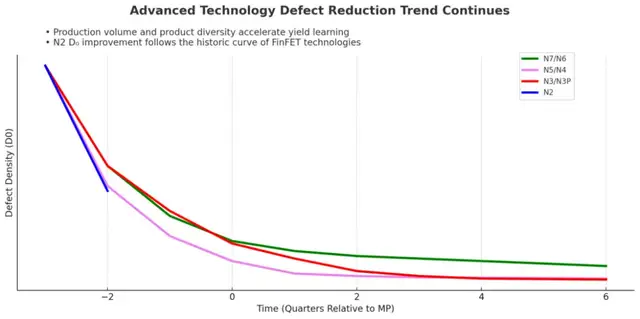

上週台積電在北美技術研討會上公佈了其N2 製程工藝相對於同期上一代工藝的缺陷密度 (D0) 。據該公司稱,該工藝的缺陷密度低於N3 、N5 和 N7 製造節點。此外,ComputerBase發佈的幻燈片顯示,N2 工藝距離量產還有兩個季度的時間,這意味着台積電有望按預期在 2025 年第四季度末開始生產 2 納米級芯片。

儘管台積電的N2工藝是該公司首個採用環柵(GAA)納米片晶體管的工藝技術,但該節點的缺陷密度低於處於同一開發階段的前代產品(比量產(MP)提前了兩個季度)。N3 /N3P、N5 /N4和N7/N6這幾代產品都採用了眾所周知的鰭式場效應晶體管(FinFET)。因此,儘管N2是台積電首個採用GAA納米片晶體管的工藝技術,但在實現量產(HVM)之前,其缺陷密度下降的速度比前代產品更快。

產量和產品多樣性仍然是加速缺陷密度改善的關鍵驅動因素。更大的產量和使用相同工藝的多樣化產品能夠更快地識別和糾正缺陷密度和良率問題,從而使台積電能夠優化缺陷學習週期。台積電表示,其N2製造技術比前代產品獲得了更多新的流片(因為台積電現在冒險為智能手機和高性能計算客户生產N2芯片),因此缺陷密度下降曲線基本證明了這一點。

考慮到引入全新晶體管架構所帶來的風險因素,N2 的缺陷減少率與之前基於 FinFET 的節點保持一致,這一點尤為重要。這表明台積電已成功將其工藝學習和缺陷管理專業知識轉移到新的 GAAFET 時代,且未遭遇重大挫折。

在半導體行業中,“良率”是一個關鍵指標,指的是從一片硅晶圓中切割出的可用芯片通過質量檢測的比例。如果晶圓廠的良率較低,製造相同數量的芯片就需要更多的晶圓,這會推高成本、降低利潤率,並可能導致供應短缺。

此前有消息稱,台積電的2nm 製程的良率已達到 60% 以上,這一數據還有較大提升空間。據悉,通常相應芯片良率需要達到70% 或更高才能進入大規模量產階段。

近日還有報道稱,英特爾本就是台積電先進製程主要客户之一,去年2月,英特爾當時的CEO帕特·基辛格證實,已將兩款處理器關鍵的運算塊(Compute tile)首度交給台積電生產,這兩款產品就是後來的Intel Core Ultra 200V系列筆記本電腦處理器(代號Lunar Lake),與該公司首款AI PC桌上型處理器Intel Core Ultra 200S系列(代號Arrow Lake)。其中,運算芯片塊以台積電N3B製程生產,GPU芯片塊以台積電N5P製程生產,SoC與I/O芯片塊則以台積電N6製程生產。

據瞭解,目前台積電與英特爾雙方在2nm製程已經有了一款合作產品,外界推測,可能是英特爾明年要推出PC處理器Nova Lake其中的運算芯片塊。

過去幾年,台積電的競爭對手三星電子在4nm、3nm和2nm的良率方面一直存在問題。三星代工廠在為高通生產驍龍8 Gen1時,4nm良率非常糟糕,以至於後來高通放棄三星代工,轉而選擇台積電。台積電製造了驍龍8+ Gen 1 AP。最終,三星代工廠將4nm 良率提高到70%。

然而,三星代工廠在3nm方面仍然存在良率問題,據報道,這導致3nm Exynos 2500 AP的生產延遲。因此,三星可能不得不支付額外的資金,為所有Galaxy S25系列手機配備更昂貴的驍龍8 Elite SoC,而不是其內部的Exynos 2500。低良率會增加芯片的成本,因為需要額外的硅晶圓來製造足夠的芯片來完成訂單。

儘管三星代工也在為低良率問題苦苦掙扎,但其已取得一定成效。據悉,三星的2nm工藝的良率已從年初的20-30% 提升至 40% 以上,遠超 3 納米時期的表現。業界認為,若 Exynos 2600 按計劃搭載於 2026 年一季度發佈的 Galaxy S26,將為三星代工業務注入強心劑,助力吸引外部客户。

*聲明:本文系原作者創作。文章內容系其個人觀點,我方轉載僅為分享與討論,不代表我方贊成或認同,如有異議,請聯繫後台。