RISC-V歐洲峯會,一系列新進展來了!_風聞

半导体产业纵横-半导体产业纵横官方账号-赋能中国半导体产业,我们一直在路上。1小时前

本文由半導體產業縱橫(ID:ICVIEWS)編譯自eetimes

本文由半導體產業縱橫(ID:ICVIEWS)編譯自eetimes

RISC-V,跑出加速度。

在巴黎舉行的 RISC-V 歐洲峯會 2025 的主題演講中,Codasip 歐洲、中東和非洲地區銷售副總裁 Emmanuel Till-Vattier 簡要介紹了產品更新,包括從 Arm 快速遷移到 RISC-V 的新可能性、新的核心定製功能以及能力硬件增強 RISC 指令 (CHERI) 內存保護方面的最新進展。

Till-Vattier 表示,Codasip 專注於三個目標:“一是讓 RISC-V 內核易於定製。二是確保其安全。三是確保安全性。”

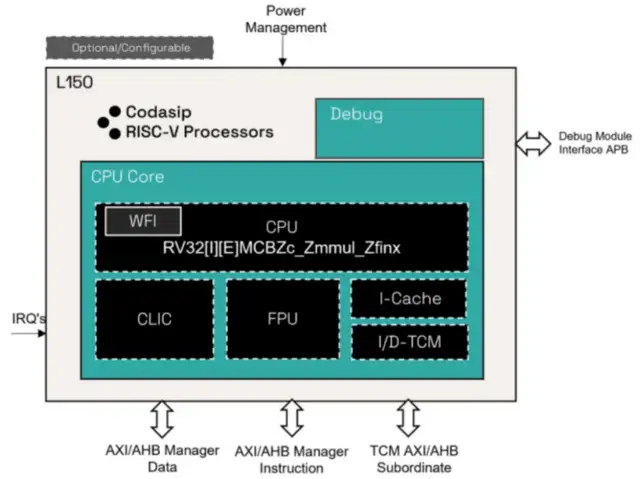

5 月初,這家總部位於慕尼黑的公司推出了 Codasip L150,這是一款專為即時嵌入式應用設計的“低功耗、面積高效、三級、32 位 RISC-V 核心”。

Till-Vattier 表示:“它的一個優點是可定製,但它也有一個非常小的浮點單元,一個符合 RISC-V Zfinx 擴展的單精度浮點。”

Codasip 聲稱,通過部署實現 Zfinx RISC-V 擴展的面積高效浮點單元,並結合座標旋轉數字計算機 (CORDIC) 硬件加速器來處理自定義指令,L150 實現了約 38.9 倍的性能提升,而硅片面積的增加卻微乎其微。

Till-Vattier 還重點介紹了 Codasip 使用通用微控制器軟件接口標準 (CMSIS)(用於 DSP 和神經網絡)加速 RISC-V 嵌入式應用程序的方法。CMSIS 最初的設計目的是使 Arm 應用程序能夠在 Arm 處理器產品組合中無縫運行。通過利用 Codasip 的 CMSIS-DSP 和 CMSIS-NN 庫,為傳統 Arm 內核開發的應用程序可以在針對領域優化的 RISC-V 實現上運行,而無需進行軟件修改。

Till-Vattier 還重點介紹了 Codasip 使用通用微控制器軟件接口標準 (CMSIS)(用於 DSP 和神經網絡)加速 RISC-V 嵌入式應用程序的方法。CMSIS 最初的設計目的是使 Arm 應用程序能夠在 Arm 處理器產品組合中無縫運行。通過利用 Codasip 的 CMSIS-DSP 和 CMSIS-NN 庫,為傳統 Arm 內核開發的應用程序可以在針對領域優化的 RISC-V 實現上運行,而無需進行軟件修改。

“大約九個月前,我們就決定,在嵌入式領域,讓軟件從 Arm 移植到 RISC-V 變得儘可能簡單至關重要,”Till-Vattier 説道。“由於 Arm 的 CMSIS 是一個非常流行的 API,我們決定移植 CMSIS-RTOS、CMSIS-NVIK、CMSIS-DSP 和 CMSIS-NN。所有這些 API 都已由 Codasip 移植到 RISC-V,這意味着如果您正在使用 CMSIS,遷移過程將非常順利、輕鬆。”

他補充道:“我們還提供定製加速器和定製指令,以提高 Arm 的性能。”

根據劍橋大學的定義,CHERI 通過新的架構特性擴展了傳統的硬件 ISA,從而實現細粒度的內存保護和高度可擴展的軟件隔離。Codasip 最近與劍橋大學合作開發了 RISC-V 的 CHERI 擴展,併發布了 CHERI-RISC-V 的首個商業實現:X730 處理器。

Till-Vattier 表示:“CHERI 是一項令人着迷的網絡安全關鍵技術,我們現在可以在 Cheri X730 應用處理器上演示 CHERI Linux 的運行。”

隨着汽車行業日益轉向 RISC-V,Codasip 開發了 L730 嵌入式內核,以滿足汽車安全保障需求。它符合 ISO/SAE 21434 和 ISO 26262 標準,最高可達 ASIL D 完整性等級。Codasip L730 還支持 RISC-V 標量加密擴展,並利用 CHERI 來提升硬件層面的安全性。

最後,Till-Vattier 指出,Codasip 已獲得資格,作為歐洲超級計算項目“歐洲 RISC-V 數字自主”(DARE)的一部分,提供基於 RISC-V 的通用處理器。DARE項目旨在構建一個超級計算機堆棧,該堆棧採用在歐洲設計和開發的高性能、節能的 RISC-V 處理器和加速器。歐盟已承諾為該項目的第一三年階段提供 2.4 億歐元。

“在地緣政治帶來諸多不確定性的時代,重要的不僅僅是你的知識產權有多好,還有你的知識產權來自哪裏,”蒂爾-瓦蒂爾説道。“根據Codasip的政策,我們所有的研發都在歐洲大陸進行,這對我們的一些客户來説很重要。”

另一家公司,也發佈了其RISC-V產品的最新進展。

如何利用可擴展的 RISC-V NPU 架構增強 AI 計算?

在短短兩年內,Semidynamics 已經“從帶有 AI 的 RISC-V 發展到帶有 RISC-V 的 AI”。

2023 年,這家總部位於西班牙巴塞羅那的初創公司走出隱身模式,推出了一系列完全可定製的 64 位 RISC-V 內核,旨在處理機器學習、人工智能和高性能計算所需的大量數據。同樣在 2023 年,Semidynamics 發佈了可定製的矢量單元,每週期可提供高達 2048 位的計算能力,實現前所未有的數據處理能力,並採用 Gazzillion Misses 技術“隱藏內存牆,保持機器正常運行”,Politz 説道。

Gazzillion Misses 為每個內核提供高達 128 次緩存未命中,避免了等待主內存處理數據的空閒時間。隨後,Semidynamics 發佈了RISC-V 張量單元來處理人工智能所需的矩陣乘法。它集成了該公司完全可定製的 64 位 RISC-V 內核和矢量單元,Gazzillion Misses 技術不斷向矢量單元提供數據,從而不會出現數據未命中。

5 月初,Semidynamics 推出了 Cervell,這是一款可擴展且可編程的 RISC-V 神經處理單元,它將 CPU、矢量和張量功能結合在“完全基於 RISC-V ISA 的單個計算元素中”,Politz 表示。

“我們希望將 RISC-V ISA 的優勢帶入前所未有的 NPU 市場。”

Politz 解釋説,大多數 NPU 都基於專有和“秘密”指令集。“AI 模型正在快速變化和發展,這使得確保現有芯片的硬件兼容性變得困難。RISC-V ISA 適用於現代並行工作負載。矢量指令在同一 ISA 下充當 GPGPU(通用圖形處理單元),能夠有效、高效地處理不斷增長的數據量。”

軟件支持可以基於通用的 RISC-V 工具鏈,並結合 ONNX 等開源方案。“這將使用户擁有前所未有的自由度,能夠應對模型變更和創新 AI 計算工作負載的部署,”Politz 説道。

ONNX 項目最初由微軟定義,它定義了 AI 模型的通用標準,所有主流 AI 框架都支持導入或導出 ONNX 格式的模型。Semidynamics 還開發了 Aliado,這是一款 RISC-V 軟件開發套件,用於對在定製 RISC-V 矢量引擎上運行的 AI 應用程序進行調試和微調。Aliado 與 ONNX Runtime 無縫集成。

該公司表示,Cervell NPU 專為加速矩陣密集型操作而設計,可實現更高的吞吐量、更低的功耗和即時響應。

Cervell 可在 2GHz 下提供高達 256 TOPS 的性能,並可從 C8 擴展到 C64 配置,使設計人員能夠根據應用需求調整性能——從緊湊邊緣部署中的 1GHz 8 TOPS INT8 到高端 AI 推理中的 256 TOPS INT4。

目標應用包括卷積 AI 網絡、轉換器、大型語言模型和生成 AI。

*聲明:本文系原作者創作。文章內容系其個人觀點,我方轉載僅為分享與討論,不代表我方贊成或認同,如有異議,請聯繫後台。