HBM5,或將在2029年到來_風聞

半导体产业纵横-半导体产业纵横官方账号-赋能中国半导体产业,我们一直在路上。10分钟前

本文由半導體產業縱橫(ID:ICVIEWS)綜合

本文由半導體產業縱橫(ID:ICVIEWS)綜合

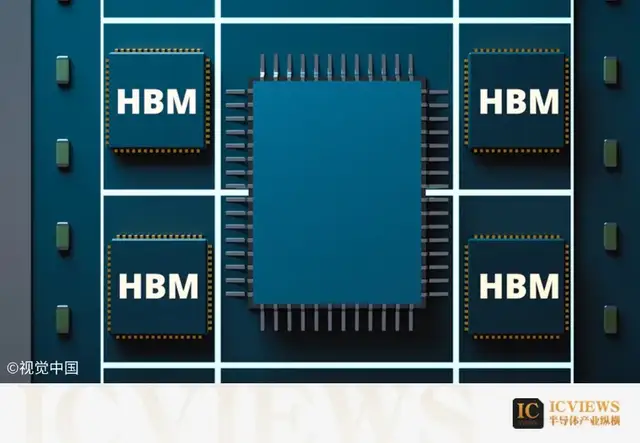

隨着HBM5的到來,冷卻的重要性將顯著提升。

據《The Elec》報道,韓國科學技術研究院 (KAIST) 教授 Joungho Kim 表示,隨着領先的內存製造商在 HBM 開發方面取得進展,一旦 HBM5 進入商業化階段(可能在 2029 年左右),冷卻技術預計將成為一個關鍵的競爭因素。

正如報告中所指出的,Kim 解釋説,雖然封裝目前是半導體制造的主要差異化因素,但隨着 HBM5 的到來,冷卻的重要性將顯著提升。他進一步指出,隨着從 HBM4 開始,基礎芯片開始承擔 GPU 的部分工作負載,導致温度升高,冷卻變得越來越關鍵。

Kim 強調,目前 HBM4 使用的液冷方法(將冷卻液施加到封裝頂部的散熱器上)在未來將面臨侷限性。為此,HBM5 結構預計將採用浸沒式冷卻,將基座芯片和整個封裝都浸入冷卻液中。

此前,韓國科學技術研究院(KAIST Teralab)公佈了HBM4至HBM8的技術路線圖,涵蓋2025年至2040年。該路線圖概述了HBM架構、冷卻方法、TSV密度、中介層等方面的進展。金教授還指出,正如報告所示,預計通過異構和先進的封裝技術,基礎芯片將轉移到HBM堆棧的頂部。

未來的 HBM 架構和冷卻創新

HBM的散熱問題是一個關鍵的挑戰。隨着存儲器產品的發展,散熱問題愈發嚴峻,導致這一問題的原因有多個:例如,由於表面積減少和功率密度增加,半導體微型化會直接影響產品的散熱性能;對於HBM這樣的DRAM堆疊產品,熱傳導路徑較長會導致熱阻增加,熱導性也會因芯片之間的填充材料而受限;此外,速度和容量的不斷提升,也會導致熱量增加。

若無法充分控制半導體芯片產生的熱量,可能會對產品性能、生命週期和功能產生負面影響。這是客户重點關注的問題,因為此類問題會嚴重影響其生產力、能源成本和競爭力。

報道稱,HBM7 需要嵌入式冷卻技術,以允許冷卻液在堆疊的 DRAM 芯片之間流動,為此,Kim 教授引入了流體硅通孔 (TSV)。除了標準 TSV 之外,還將採用新型通孔,包括熱通孔 (TTV)、柵極 TSV 和熱通孔 (TPV)。

HBM7 預計還將與高帶寬閃存 (HBF) 等新架構集成,其中 NAND 閃存採用 3D 堆疊結構,類似於 HBM 中的 DRAM。展望未來,正如報告中強調的那樣,HBM8 將直接在 GPU 上安裝內存。

鍵合技術是 HBM 性能的關鍵

此外,Kim 還表示,除了冷卻之外,鍵合也將成為決定 HBM 性能的另一個關鍵因素。Kim 表示,從 HBM6 開始,將引入一種結合玻璃和硅的混合中介層。

TrendForce也指出,DRAM 行業對 HBM 產品的關注度正日益轉向混合鍵合等先進封裝技術。各大 HBM 製造商正在考慮是否在 HBM4 16hi 堆疊產品中採用混合鍵合技術,但已確認計劃在 HBM5 20hi 堆疊產品中採用該技術。

晶圓鍵合也被稱為混合鍵合,即芯片垂直堆疊,通過硅穿孔(TSV)或微型銅線連接,I/O直接連接,沒有用到凸塊連接。根據芯片堆疊方式,還有分為晶圓到晶圓(wafer-to-wafer)、晶圓到裸晶(wafer-to-die)和裸晶到裸晶(die-to-die)。

現在的DRAM是在同一晶圓單元層兩側周邊元件,這會使表面積擴大,而3D DRAM則是基於現有的平面DRAM單元來做垂直堆疊,就像目前的3D NAND的單元垂直堆疊一樣。三星和SK海力士都計劃在不同DRAM晶圓上製造“單元”(Cell)和周邊元件(peripherals),然後再通過混合鍵合連接,這將有助於控制器件的面積、提高單元密度。

SK海力士曾在其第三代8層堆疊的HBM2E上進行過測試,使用混合鍵合製程後,通過了所有可靠性測試。SK海力士還評價了該HBM在高温下的使用壽命,檢查產品出貨後客户在芯片黏合過程中可能出現的潛在問題。目前,SK海力士計劃在新一代的HBM4上採用混合鍵合技術。

目前三星也在研究4F Square DRAM,並有望在生產中應用混合鍵合技術。4F Square是一種單元數組結構,與目前商業化的6F Square DRAM相比,可將芯片表面積減少30%。

另外,三星在其論文中指出,未來16層及以上的HBM必須採用混合鍵合技術。三星稱,降低堆疊的高度是採用混合鍵合的主因,內存高度限制在775微米內,在這高度中須封裝17個芯片(即一個基底芯片和16個核心芯片),因此縮小芯片間的間隙,是內存大廠必須克服的問題。

*聲明:本文系原作者創作。文章內容系其個人觀點,我方轉載僅為分享與討論,不代表我方贊成或認同,如有異議,請聯繫後台。