中國提出顛覆性的晶體管技術_風聞

半导体产业纵横-半导体产业纵横官方账号-赋能中国半导体产业,我们一直在路上。1小时前

本文由半導體產業縱橫(ID:ICVIEWS)編譯自eetime

在半導體技術領域,一個集成電路不僅可以在正面形成,還可以在背面形成的時代即將到來。

imec於2018年發佈的CFET(互補場效應晶體管)一直被視為繼FinFET和GAA之後,前景光明的下一代場效應晶體管。然而,在今年的VLSI研討會上,北京大學發佈的“倒裝堆疊晶體管(FFET)”卻引起了廣泛關注。

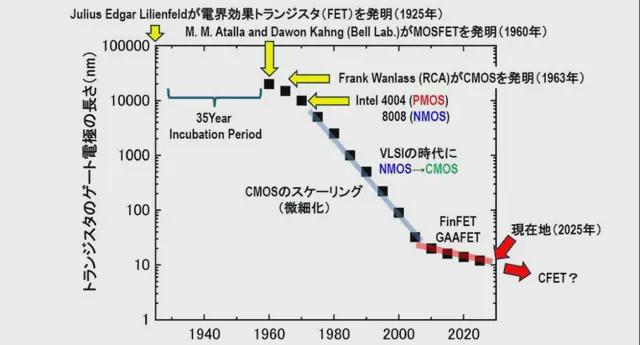

FET的發明和發展歷史2025年是場效應晶體管誕生100週年。

圖 1:場效應晶體管 (FET) 發明 100 週年。來源:VLSI Symposium 2025,特別研討會,Kazuhiko Endo 教授(東北大學)

場效應晶體管(FET)是一種利用半導體內部產生的電場來控制電流的晶體管。其基本原理由美國物理學家朱利葉斯·埃德加·利利菲爾德於1925年發明並獲得專利。然而,由於當時的技術水平,FET難以實現,因此這個想法在很長一段時間內都未能投入實際應用。

大約35年後,1960年,貝爾實驗室的馬丁·阿塔拉(Martin Atalla)和達翁·康(Dawon Kahng)發明了金屬氧化物半導體場效應晶體管(MOSFET),並在世界上首次成功使其運行。這種MOSFET成為後續半導體產業發展的基礎,併成為支撐集成電路鉅變的根本技術。

MOSFET技術不斷發展,1971年,英特爾發佈了用於計算器的“4004”處理器,該處理器採用了PMOS技術。1972年,英特爾又發佈了“8008”處理器,該處理器採用了NMOS技術,能夠進行更復雜的計算。

但是,“4004”採用以空穴為載流子的PMOS結構,因此工作速度較慢;“8008”採用以電子為載流子的NMOS結構,雖然可以實現高速工作,但存在功耗高的問題。

為了應對這一問題,美國RCA公司的弗蘭克·萬拉斯(Frank Wanlass)於1963年發明的CMOS(互補MOS)技術引起了人們的關注,該技術比PMOS和NMOS更早出現。CMOS是一種將PMOS和NMOS成對組合在一起的技術,可同時實現低功耗、高速運行和高集成度。CMOS技術最初發明時,由於製造複雜性,並未得到廣泛應用,但其真正價值很快得到了重新評估。

從“重塑CMOS”到FinFET和GAA時代20世紀80年代,隨着VLSI(超大規模集成電路)時代的到來,CMOS佔據了主導地位。CMOS標誌着半導體技術飛速發展的轉折點,這是因為CMOS電路的微型化使得同時實現高速化、低功耗化和高集成度成為可能。

這一演變的理論基礎是IBM的羅伯特·H·丹納德(Robert H. Dennard)於1974年提出的“丹納德縮放定律”。丹納德證明,通過以一定的速率降低晶體管的尺寸和電壓,可以提高運行速度等性能,同時降低功耗。

此後,半導體行業一直遵循這一“縮放定律”不斷推進微型化。然而,自2000年代中期以來,這一定律已達到其物理和電氣極限。即使進一步微型化,運行速度也不再按比例提高。

為了克服這一挑戰,業界不斷探索新技術。2011年,英特爾成功量產採用FinFET(一種三維晶體管)的處理器。此外,2022年,三星電子成為全球首家在3納米工藝中量產採用環繞柵極(GAA)結構的邏輯半導體的公司。2025年,台積電將緊隨其後推出2納米工藝,英特爾也將緊隨其後推出其“18A”工藝。

因此,2025年將是新型晶體管結構“GAA”應用開花的一年。下面,筆者將詳細探討GAA發展至今的歷史歷程。

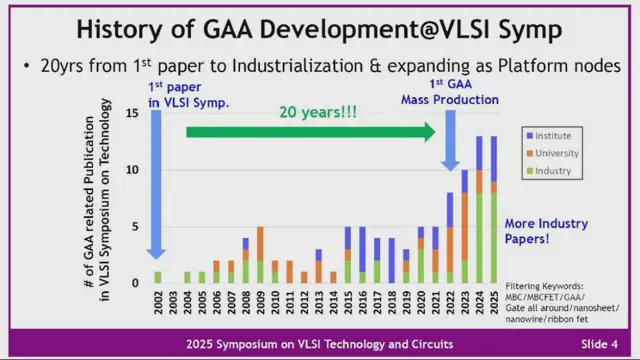

三星的GAA技術三星的YY Masuoka在VLSI會議上以《GAA “G”enuine “A”rchitecture for “A”I generation》為題發表演講。

根據Masuoka的研究,關於GAA的首次演講是在2002年的VLSI研討會上進行的(圖2)。此後,與GAA相關的演講數量一直在波動,但自2020年以來一直呈上升趨勢,2022年,三星開始量產配備GAA的邏輯半導體。此外,預計台積電和英特爾將在2025年效仿。

圖 2:自 2002 年 GAA 論文發表以來 20 年的量產情況。來源:VLSI Symposium 2025,特別研討會,YY Masuoka(三星)

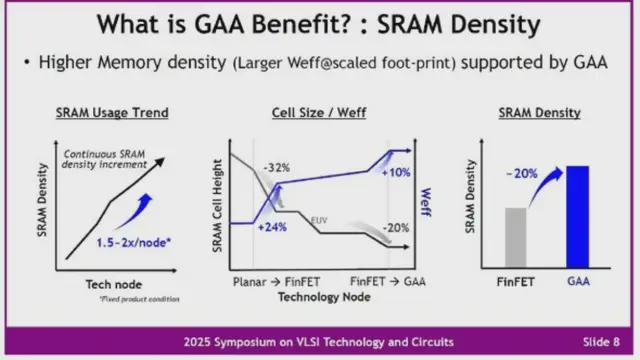

如圖 3 所示,GAA 的優勢已通過 SRAM 驗證。如圖所示,隨着技術節點的進步,SRAM 的密度每代都需要增加 1.5 到 2 倍,但通過將 FET 從平面型轉換為 FinFET,再轉換為 GAA,可以降低 SRAM 單元高度,同時增加晶體管 Weff(有效溝道寬度)。因此,通過從 FinFET 轉換為 GAA,可以將 SRAM 的密度提高約 20%。

Masuoka 在這張幻燈片上得出的第一個結論是“GAA 是未來芯片擴展的必需品。

圖 3 結論 1:GAA 是未來實現芯片擴展的必需品。 來源:VLSI Symposium 2025,特別研討會,YY Masuoka(三星)

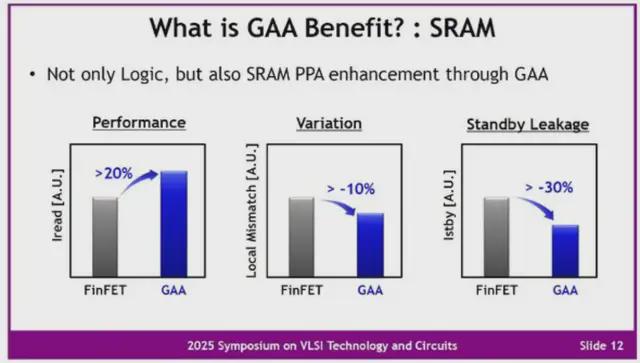

GAA 是 PPA 增強的必要條件接下來,Masuoka 展示了通過將晶體管結構從 FinFET 轉換為 GAA,可以將 SRAM 性能提高 20% 以上,將局部失配減少 10% 以上,並將待機漏電流降低 30% 以上(圖 4)。換句話説,通過採用 GAA,可以同時改善 PPA(功耗、性能和麪積)。

Masuoka 在這張幻燈片上的第二個結論是“GAA 是 PPA 增強的必要條件。 ”

圖4 結論-2,GAA 對於 PPA 增強至關重要。來源:VLSI Symposium 2025,特別研討會,YY Masuoka(三星)

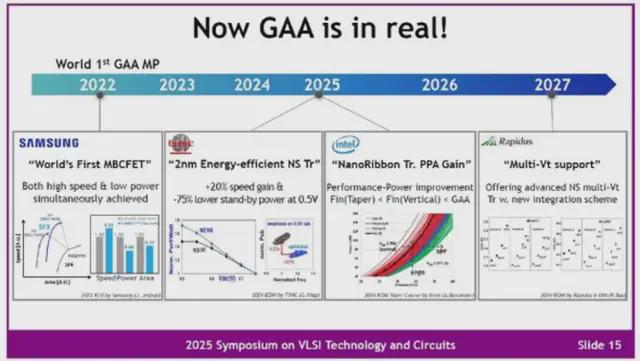

Masuoka進一步表示,三星將在2022年全球率先開始量產採用GAA的邏輯芯片,台積電和英特爾將在2025年緊隨其後,而Rapidus也計劃在2027年量產GAA。在結論3中,他總結道:“現在GAA已經實現。”(圖5)。

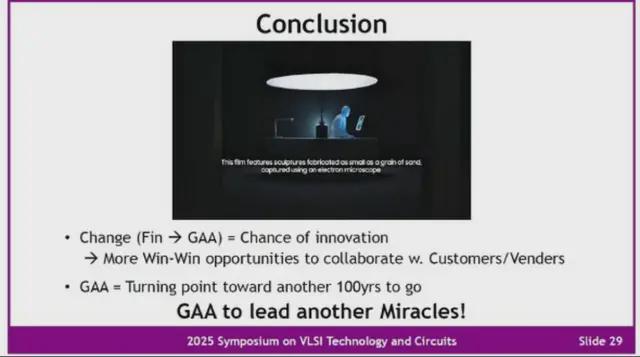

益岡最終的結論是,這將是GAA未來100年的關鍵轉折點,並強有力地發出“GAA將引領另一個奇蹟。 ”(圖6)。

圖5 結論-3,現在GAA已經實現。來源:VLSI Symposium 2025,特別研討會,YY Masuoka(三星)

圖6 結論:GAA 將引領另一個奇蹟。來源:VLSI Symposium 2025,特別研討會,YY Masuoka(三星)

那麼,GAA的未來又將如何發展呢?

其中一項領先的候選技術——北京大學吳恆教授公佈的“倒裝堆疊晶體管”(Flip FET)——引起了廣泛關注。

中國論文數量快速增長圖 7顯示了 VLSI 研討會上技術(設備/工藝)和電路領域按地區提交和接受的論文數量。

首先,從圖7A中各地區投稿論文數量的趨勢來看,可以明顯看出,中國的投稿數量自2021年左右以來持續快速增長,到2025年更是達到了驚人的283篇。同時,從圖7B中錄用論文數量來看,中國共提交了50篇論文,位居第三,僅次於第一名的美國(56篇)和第二名的韓國(55篇)。然而,考慮到中國近年來的顯著增長,2026年後中國躍居第一的可能性很大。

接下來,圖8顯示了技術與電路領域論文總數排名前11的機構。中國在這方面的表現同樣引人注目,北京大學排名第4(12篇論文),清華大學排名第6(8篇論文),澳門大學和復旦大學均位列第11(各5篇論文),取得了長足的進步。

圖8:技術與電路領域論文被接受數量最多的Top 11機構。來源:作者根據2025 VLSI Symposium新聞發佈會資料製作

簡而言之,中國高校在國際半導體會議VLSI研討會上的影響力正在迅速提升。此外,在中國高校的演講者中,有很多二三十歲的年輕研究人員。換句話説,可以説,中國的年輕力量主導了今年的VLSI研討會。

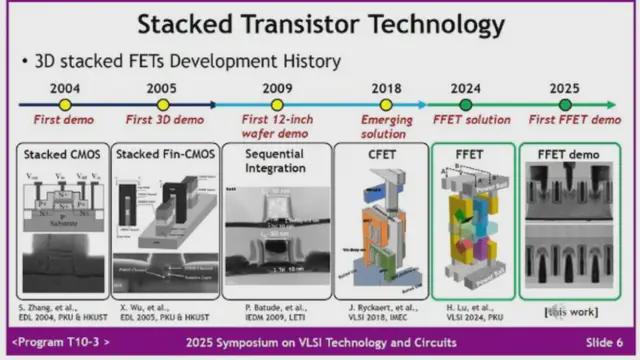

3D堆疊晶體管的歷史和北京大學倒裝堆疊晶體管的出現北京大學吳恆教授表示,2025年將是自2004年首次演示3D堆疊CMOS以來的大約20年(圖9)。在此期間,2005年成功演示了3D堆疊FinFET,2009年歐洲CEA-Leti演示了第一塊3D堆疊12英寸晶圓。

圖 9 3D 堆疊 FET 的歷史。來源:VLSI Symposium 2025,T10-3,吳恆(北京大學),幻燈片“在 300 毫米晶圓上首次實驗演示倒裝 FET(FFET)中的雙面 N/P FET,用於亞 1nm 節點的堆疊晶體管技術。”

隨後,在2018年的VLSI研討會上,imec發佈了CFET(互補場效應晶體管),這是一種垂直配置的PMOS和NMOS。在台積電等尖端邏輯半導體制造商的路線圖上,CFET排在GAA之後。換句話説,在FinFET和GAA之後,FET將進入CFET時代,這似乎已成為半導體行業的共識。

然而,就在這其中,北京大學吳恆教授團隊在2024年VLSI研討會上提出了一種名為倒裝堆疊晶體管(FFET)的新型3D堆疊晶體管概念,並於2025年宣佈成功演示了其運行。

在下一節中,筆者將解釋Flip FET概念背後的技術背景。

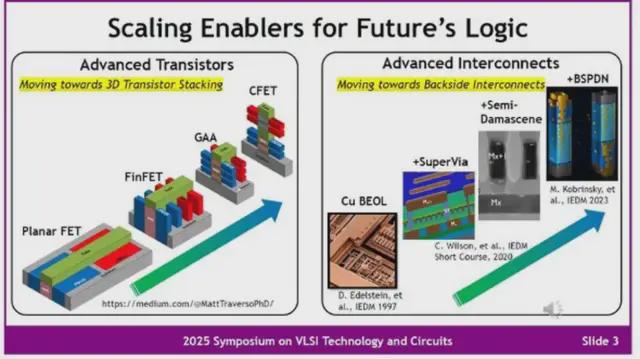

2nm及後續採用的GAA和背面電源在2nm及以後的工藝中,FET將從GAA過渡到CFET,並將採用背面電源輸送網絡(BSPDN)作為佈線技術(圖10)。

圖 10 晶體管從 GAA 變為 CFET,佈線至 BSPDN 。來源:VLSI Symposium 2025,T10-3,吳恆(北京大學),幻燈片來自“在 300 毫米晶圓上對倒裝場效應晶體管 (FFET) 中的雙面 N/P FET 進行首次實驗演示,用於亞 1nm 節點的堆疊晶體管技術。”

BSPDN是一種在晶圓表面形成晶體管和信號佈線,然後在晶體管背面構建電源線的技術。英特爾將這項技術稱為“Power Via”,預計從“18A”工藝開始採用。

需要 BSPDN(或 Power Via)的主要原因有兩個:

第一,傳統的供電方式是從晶體管和信號線的上方供電,在較長的供電路徑上容易產生電壓下降。而通過從背面直接供電,可以顯著降低電壓下降。

第二,過去,晶體管上方有十幾層的信號線和粗電源線混雜在一起,信號線和電源線很容易相互干擾,給佈線設計帶來了很大的限制。通過將晶圓正面的信號線與背面的電源線分開,可以消除兩者之間的干擾,從而可以提高晶圓正面的佈線密度。

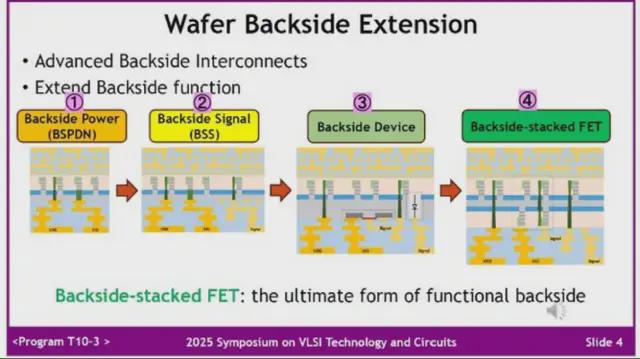

Flip FET 背後的理念如上所述,BSPDN 有望在 GAA 世代中得到全面應用。在此背景下,我們將使用圖 11解釋Flip FET 背後的概念。

圖 11:如果我們不僅製作電源線,還在背面製作信號線和場效應晶體管 (FET) 會怎樣?來源:VLSI Symposium 2025,T10-3,吳恆(北京大學),幻燈片來自“在 300 毫米晶圓上首次實驗演示倒裝場效應晶體管 (FFET) 中的雙面 N/P FET,用於亞 1 納米節點的堆疊晶體管技術。”

從 2nm 開始採用 BSPDN。如果要在背面創建電源線,那麼創建信號線(背面信號)不就可以了嗎?還有一個想法是在背面安裝某種裝置。既然已經走到這一步,如果還在背面創建電源線、信號線和 FET 會怎麼樣?這樣一來,就設計出了在正面製作FET和信號線,在背面製作FET、信號線和電源線的方案。那麼,為了實現這個想法,究竟採用了什麼樣的工藝呢?

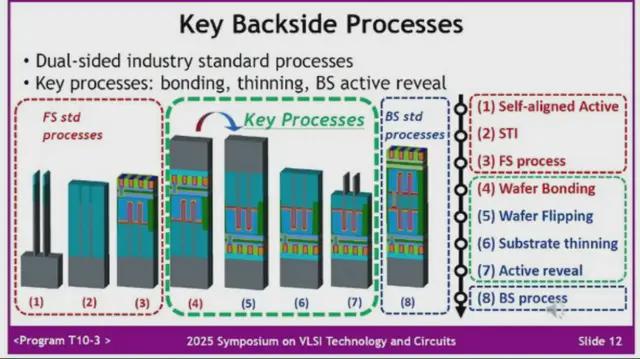

令人驚歎的Flip FET工藝將參考圖描述在正面和背面形成FET的工藝。

圖 12. 在正面 (FS) 和背面 (BS) 分別形成 FET 。來源:VLSI Symposium 2025,T10-3,吳恆(北京大學),幻燈片來自“在 300 毫米晶圓上對倒裝 FET(FFET)中的雙面 N/P FET 進行首次實驗演示,用於亞 1nm 節點的堆疊晶體管技術。”

(1)採用自對準有源技術形成場效應晶體管(FET)溝道區。(2)形成元件隔離(淺溝槽隔離,STI)結構。(3)在正面形成NMOS晶體管及其佈線層。(4)將另一片晶圓鍵合到已經形成的硅晶圓上。(5)將晶圓倒裝,這是該工藝的關鍵點。(6)倒裝後,對上層晶圓進行減薄。(7)進一步去除硅,露出有源層。(8)在背面形成PMOS晶體管及其佈線層。

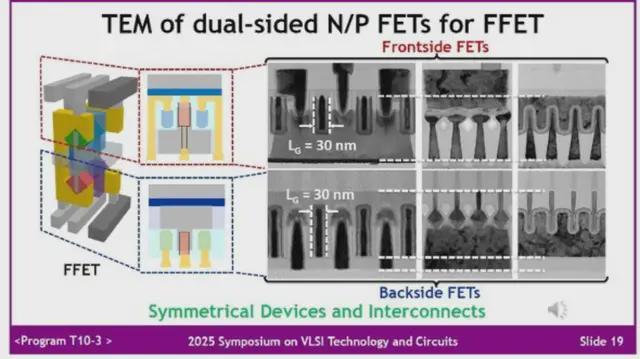

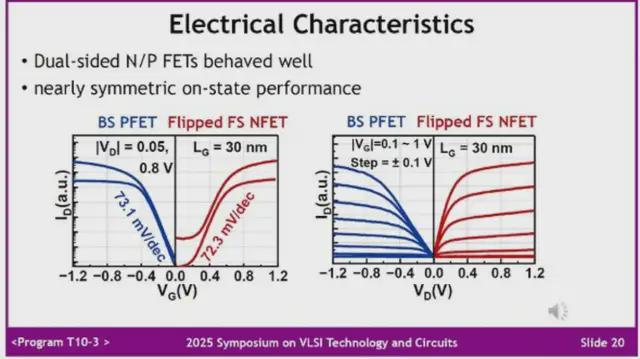

這項技術之所以被稱為“Flip FET”,是因為它包含了鍵合後倒裝晶圓的工藝。實際上,我們利用Flip FET工藝在晶圓正面形成了FinFET NMOS,在背面形成了FinFET PMOS(圖13)。NMOS和PMOS的性能都很好(圖14)。

圖 13:在正面形成 NMOS,在背面形成 PMOS 。來源:VLSI Symposium 2025,T10-3,吳恆(北京大學),幻燈片來自“在 300 毫米晶圓上對倒裝場效應晶體管 (FFET) 中的雙面 N/P FET 進行首次實驗演示,用於亞 1nm 節點的堆疊晶體管技術。”

圖 14 確認 PMOS 和 NMOS 的操作。來源:VLSI Symposium 2025,T10-3,吳恆(北京大學),幻燈片“在 300 毫米晶圓上首次實驗演示倒裝場效應晶體管 (FFET) 中的雙面 N/P FET,用於亞 1 納米節點的堆疊晶體管技術。”

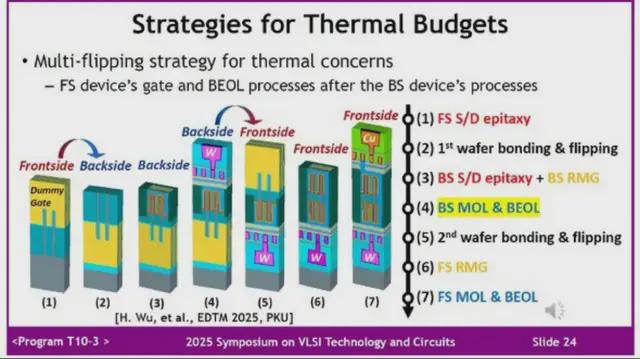

倒裝堆疊晶體管(Flip FET)的應用和未來展望吳恆教授提出了一種在背面形成PMOS和佈線層,然後在正面形成NMOS和佈線層的工藝,以解決Flip FET應用的熱預算問題。在該方法中,晶圓鍵合和倒裝操作進行了兩次(圖15)。

圖 15 在 BS 上創建 PMOS,然後在 FS 上創建 NMOS 的過程[點擊放大] 資料來源:VLSI 研討會 2025 幻燈片,T10-3,吳恆(北京大學),“在 300 毫米晶圓上首次實驗演示倒裝場效應晶體管 (FFET) 中的雙面 N/P 場效應晶體管,用於亞 1 納米節點的堆疊晶體管技術。”

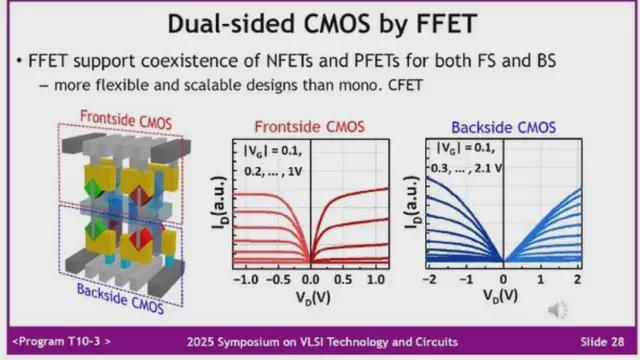

接下來,應用相同的Flip FET工藝,在正面和背面製作CMOS結構,並對其工作特性進行評估(圖16)。吳恆教授課題組在T22-4技術專場做了關於此主題的專題報告。

圖 16 演示使用倒裝 FET 在兩側形成 CMOS 。來源:VLSI Symposium 2025,T10-3,吳恆(北京大學),幻燈片來自“在 300 毫米晶圓上首次實驗演示倒裝 FET(FFET)中的雙面 N/P FET,用於亞 1 納米節點的堆疊晶體管技術。”

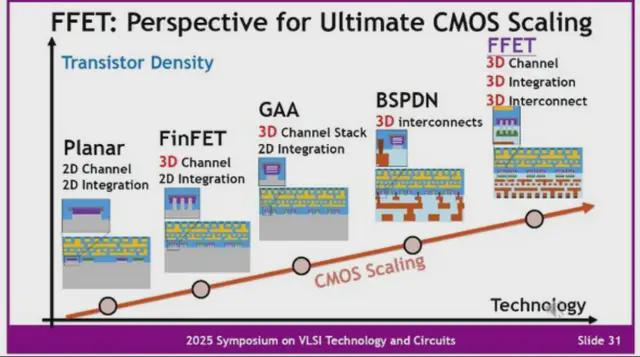

此外,吳恆教授計劃將Flip FET技術應用於亞1納米節點,其路線圖如圖17所示。同課題組的彭萬躍教授在技術分會T22-3上對該路線圖進行了詳細的展示。

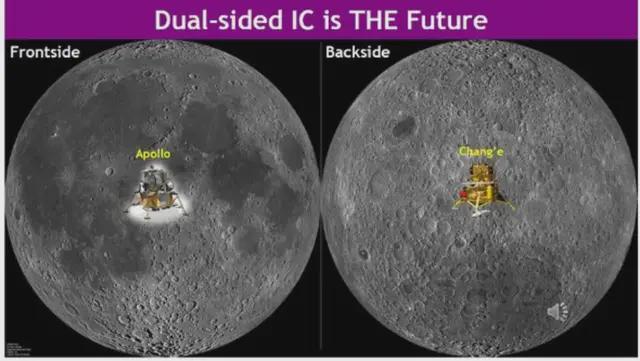

吳恆教授以圖18結束了他的演講。阿波羅計劃將火箭降落在月球正面,但未來或許可以登陸月球背面。同樣地,他總結道,在半導體技術領域,一個集成電路(IC)不僅可以在正面形成,還可以在背面形成的時代即將到來。

圖 17:CMOS 路線圖上的倒裝場效應晶體管 (FFET)。來源:VLSI 研討會 2025,T10-3,吳恆(北京大學),幻燈片來自“在 300 毫米晶圓上首次實驗演示倒裝場效應晶體管 (FFET) 中的雙面 N/P 場效應晶體管,用於亞 1 納米節點的堆疊晶體管技術。”

圖 18 未來將在晶圓的兩面創建 IC。來源:VLSI Symposium 2025,T10-3,吳恆(北京大學),幻燈片來自“在 300 毫米晶圓上首次實驗演示倒裝場效應晶體管 (FFET) 中的雙面 N/P FET,用於亞 1 納米節點的堆疊晶體管技術。”

*聲明:本文系原作者創作。文章內容系其個人觀點,我方轉載僅為分享與討論,不代表我方贊成或認同,如有異議,請聯繫後台。