知合計算:打響高性能RISC-V突圍戰_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。57分钟前

過去幾十年,全球芯片架構的演進經歷了三次關鍵轉折,PC時代x86憑藉封閉生態壟斷市場,移動時代ARM以“公版授權”降低設計門檻廣受歡迎,而在如今的AI與萬物互聯時代,RISC-V以其開源、精簡、可擴展的特性以及低成本優勢成為全球芯片產業變革的新引擎,市場應用與潛力巨大。

經過十幾年發展,RISC-V已在物聯網和嵌入式領域實現了規模化落地。隨着其性能的長足進步,近年來RISC-V逐漸將目光投向AI、數據中心、智能汽車等高性能計算市場。

RISC-V熱鬧背後的“標杆性空白”

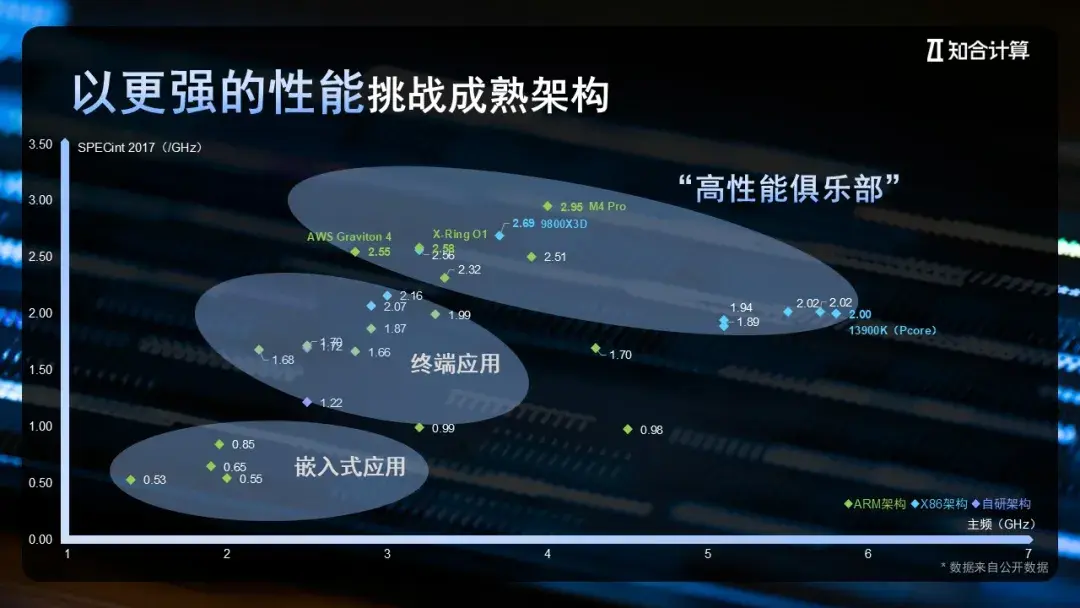

然而,從行業現狀來看,RISC-V在高性能領域的突破呈現一種“雷聲大雨點小”的感覺。儘管近兩年RISC-V在高性能領域的探索熱度攀升,但真正能與ARM、x86抗衡的標杆性產品仍未出現。

當前RISC-V陣營的“第一梯隊”——如SiFive的P870-D、達摩院的C930、開芯院的第三代“香山”處理器核等,相較於ARM與x86架構主流產品,整體性能仍落後一個身位。

“更關鍵的是,國內真正量產的高性能RISC-V芯片產品還未落地”,知合計算CEO孟建熠指出,性能上的滯後,或將引發一系列的連鎖反應。

“硬件是軟件生態的地基,地基不牢,生態自然難穩。”孟建熠解釋道,當RISC-V缺乏高性能標杆產品時,操作系統、商業應用軟件的適配動力會大幅下降——開發者不願為“小眾且性能不足”的架構投入大量資源,導致軟件生態進展緩慢;而軟件的缺失又會讓企業客户對RISC-V持觀望態度,進一步壓縮硬件廠商的商業化空間。

而打破這種惡性循環的關鍵,首先是讓RISC-V在性能上實現追趕。因為只有先在芯片性能上追上主流架構,才能讓軟件開發者和企業客户看到RISC-V的潛力,以標杆產品落地帶動上下游企業聯動,進而驅動生態的正向循環。

從物聯網領域的“輕量級玩家”到高性能計算的“挑戰者”,RISC-V亟待一場關鍵蜕變。這也是知合計算、Tenstorrent、Ventana等RISC-V廠商集中發力的核心目標。

**“通推一體”,知合計算“阿基米德”**亮相RISC-V中國峯會

在上述時代背景和產業趨勢下,2025年7月17日,知合計算在第五屆RISC-V中國峯會上正式公佈了其新一代高性能RISC-V內核的技術進展,併發布“阿基米德”系列通推一體CPU產品。

孟建熠表示,作為最具創新活力的處理器架構,開放的RISC-V正在催生AI原生芯片的無限可能。而在RISC-V深入高性能計算場景的過程中,打造具有更高性能與能效比,並高效融合AI增強計算能力的標杆產品至關重要。

孟建熠表示,作為最具創新活力的處理器架構,開放的RISC-V正在催生AI原生芯片的無限可能。而在RISC-V深入高性能計算場景的過程中,打造具有更高性能與能效比,並高效融合AI增強計算能力的標杆產品至關重要。

為此,知合計算正式提出了“通推一體”架構——通過在架構層面實現通用計算與AI推理計算的高效融合,旨在打造高性能、高能效比的通用計算和高性價比AI推理能力的優勢。

高性能RISC-V CPU核,打造“標杆級產品”

為實現更高性能與能效比的通用計算能力,知合計算公佈了其高性能RISC-V CPU內核的研發進展。

據介紹,該RISC-V CPU核躋身到了高性能CPU第一陣營,能夠媲美ARM和x86最先進的產品性能,達到RISC-V領域的最強性能產品。

除了性能指標強勁以外,該CPU核還有諸多創新點:

除了性能指標強勁以外,該CPU核還有諸多創新點:

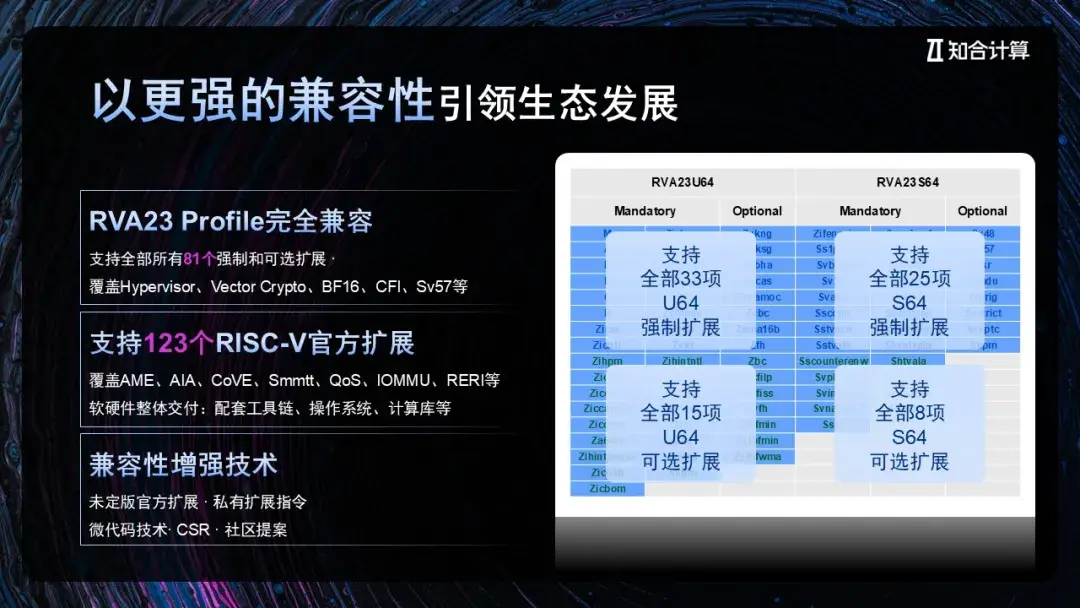

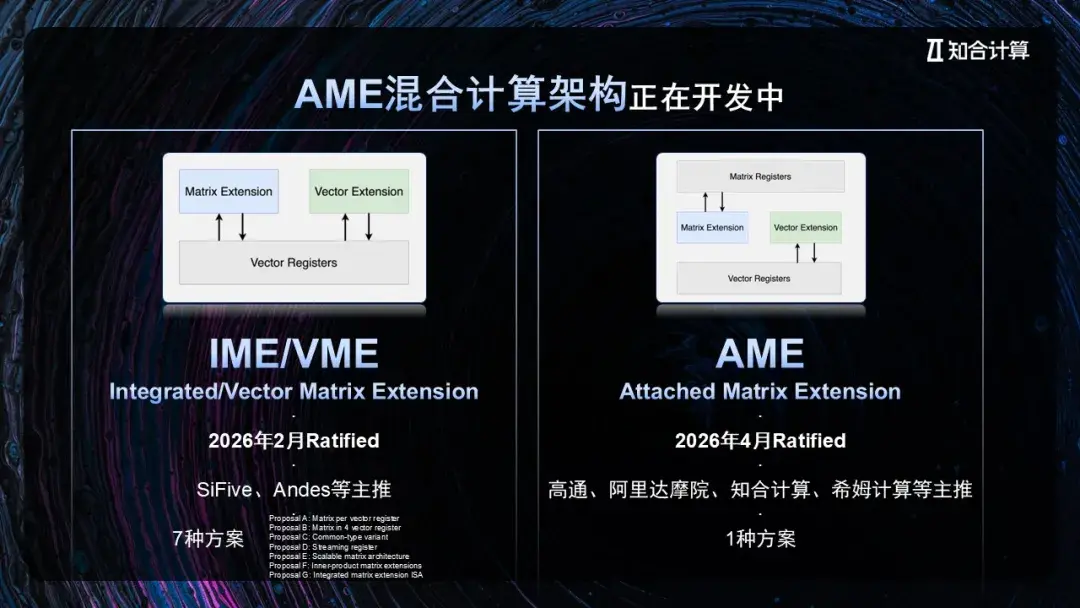

在內核兼容性方面,完全兼容RVA23 Profile,支持全部81項強制和可選擴展,如Hypervisor、Vector Crypto、BF16、CFI、Sv57等;支持123個RISC-V官方擴展,涵蓋AME、AIA、CoVE、Smmtt、QoS、IOMMU、RERI等,以滿足AI計算的新需求。

同時,與其他只關注CPU核本身的產品不同,知合計算的CPU核能提供包括SoC系統和上層軟件的整體支持與交付,為產品設計流程提供適配這些擴展的全套工具鏈、操作系統和計算庫等軟件棧,無需二次開發就能享受到這些新擴展帶來的優勢。

同時,與其他只關注CPU核本身的產品不同,知合計算的CPU核能提供包括SoC系統和上層軟件的整體支持與交付,為產品設計流程提供適配這些擴展的全套工具鏈、操作系統和計算庫等軟件棧,無需二次開發就能享受到這些新擴展帶來的優勢。

其次,對於極少數高性能應用必需但官方規範尚不完善的功能,知合計算將通過聯合產業夥伴向社區貢獻提案,共同促進RISC-V高性能生態繁榮。

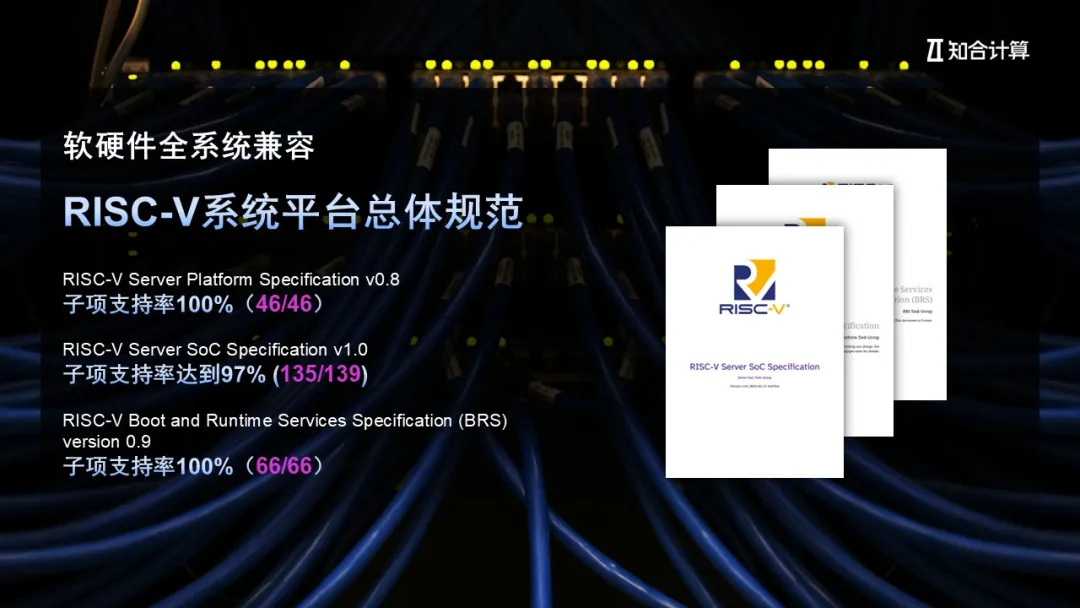

此外,在軟硬件平台系統兼容性方面也頗具優勢。孟建熠指出:“該CPU不僅內核兼容RISC-V官方規範,其SoC平台和上層軟件棧也原生兼容RISC-V系統平台的總體規範。在最新發布的RISC-V Server Platform Specification v0.8版本中,子項支持率達100%,Server SoC Specification v1.0的子項支持率為97%,且軟件棧支持BRS的全部66個子項。”

據透露,該內核現已開放性能評估和軟件適配申請,與之配套的工具鏈、操作系統以及計算庫等均已完成研發設計與適配工作。基於該高性能RISC-V內核的高端處理器產品預計將於2026年正式亮相。

據透露,該內核現已開放性能評估和軟件適配申請,與之配套的工具鏈、操作系統以及計算庫等均已完成研發設計與適配工作。基於該高性能RISC-V內核的高端處理器產品預計將於2026年正式亮相。

從這些數據和優化成果表明,知合計算的高性能RISC-V CPU核已脱離“學術玩具”的標籤,凸顯出其以實際業務需求為導向、以商業化落地為目標的開發邏輯,將成為企業可直接應用部署的成熟解決方案。

知合計算堅信,只有具備更強性能、更強內核兼容性和更完善的軟硬件全系統兼容性的架構才能推動生態繁榮。

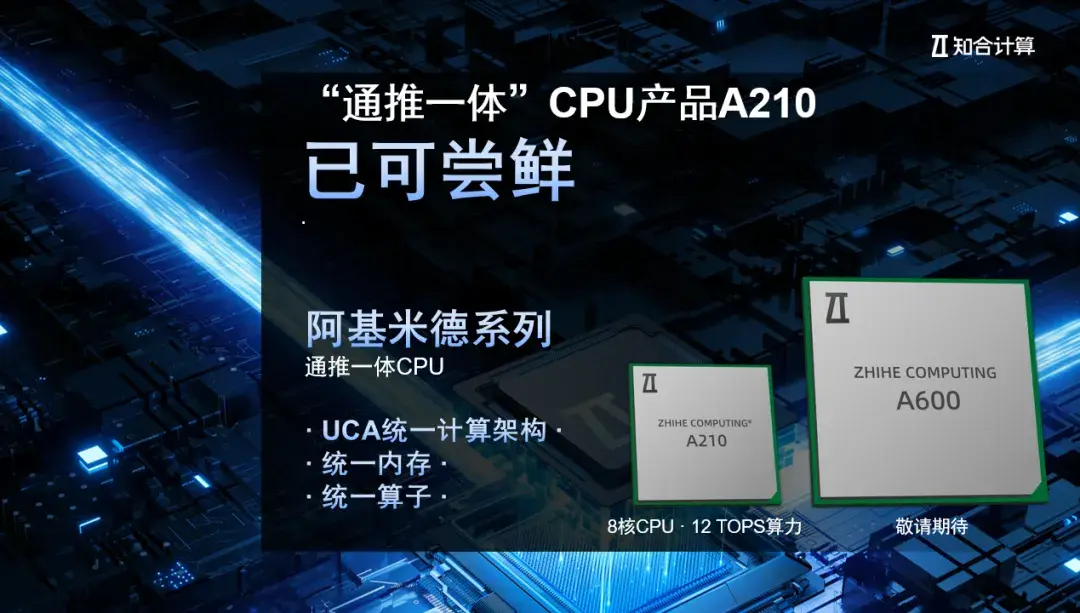

“通推一體”CPU產品A210,已可嚐鮮

此外,知合計算在峯會現場還公佈了其首代通推一體CPU產品“阿基米德”系列,以及阿基米德系列中針對邊緣服務器場景的A210芯片產品。

據瞭解,阿基米德系列創新性採用了UCA統一計算架構,實現了統一內存和統一算子,有助於提高計算效率和性能,為用户提供更強大的計算能力和更優化的使用體驗。“通推一體”架構則實現了SoC層面高性能通用計算和AI推理能力的高效融合,相較於目前業界主流的傳統GPU/GPGPU方案,高性價比成為其核心優勢。該系列首次亮相的A210,則是一款8核CPU,並配備了12 TOPS(INT8)的AI推理算力。

據瞭解,阿基米德系列創新性採用了UCA統一計算架構,實現了統一內存和統一算子,有助於提高計算效率和性能,為用户提供更強大的計算能力和更優化的使用體驗。“通推一體”架構則實現了SoC層面高性能通用計算和AI推理能力的高效融合,相較於目前業界主流的傳統GPU/GPGPU方案,高性價比成為其核心優勢。該系列首次亮相的A210,則是一款8核CPU,並配備了12 TOPS(INT8)的AI推理算力。

孟建熠表示,阿基米德系列在AI推理場景中的高性價比優勢,源於其對不同大模型架構需求的精準適配,以及對傳統方案成本痛點的針對性突破。

當前,基於Transformer架構的傳統大語言模型,因模型參數規模龐大、計算過程中存在大量矩陣運算與特徵交互,對算力密度和內存帶寬提出了極高要求。為滿足這類需求,GPU/GPGPU等並行計算卡普遍採用HBM作為存儲方案。但HBM的技術特性也帶來了顯著弊端:一方面,HBM製造工藝複雜、產能有限,導致其成本居高不下;另一方面,受限於堆疊技術和功耗控制,單顆GPU能搭載的HBM容量通常有限,難以滿足超大規模模型的全量參數加載需求。而若通過“多GPU互連”來擴展內存容量,又會帶來設備間通信開銷增加、算力利用率下降和浪費等新問題。

這種“高帶寬依賴-HBM綁定-成本飆升+容量受限”的鏈條,使得傳統方案在AI推理場景中性價比偏低。

這種矛盾給了RISC-V一個非常好的機會。

與傳統方案不同,知合計算的阿基米德系列選擇傳統CPU中的DDR內存作為存儲方案。儘管DDR的帶寬和傳輸速度低於HBM,但其核心優勢恰好匹配了以DeepSeek為代表的新興MoE架構大模型的需求:MoE架構的核心特點是模型參數規模極大,但實際推理時僅激活部分“專家模塊”,這對內存的“容量”要求遠高於“帶寬”,且單次計算的數據流並不大。此時,DDR內存的“大容量”和“擴容成本低”成為關鍵優勢,既能滿足MoE模型的海量參數存儲需求,又能顯著降低硬件成本。

基於上述場景需求和RISC-V架構的靈活設計,A210芯片無需盲目追求高帶寬和大算力,而是通過內存架構優化與MoE模型的特性適配,在“算力供給-帶寬需求-內存容量”之間找到了更優平衡點,同時避免了效率損耗和冗餘成本。這種按需匹配的設計,能夠實現AI推理場景下的高性價比優勢——以更低成本提供滿足實際需求的推理能力。

當前A210芯片已完成回片和內部測試,即將對開發者、合作伙伴和客户提供樣片測試申請,後續將繼續推進其商業化落地和實際應用場景的部署。

**聚焦“弱生態市場”:**以場景破局推動RISC-V生態落地

據介紹,知合計算的阿基米德系列產品能夠覆蓋從邊緣服務器到雲端服務器的廣泛場景,為包括視頻編解碼、加解密計算、AI大模型推理、數據存儲等豐富的計算應用提供高性能、高能效比、高性價比的算力基礎設施。

知合計算通過針對性優化和增強,使得RISC-V在這些應用場景的相關指標可達到甚至超越業界先進水平,助推RISC-V處理器能夠在高性能計算領域順利落地和應用。

與此同時,知合計算還圍繞總線互聯、多核和QoS等方面進行了顯著優化;安全方面則採用基於CoVE的高性能軟硬件系統安全平台,為產品性能與安全特性提供全新保障。

與此同時,知合計算還圍繞總線互聯、多核和QoS等方面進行了顯著優化;安全方面則採用基於CoVE的高性能軟硬件系統安全平台,為產品性能與安全特性提供全新保障。

不僅如此,其軟硬件SoC全系統原生支持RISC-V CoVE和RAS規範,可提供整體解決方案,並配備豐富的調試與性能分析工具。通過打通軟硬件及前後端開發流程體系,能夠快速評估新擴展、新功能的性能收益和PPA成本,在實現有競爭力頻率指標的同時,還能將面積和功耗控制在優秀水平。

這一系列突破為RISC-V在高性能計算領域的應用築牢了基礎,也為其引領高性能計算軟硬件生態發展注入了強勁動力。

選擇上述四大應用場景作為突破口,背後藴含着知合計算對RISC-V生態建設的深刻考量。

孟建熠向筆者表示:“談及RISC-V的生態建設,軟件層面的短板始終是行業繞不開的挑戰。”面對這一現實,知合計算選擇了一條“避實就虛”的場景化突圍路徑——聚焦對軟件生態依賴度較低的“弱生態市場”率先發力。

以大模型推理場景為例:主流算法的核心算子僅需適配十餘個,例如知合計算的產品已實現對滿血版DeepSeek R1的適配,完成後即可直接應用於DeepSeek一體機,無需大規模投入其他軟件適配工作,與 PC、平板等需要海量軟件支撐的場景形成鮮明對比。

這種策略的核心邏輯在於,通過在特定場景推出成熟可用的標杆產品,先建立市場信心,再逐步吸引下游軟件廠商與產業鏈夥伴主動參與適配。正如知合計算一直踐行的“場景落地-生態完善-更多場景落地”的正向循環。

從行業視角看,這種以場景破局、以標杆產品撬動生態協同的思路,正在為RISC-V軟件生態的漸進式成熟提供切實可行的路徑,也讓外界對其在高性能領域的落地前景更添期待。

**以商業化落地為錨點,**知合計算的差異化突圍之路

RISC-V要真正進入高性能市場,標杆案例的建立是關鍵一步。這一案例不僅要證明技術可行,還要能吸引更多企業和開發者加入生態建設,推動市場接受度和生態成熟。

知合計算此次公佈的高性能RISC-V標杆產品,通過架構創新與場景化適配,在性能、生態和商業化落地等維度實現全面突破,可以視為激活行業生態的關鍵變量。

孟建熠認為,這一案例將不僅是技術的勝利,更是信心的象徵。其核心價值在於通過“標杆引領”打破行業發展瓶頸,重新定義RISC-V的技術上限。

而這種引領作用將觸發滾雪球式的正向循環,當性能可對標ARM、x86的RISC-V產品落地,則將徹底改變外界對RISC-V“僅適用於低性能場景”的認知,吸引更多軟硬件廠商、開發者加入生態建設,最終推動RISC-V進入百花齊放的產業化階段。

這一路徑恰與ARM、x86通過標杆產品構建生態壁壘的成功經驗形成呼應。

唯有更多企業投身高性能RISC-V的技術探索與產品落地,才能推動生態從“概念驗證”走向“規模商用”,讓RISC-V真正具備與傳統架構分庭抗禮的產業競爭力,重構全球CPU產業格局。

在RISC-V高性能計算賽道的激烈競爭中,知合計算雖非最早入局者,卻憑藉對“商業化落地”的極致聚焦,走出了一條“後發先至”的差異化路徑。

知合計算從成立之初便將重心鎖定在產品的實際落地能力上。其團隊在芯片外圍設計、互連技術、緩存優化等底層細節,以及調試工具包、軟硬件交付配套工具鏈等生態支撐環節持續深耕,構建起從CPU核到終端產品的完整技術鏈條。

這種以商業化可行性為標尺的策略,讓知合計算的每一步研發都緊扣“產品可用、生態能接、市場認可”的實際目標,使其技術成果能快速轉化為可落地的產品。對於RISC-V這樣的新興賽道而言,這種“落地優先”的務實路線,或許正是後來者實現彎道超車的關鍵所在。

**RISC-V破局高性能:**生態共生與產業共盛

綜合來看,RISC-V向高性能場景的突破已是大勢所趨。

在知合計算看來,RISC-V的未來走向清晰而關鍵:若能在高性能領域站穩腳跟,將與ARM、x86形成三足鼎立的全球計算架構格局;反之則可能在技術迭代的浪潮中逐漸淡出歷史舞台。

而決定這一走向的核心,就在於能否形成“滾雪球式”的生態正向循環。

作為深耕RISC-V賽道的重要參與者,知合計算將以推動這一正向循環為目標,通過持續打磨高性能標杆產品為生態注入動能,助力RISC-V在高性能計算賽道上實現從“跟跑”到“並跑”乃至“領跑”的跨越。

要實現這一跨越,離不開全行業的協同發力。知合計算強調,標準話語權與生態共建能力是RISC-V向高性能領域突圍的核心關卡,國內廠商要凝聚產業合力,共同探索破局路徑。

孟建熠呼籲:“國內廠商要抱團取暖,以集體力量提升RISC-V國際標準話語權。” 他強調,標準的走向將直接決定技術路線的適配性與生態紅利的分配,唯有深度參與核心標準的制定,才能讓技術規則更貼合本土產業需求,從而真正享受到開源生態帶來的發展紅利。

孟建熠呼籲:“國內廠商要抱團取暖,以集體力量提升RISC-V國際標準話語權。” 他強調,標準的走向將直接決定技術路線的適配性與生態紅利的分配,唯有深度參與核心標準的制定,才能讓技術規則更貼合本土產業需求,從而真正享受到開源生態帶來的發展紅利。

而要實現這一目標,當前國內RISC-V產業的核心命題在於“合作大於競爭”。唯有構建“競合共生”的產業生態,讓技術創新在協同中加速迭代,才能推動RISC-V在高性能領域實現突破性進展,為本土算力產業開闢出一條自主可控的全新路徑。