實現120層堆疊,下一代3D DRAM將問世_風聞

半导体产业纵横-半导体产业纵横官方账号-探索IC产业无限可能。57分钟前

本文由半導體產業縱橫(ID:ICVIEWS)綜合

高密度3D DRAM可能即將到來。

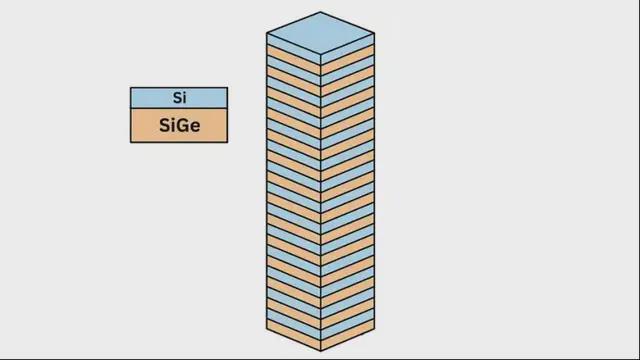

比利時imec(比利時微電子研究中心) 與根特大學(Ghent University) 宣佈,300 毫米硅晶圓上成功外延生長120 層Si / SiGe 疊層結構,為推動3D DRAM的重要突破。

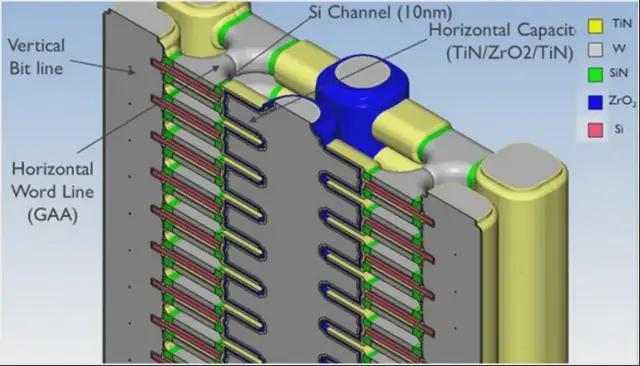

論文發表於《Journal of Applied Physics》。傳統DRAM 製程縮小至10 納米級以下,電容體積不斷縮小,導致電荷保存更困難、漏電問題加劇,業界普遍認為平面微縮已逼近極限。若要滿足AI 與高效能運算(HPC)龐大的存儲需求,未來勢必要藉由“垂直堆疊”提升密度,概念與邏輯芯片的環繞閘極(GAA)類似,3D 結構設計突破既有限制。

雖然HBM(高頻寬存儲)也常稱為3D 存儲,但嚴格來説,屬於芯片堆疊式DRAM :先製造多顆2D DRAM 晶粒,再以 TSV(硅穿孔)互連組合,本質上仍是2D。真正的3D DRAM 是像3D NAND Flash ,單一芯片內直接把存儲單元沿Z 軸方向垂直堆疊。

想象一下,用數百片非常薄、略有不同的材料薄片建造一座塔,每片薄片都會自行彎曲或變形。這正是比利時微電子研究中心(IMEC) 和根特大學的研究人員在 300 毫米晶圓上交替生長 120 層硅 (Si) 和硅鍺 (SiGe) 材料時所取得的成果——這是邁向三維 DRAM 的關鍵一步。乍一看,這聽起來像是在疊紙,但實際上,這更像是用自然會分裂的材料來平衡一座紙牌屋。

過去,由於硅與硅鍺(SiGe)晶格不匹配,一旦層數過多就容易出現缺陷,難以突破數十層瓶頸。這就像試圖堆疊一副牌,其中每一張牌都比第一張稍大——如果不仔細對齊,堆疊就會彎曲並倒塌。用半導體術語來説,這些“倒塌”表現為失配位錯,這些微小的缺陷可能會損害存儲芯片的性能。這次imec 團隊加入碳元素,就像層與層之間塗一層“隱形黏膠”,有效緩解應力(stress),展現穩定性。

為了解決這個問題,團隊精心調整了硅鍺層中的鍺含量,並嘗試添加碳,碳就像一種微妙的膠水,可以緩解應力。他們還在沉積過程中保持了極其均勻的温度,因為反應堆中即使是微小的熱點或冷點也可能導致生長不均勻。

該工藝本身採用先進的外延沉積技術,就像用氣體繪畫一樣。硅烷和鍺烷(含硅和鍺的氣體)在晶圓表面分解,留下精確的納米薄層。控制每層的厚度、成分和均勻性至關重要;即使是微小的偏差也會在整個堆疊中傳播,從而放大缺陷。

那麼,為什麼要付出這麼多努力呢?在傳統的DRAM 中,存儲單元是平面佈局的,這限制了密度。而垂直堆疊(3D)則可以在相同的佔用空間內容納更多的存儲單元,從而在不增大芯片尺寸的情況下提高存儲容量。成功構建 120 個雙層結構表明垂直擴展是可以實現的,這將使我們更接近下一代高密度存儲設備。

想象一下,每一層雙層結構就像摩天大樓的一層,如果其中一層錯位,整棟樓就會變得不穩定。通過控制應變並保持各層結構均勻,研究人員有效地建造了一座由硅和硅鍺組成的納米級摩天大樓,每單位面積可容納數千個存儲單元。

其影響遠不止內存芯片。精確多層結構的生長技術可以推動3D晶體管、堆疊邏輯器件,甚至量子計算架構的發展,在這些架構中,原子級層特性的控制至關重要。三星已經將3D DRAM列入其發展規劃,甚至為此設立了專門的研發機構。

此外,該研究與正在進行的柵極環繞場效應晶體管(GAAFET) 和互補場效應晶體管(CFET) 技術開發工作相一致。這些先進的晶體管架構得益於外延生長技術對材料特性的精確控制,從而能夠製造出更小、更強大的晶體管,這對於電子設備的持續小型化至關重要。

團隊指出,成果證明3D DRAM 材料層級具可行性。應力控制與製程最佳化逐步成熟,將來3D DRAM 有望像3D NAND 走向商用化,使AI 與數據中心容量與能效都更高。

總而言之,這不僅僅是你所知的硅片堆疊;它基於原子張力的工程順序,創造出自然界本身難以產生的結構。對於內存技術而言,正如我們每次談到新突破時所説的那樣,這是一個里程碑,它可能會重塑芯片的設計方式,使其比以往任何時候都更密集、更快、更可靠。

*聲明:本文系原作者創作。文章內容系其個人觀點,我方轉載僅為分享與討論,不代表我方贊成或認同,如有異議,請聯繫後台。