人人都有HPC玩,消費級CPU衝擊100核_風聞

半导体产业纵横-半导体产业纵横官方账号-探索IC产业无限可能。4小时前

“舊時王謝堂前燕,飛入尋常百姓家”。

“舊時王謝堂前燕,飛入尋常百姓家”。

曾幾何時,高性能計算(HPC)專屬的多核處理器還只活躍在服務器領域,如今隨着英特爾最新 CPU 路線圖的曝光,預計接下來幾年英特爾將會有很多充滿競爭力的產品,例如搭載NVIDIA GPU的核顯以及100核的CPU。不過業內人士表示,英偉達和英特爾的合作是美國政府從中撮合,產品協同是不是真能落地還不好説。

百核CPU即將走進消費級市場,一場圍繞“核”的巔峯對決正在英特爾與AMD之間悄然展開。

01

為什麼需要多核?

在計算機發展歷程中,提高處理器主頻曾是提升性能的主要路徑。更高的主頻意味着處理器每秒能完成更多運算,早期電腦性能的飛躍很大程度上依賴於此。然而,這條道路很快遇到了難以逾越的障礙。

首先是熱量與功耗的失控。隨着主頻的提高,處理器產生的熱量和功耗也會顯著增加。高功耗可能導致散熱問題,需要更強大的冷卻系統,而且會增加計算機系統的能耗;其次是性能邊際遞減。當主頻突破 4GHz 後,電子信號的傳輸延遲、晶體管的開關損耗等問題開始凸顯,繼續提升主頻不僅難以帶來明顯的性能增益,還可能因時序紊亂導致系統穩定性下降;最後是製程技術的天花板。隨着晶體管尺寸逼近納米級物理極限,單純依靠縮小製程來支撐更高主頻的難度越來越大,成本也隨之飆升。

相比之下,多核處理器提供了一條更具可持續性的性能提升路徑。通過在單顆芯片內集成多個運算核心,處理器可以並行處理多任務,比如一邊渲染視頻,一邊運行辦公軟件,各核心各司其職,無需再依賴單一核心的高頻“硬撐”。這種架構不僅能顯著提升多任務處理效率,還能在同等性能下降低單位功耗,實現更優的能效比。如今,多核已不再是 “備選方案”,而是適配複雜計算需求(如 AI 推理、4K 視頻剪輯)的必然選擇。

2005年,當時英特爾推出了首款雙核處理器Pentium D,標誌着多核時代的開端。此後,隨着技術的發展,CPU核心數量不斷增加,從雙核到四核、六核、八核,再到如今的多核甚至數十核。這一趨勢的推動因素包括製程工藝的進步、並行計算的需求增長以及市場競爭等因素。

綜合考慮,多核和提高主頻都是提高計算機性能的手段,但多核處理器更符合當前計算需求和技術趨勢。在實際設計中,通常會綜合考慮這兩者以達到最佳的性能和能效比。

02

英特爾的CPU技術路線圖:直指百核

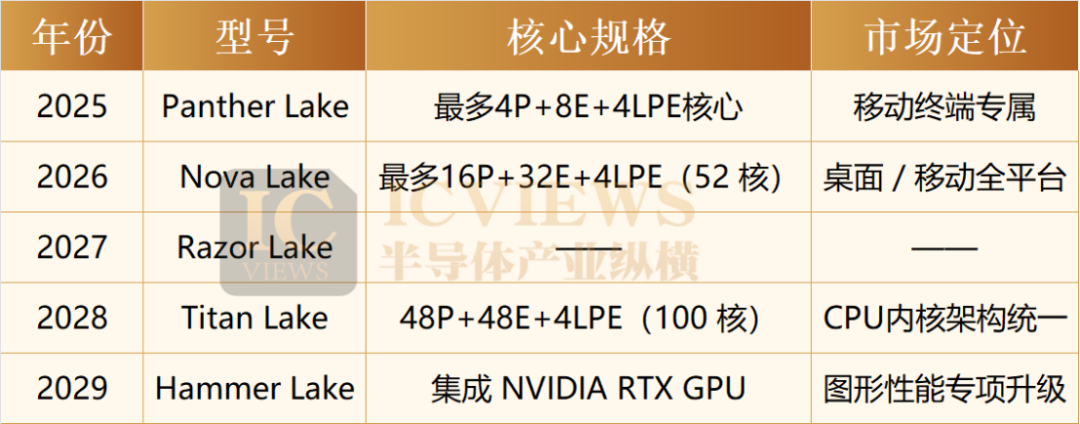

近期曝光的英特爾CPU 技術路線圖,為消費級市場帶來了諸多驚喜,百核 CPU 的出現已不再是遙不可及的夢想。

首先英特爾在今年年末推出Panther Lake處理器,搭載Intel 18A工藝,而這也是英特爾今年最受關注的移動終端,不過不是面向桌面級市場,想要桌面處理器,還是得等到2026年的Nova Lake處理器,包括桌面以及移動平台都將採用該架構,同時相比較Panther Lake處理器,Nova Lake處理器的核心數量暴增,最高可以達到16P+32E+4LPE的規格也就是52核。

首先英特爾在今年年末推出Panther Lake處理器,搭載Intel 18A工藝,而這也是英特爾今年最受關注的移動終端,不過不是面向桌面級市場,想要桌面處理器,還是得等到2026年的Nova Lake處理器,包括桌面以及移動平台都將採用該架構,同時相比較Panther Lake處理器,Nova Lake處理器的核心數量暴增,最高可以達到16P+32E+4LPE的規格也就是52核。

根據路線圖,到了2027年,英特爾將會推出Razor Lake處理器,這將是最後一個採用異構P核和E核設計的CPU。Razer Lake將採用Griffin Cove P核和Golden Eagle E核,在明年發佈的Nova Lake的基礎上小幅提升。

到了2028年推出Titan Lake處理器,最高擁有48P核以及48E核以及4個LPE核,相當於擁有100個核心的龐大規模,此外到了2029年,英特爾與NVIDIA達成的合作就將結出碩果,推出的Hammer Lake處理器或許將採用NVIDIA的RTX GPU,從而在圖形性能上達到新的高度,當然這也就意味着雙方或許要共同研發4年左右的時間。

03

英特爾的“豪賭”:從混合架構的掙扎,到“統一核心”

據瞭解,英特爾可能會在2028年推出Titan Lake處理器系列。屆時可能會完全放棄P核,轉而採用多達100個E核。Titan Lake很可能標誌着英特爾從異構P核和E核配置轉向統一核心架構,該架構可能基於Nova Lake更大的Arctic Wolf E核。

P核(Performance Core)即性能核心,主打高性能表現,擁有更大的緩存、更高的時鐘頻率,支持多線程技術(一個 P 核可同時處理兩個線程),就像處理器中的 “主力干將”,專門負責處理遊戲、CAD 設計、視頻編輯、3D 建模等對性能要求極高的複雜任務。比如在運行 3A 遊戲時,P 核能以高頻率快速處理遊戲中的物理運算、圖形渲染等關鍵數據,確保遊戲畫面流暢運行。但 P 核的短板也很明顯:功耗與發熱量較高。

E 核(Efficiency Core)則以低功耗為核心設計目標,時鐘頻率低於 P 核,功率也較低,不支持超線程,主要負責後台任務(如系統通知、軟件更新、輕度辦公),其作用是為 P 核 “減負”,在保證日常使用流暢度的同時降低整機功耗,並有助於提高P核心的性能和效率。從 Alder Lake 到 Raptor Lake,英特爾的 E 核均基於 Gracemont 架構,能效比已得到市場驗證。

在第 12 代(Alder Lake)、13 代(Raptor Lake)和 14 代(Raptor Lake Refresh)CPU 中,英特爾採用的都是 P 核與 E 核結合的混合架構,E 核基於 Gracemont 微架構設計,該架構是英特爾 Tremont 技術的升級版,在能效比上有顯著提升。

此次轉向統一核心,本質是英特爾對“性能與能效平衡” 的重新考量:一方面,優化後的 Arctic Wolf E 核在單線程性能上已接近前代 P 核,同時保持了更高的能效比與單位面積性能(PPA);另一方面,統一核心架構能簡化硬件設計與軟件調度邏輯,降低研發成本 —— 這對於近年來面臨財務壓力的英特爾而言,是兼顧技術突破與商業效益的關鍵選擇。此外,配合 14A 製程工藝,Titan Lake 的熱設計功耗(TDP)也將得到更好控制,源自Arctic Wolf E核而產生的核心尺寸和功耗增加都可以通過提升PPA來抵消。

04

塞一堆小核心是否可以超越單個大核心

隨着英特爾在消費級市場持續堆核,一個關鍵問題逐漸凸顯:核心數量的增長,是否能等同於實際性能的提升?答案顯然是否定的。

對於天然能利用多核的程序來説,直接堆核心就能有很不錯的收益。但是事實上仍然目前仍有大量軟件(尤其是部分單機遊戲、專業設計工具)未完成多核優化,即便 CPU 擁有數十個核心,實際運行時仍依賴少數核心單打獨鬥,形成“一核苦幹,多核圍觀”的局面。這可能是軟件開發者沒適配,也可能是這類程序涉及到算法天然就不適合多核運算。

而英特爾最新公佈的 SDC(Software Defined Super Cores,軟件定義超級核心)技術,旨在通過軟件與硬件協同的方式,提升CPU單線程性能並優化能效。

這項SDC技術的核心思路,是將兩個或更多的CPU物理核心聯合起來,作為一個高性能虛擬核心協同工作(有點像HPC)。具體來説,就是將單個線程中的指令劃分成多個區塊,分配到不同核心上並行執行。每個核心分別處理程序的某一部分,再通過專用的同步與數據傳輸指令,確保所有操作仍按原始程序順序完成,從而以極低的開銷實現更高的每時鐘指令數(IPC)。這種方法可在不提高時鐘頻率、也不設計更寬、更復雜單體核心的前提下提升單線程性能,避免了更大核心設計帶來的功耗和晶體管數量增加的難題。

此前的P核與E核,其寄存器數量、緩存大小、計算單元配置均為硬件固定,無法根據任務需求靈活調整;而SDC技術通過軟件層面的動態重構,可將多個E核的計算單元與緩存資源“整合”為一個“超級核心”,用於應對單線程密集型任務(如遊戲);也可將資源“拆分”,適配AI數據處理等多線程任務。這種“按需分配”的模式,讓多核CPU的資源利用率大幅提升,從根本上緩解“多核閒置”問題。

AMD的Zen 6架構

面對英特爾的強勢佈局,AMD 也不甘示弱,其即將推出的 Zen 6 架構同樣備受矚目。Zen 6 架構預計將橫跨台積電 3nm 和 2nm 兩代製程工藝,之所以採用這種策略,是因為 Zen 6 架構計劃服役至 2027 年年底或 2028 年年初,期間通過製程工藝的升級,持續提升性能和能效比。

從公佈的數據來看,在核心設計上,Zen 6 架構將繼續沿用經典的 CCD(核心複合體)設計,但單顆 CCD 的最高核心數提升至 12 核,且全部支持雙線程技術。與上一代 Zen 5 架構相比,Zen 6 的 CCD 內核數量增加了 50%,性能提升十分顯著。按照規劃,AMD 將基於 Zen 6 架構推出 24 核 48 線程和 48 核 96 線程的消費級桌面處理器。可以説,多線程已經成為AMD與英特爾的共同角力點。

如今,多核大戰已徹底從服務器領域蔓延至消費級市場,英特爾與 AMD 在核心數量、架構設計、性能優化等方面的激烈角力,最終受益的將是廣大消費者。不久的將來,當我們在組裝電腦、選購筆記本時,數着處理器上密密麻麻的核心數量,享受着百核 CPU 帶來的超強運算體驗,曾經高不可攀的 HPC 技術,終將成為每個人都能輕鬆玩轉的日常工具。

多核大戰,已不再是服務器專屬。如今,英特爾與AMD都在消費級市場瘋狂“堆核”,數框框數到眼花的日子,終於來了。