ASML驅動摩爾定律前行,以全景光刻賦能AI時代半導體創新_風聞

半导体行业观察-半导体行业观察官方账号-专注观察全球半导体最新资讯、技术前沿、发展趋势。3小时前

自1965年戈登·摩爾的預言提出至今,60年來摩爾定律成為集成電路行業進步的圭臬,持續推動集成電路行業創新,讓世界迎來深刻變革。

如今,隨着生成式AI技術爆發,正加速行業從“芯片無處不在”邁向“AI芯片無處不在”,全球半導體行業隨之迎來新的發展浪潮,持續釋放未來潛力。據預測,到2030年全球半導體銷售額將突破1萬億美元。其中數據中心與邊緣AI需求增長尤為顯著,將佔據約40%的市場份額,高性能計算領域的增量空間成為行業增長的重要引擎。

但機遇背後,挑戰也隨之而來。

當前AI算力需求增速已遠超摩爾定律的發展節奏:AI大模型參數呈指數級增長,僅靠芯片晶體管數量/計算能力每2年翻倍的速度,已無法滿足AI大模型訓練的算力需求;與此同時,芯片能效提升速度已放緩至每兩年僅提升約40%。若延續當前趨勢,到2035年訓練一個前沿AI模型所需的電力或將消耗全球總髮電量。

數據來源:斯坦福大學黃漢森(H.S. Philip Wong)教授等人整理分享 圖源:ASML

數據來源:斯坦福大學黃漢森(H.S. Philip Wong)教授等人整理分享 圖源:ASML

算力與功耗的供需缺口,成為AI時代下半導體行業亟待突破的關鍵課題。

**應對AI時代挑戰,**ASML賦能創新突破

面對日益嚴峻的算力與能效挑戰,AI的持續發展亟需在模型效率、芯片技術以及設備與工藝等多維度實現協同創新,推動行業在四大關鍵領域謀求突破:

高效的AI模型:以更少計算資源訓練更多參數的模型;面向AI的高效芯片設計與架構:根據特定的AI需求,推動集成電路系統中的能效提升;高效芯片技術:芯片晶體管微縮和能源優化更高效的集成電路生產設備和工藝在這一創新體系中,光刻技術作為芯片製造的核心環節,其進步對降低單位算力成本與能耗至關重要。

圖源:ASML

圖源:ASML

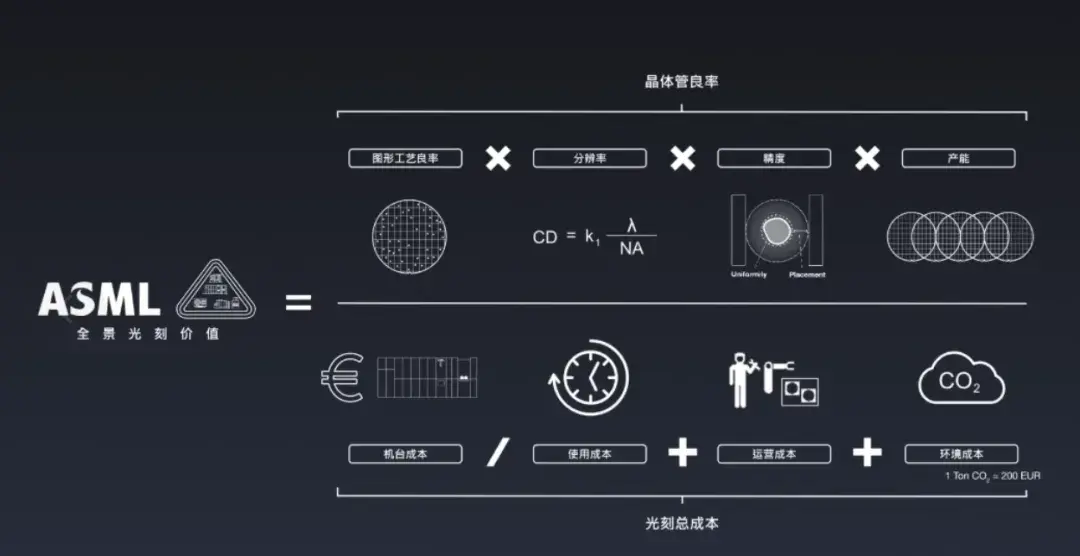

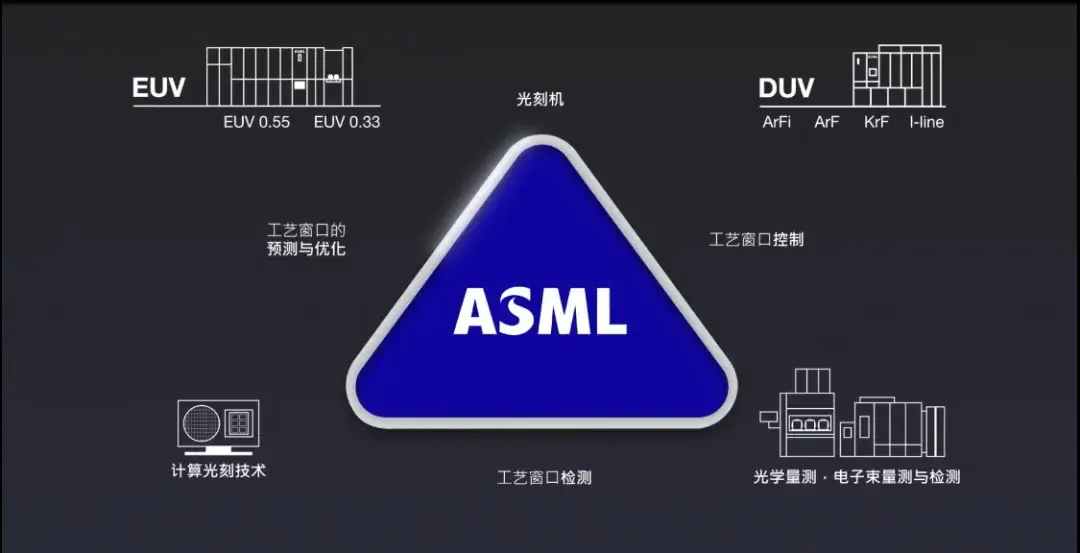

作為半導體制造的核心設備供應商,ASML憑藉其全景光刻解決方案系統性地優化光刻工藝中的各項核心指標——包括良率、分辨率、精度與產能,致力於降低設備在整個生命週期內的使用成本與環境足跡。

整體而言,ASML的全景光刻技術正成為推動芯片技術與工藝改進的核心力量。作為芯片製造突破的關鍵環節,以全流程的效率提升與性能保障,為AI時代的半導體創新提供堅實底座。

在本屆進博會期間,ASML以“積納米之微,成大千世界”為主題,重點展示了其面向主流芯片市場的全景光刻解決方案,融合光刻機、計算光刻和電子束量測與檢測技術。通過數字化、交互式形式呈現這些技術如何協同推動AI時代下摩爾定律的持續演進。

ASML中國區總裁沈波指出,通過2D微縮持續縮小晶體管尺寸、提升晶體管密度與能效,以及藉助3D集成進行堆疊和封裝,突破平面極限,是芯片行業在技術領域尋求創新突破的兩大核心路線。ASML依託集光刻機、計算光刻和光學、電子束量測與檢測技術於一體的全景光刻解決方案,致力於提升性能與能效,以更低能耗和成本實現更高良率。

**推動2D微縮,**EUV加速先進製程落地

其中,為應對AI對芯片算力和能效的極致要求,全球半導體制造商正持續推動芯片尺寸微縮,以在單位面積內集成更多晶體管。從IMEC公佈的技術路線圖來看,先進製程正朝着更小的金屬間距與節點尺寸穩步演進。

圖源:IMEC

圖源:IMEC

能看到,未來15年,芯片製程將從3nm、2nm向A14、A10以及更先進的埃米節點演進,芯片架構也將沿着FinFET、NanoSheet、CFET到2DFET的方向持續迭代,以及金屬間距、互聯架構和供電方式等創新技術隨之快速發展。

在這一進程中,極紫外(EUV)光刻系統作為實現芯片微縮的關鍵工具,已成為多數邏輯與存儲芯片的光刻技術標準。

同時,ASML還在通過持續的光學創新與光刻系統升級,推動EUV技術從0.33 NA向0.55 NA高數值孔徑乃至未來0.75 NA不斷演進,逐步拓寬技術應用窗口。High-NA EUV不僅能顯著提升成像分辨率和對比度,更能將原先需要多重曝光的複雜層次轉為單次曝光完成,從而大幅簡化工藝流程。

ASML通過EUV的可擴展性與技術迭代,不僅能幫助客户實現從“多曝光”到“單曝光”的效率跨越,更在分辨率、生產率、成本控制上形成協同優勢,最終為客户帶來良率提升、週期縮短、綜合成本下降等多重價值。

換言之,EUV技術正為行業構建起一條兼顧性能、效率與可持續性的清晰路徑,持續支撐半導體行業向更小節點、更高性能邁進,助力ASML在AI時代保持領先競爭力。

DUV,光刻領域的“中流砥柱”

然而,值得注意的是,儘管EUV在芯片製造中備受關注,但在整個光刻體系中,成熟的深紫外(DUV)光刻才是真正的主力。當前業界絕大多數的光刻任務,依然由i-line、KrF、ArF、ArFi等DUV光刻技術完成。

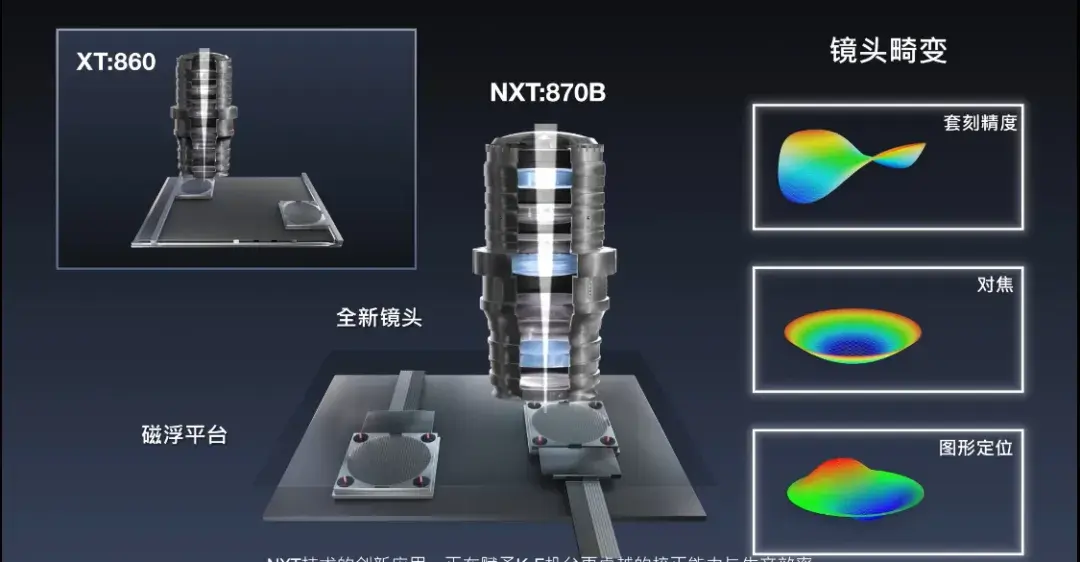

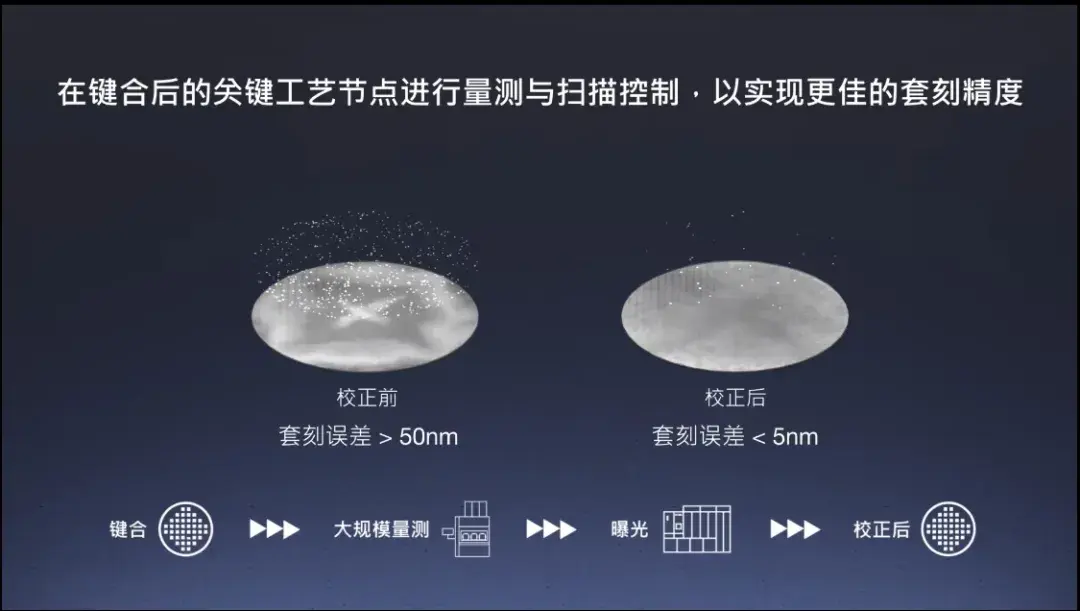

ASML在DUV領域的技術積累同樣深厚,其DUV設備通過持續創新,在生產力、套刻精度與工藝適應性上形成顯著優勢,成為支撐光刻效率與質量的核心力量。以本屆進博會上展示的TWINSCAN NXT:870B光刻系統為例,在升級的光學器件和最新一代磁懸浮平台的支持下,NXT:870B可將晶圓吞吐量提升至≥400 wph的新高度,並通過多方面技術優化實現性能突破,為鍵合後的套刻和階梯式工藝提供強大的校正能力。

圖源:ASML

圖源:ASML

此外,ASML的DUV設備在穩定性與長期可用性上也展現出硬實力。例如,在DUV平台中創新性引入鑽石塗層,能夠有效減少設備磨損並延長使用壽命,大幅降低設備停機校準時間與維護成本,顯著提升產線可用性。

在精度控制與工藝適應性上,ASML DUV設備的校正能力也尤為突出。針對晶圓鍵合前後的形變難題,通過大規模計量技術捕捉晶圓形變特徵,再借助光刻機曝光補償實現局部圖案調整,能夠將鍵合後套刻誤差從50nm量級成功降至5nm以下,部分場景下甚至能降至2.5nm以內,完美適配晶圓-晶圓(W-W)、晶圓-芯片(D-W)混合鍵合的工藝需求,為芯片集成路徑提供重要支持。

能看到,ASML通過持續創新,確保其DUV光刻設備在生產力與工藝控制能力上保持領先。從成熟工藝到封裝鍵合,ASML的DUV光刻設備以“高效、精準、可靠”的核心優勢,為AI時代半導體芯片的規模化、高質量生產提供堅實支撐。

**先進封裝崛起:**ASML攜XT:260光刻機滿足客户需求

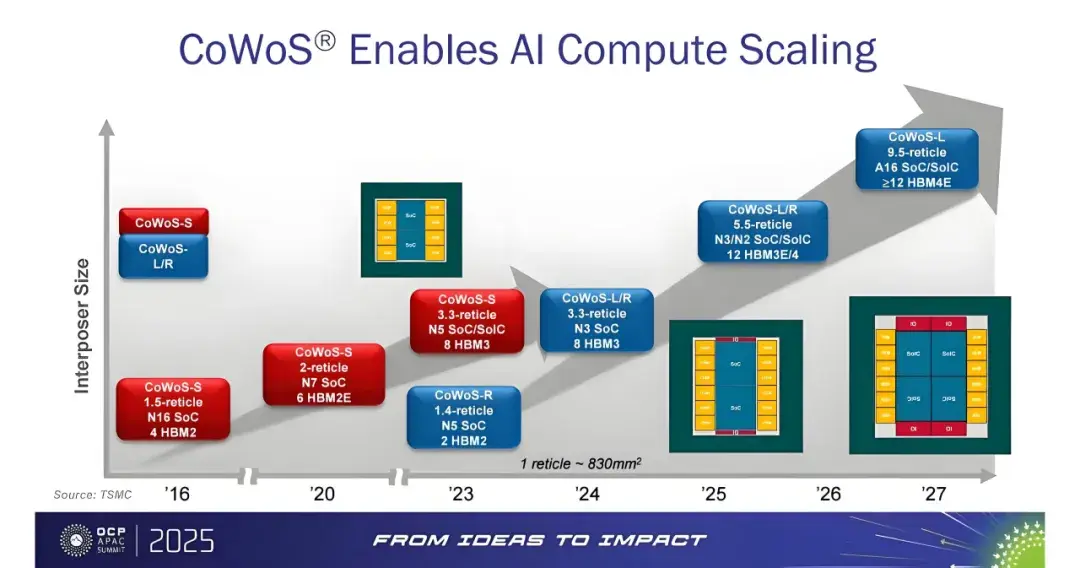

另一邊,在AI芯片強勁需求的推動下,以台積電CoWoS為代表的先進封裝技術正迅速崛起,成為延續算力增長的關鍵路徑。

圖源:TSMC

圖源:TSMC

在這一技術演進過程中,隨着芯片集成度的不斷提升,CoWoS中介層尺寸持續擴大,從早期1倍掩模版逐步升級至3.3倍、5.5倍,未來更將邁向9.5倍掩模版規格。對此,如何在更大尺寸的掩模版上實現高精度、高效率的圖形化製備,成為支撐CoWoS等先進封裝路線落地的核心問題。

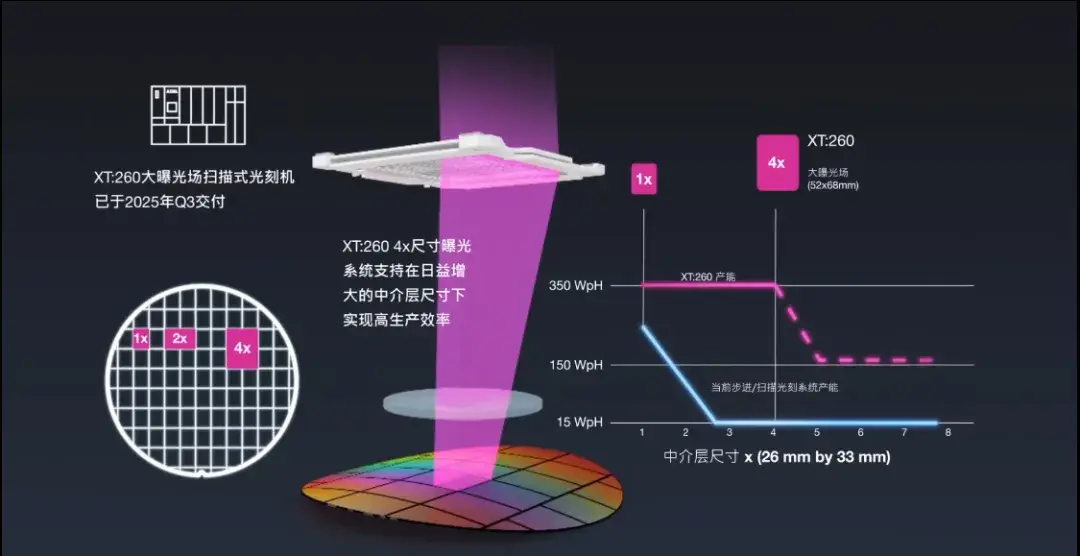

面對行業新挑戰,ASML在最新第三季度財報上披露的TWINSCAN XT:260光刻系統精準切入需求痛點,為先進封裝領域提供支持。

圖源:ASML

圖源:ASML

據介紹,XT:260 i-line光刻機是ASML首款可服務於先進封裝領域的光刻機,基於其獨有的雙工作台技術,通過光學系統的創新,XT:260具有大視場曝光,相較於現有機型可提升4倍生產效率,能夠有效提升先進封裝的效率、性能和良率,並降低單片晶圓成本。除先進封裝外,TWINSCAN XT:260還可支持主流市場的其他廣泛應用,該系統已於今年三季度實現了商業發貨。

從技術價值來看,XT:260延續了ASML DUV技術高效適配場景需求的核心優勢。與EUV技術、其他DUV設備形成協同,共同構建起ASML覆蓋“芯片製造-封裝集成”全流程的光刻解決方案,為AI時代半導體產業鏈的創新提供更全面的技術支撐。

**ASML全景光刻“鐵三角”,**構建良率保障閉環

上文提到,在驅動半導體行業向2D微縮與3D集成邁進的過程中,ASML的價值遠不止於提供EUV與DUV光刻機台,其核心的競爭力更在於構建了覆蓋“光刻機台、計算光刻、電子束量測與檢測”三大支柱的全景光刻(Holistic Lithography)技術體系。

這一“鐵三角”協同的解決方案,正助力全球範圍內芯片製造客户在更小尺寸、更高性能、更智能化的芯片製造中突破瓶頸,實現更高的良率、產能與經濟效益。這一全鏈條協同思路成為ASML應對AI時代挑戰的重要方案。

圖源:ASML

圖源:ASML

其中,作為“鐵三角”的核心技術支撐之一,ASML的計算光刻技術通過先進的仿真與優化手段,能夠預測、校正、優化和驗證光刻技術的成像性能,實現更精確的圖形成像和更好的芯片生產良率。

和計算光刻一樣,量測與檢測也是ASML為保證芯片良率而做的投入之一,即通過光學或電子束手段對曝光後的晶圓進行成像檢查和反饋,及時糾錯/調整光刻工藝即時提升精度與良率,幫助模型進一步優化,為後續的製程開發做好準備。

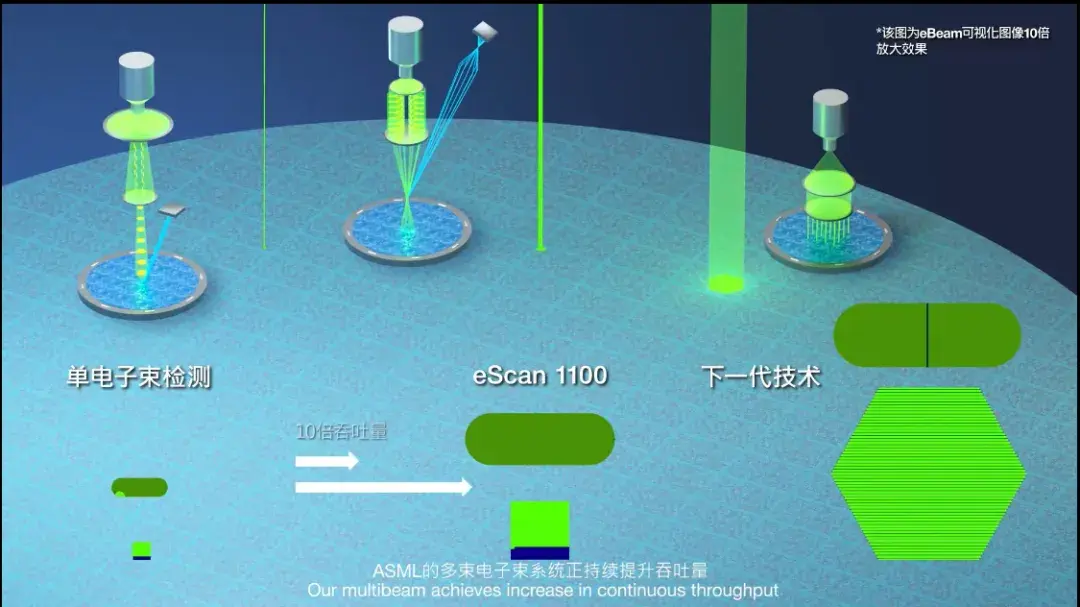

隨着芯片結構日趨立體與複雜,傳統光學檢測已難以捕捉10nm以下的微小物理缺陷,ASML的電子束量檢測技術成為有效解決方案,發揮着不可替代的作用。

同時,針對3D架構芯片中日益複雜的埋藏缺陷與電學缺陷,電子束電壓對比度(VC)檢測技術從NAND領域逐步拓展至DRAM與邏輯芯片,通過電壓信號差異識別埋層結構異常,滿足3D集成對全維度缺陷監控的需求。

在電子束量測與檢測設備方面,ASML也在持續不斷推進創新。eScan 1100作為ASML首款實現在線缺陷檢測(涵蓋物理缺陷和電性缺陷)的25束電子束檢測系統,其晶圓量測吞吐量提升至傳統單束系統的10倍以上。

圖源:ASML

圖源:ASML

該設備在邏輯與DRAM層上的面積吞吐量優勢顯著,可實現單位時間內掃描更多區域,這意味着能捕捉更多缺陷特徵,為客户在從研發到量產爬坡中提供及時監控和反饋,加速良率的提升。

據悉,eScan 1100主要用於電壓對比度檢測。未來,ASML計劃將電子束數量擴展至2700束,進一步釋放量測環節的效率和良率潛力,為未來更嚴苛的製程節點做好準備。

綜合來看,這些技術共同構成了ASML賦能芯片製造與集成的核心能力。光刻系統持續推動2D微縮,同時賦能先進封裝與3D集成;計算光刻突破光學物理極限,智能優化成像;電子束、光學量測與檢測是保障芯片質量的關鍵技術。

與此同時,ASML的全景光刻解決方案還為3D集成的核心鍵合工藝提供堅實支持,幫助減少晶圓形變所導致的對準誤差、保障芯片精準堆疊,並實現更短、更快的互聯,以滿足客户在新興應用領域日益增長的需求。

圖源:ASML

圖源:ASML

**AI時代,**ASML助力摩爾定律煥發新活力

面對AI時代算力需求指數級增長、功耗挑戰加劇、3D集成加速推進的行業變局,ASML以全鏈條協同為核心戰略佈局,依託全景光刻“鐵三角”體系,既在2D縮放領域持續突破物理極限,破解先進節點尺寸縮小難題,又為3D集成提供可信賴、可擴展的整體解決方案,化解鍵合形變、套刻誤差等核心痛點。

展望未來,在AI芯片向更高集成、更復雜架構演進的進程中,ASML早已超越單純的技術提供者身份,成為與全球產業共同探索未來的合作伙伴。其全景光刻,在支撐着全球半導體行業向萬億美元規模邁進的同時,更讓摩爾定律在AI時代持續演進,持續為芯片創新注入動力,成為連接技術極限與AI應用落地的關鍵橋樑。